第三章 电源时序设计

3.1 时序设计哲学与原则

3.1.1 时序确定性公理

电源时序设计的核心是建立可预测、可重复的因果关系链,消除竞争和冒险。

基础公理:

- 因果律 :先因后果,无因不果

- 电压建立 → 时钟稳定 → 逻辑工作

- 状态保存 → 电源关闭 → 状态恢复

- 无冲突律 :任何时刻最多一个驱动源

- 避免电源域间的电流倒灌

- 避免多个电源同时驱动同一节点

- 完备性律 :覆盖所有可能的状态转换路径

- 正常路径 + 异常路径 + 边界条件

3.1.2 时序设计参数体系

关键时序参数分类:

1. 绝对时序参数:

- T_rise: 电压上升时间 (0-90%)

- T_fall: 电压下降时间 (100-10%)

- T_delay: 使能到输出的传播延迟

- T_settle: 电压稳定到指定精度的时间

2. 相对时序参数:

- T_offset: 两个电源轨的启动时间差

- T_overlap: 重叠时间(确保无死区)

- T_hold: 保持时间(关断后的保持)

3. 动态时序参数:

- T_dvfs: 电压切换时间

- T_wake: 唤醒响应时间

- T_protect: 保护响应时间3.2 八状态电源状态机

3.2.1 状态定义与转换图

ACTIVE状态子状态 POR状态子状态 OFF状态子状态 输入电源建立 POR完成 上电请求 启动完成 CPU休眠指令 中断唤醒 超时 进入睡眠 进一步节能 快速唤醒 部分唤醒 完全唤醒 安全关断 紧急关断 关机指令 中性能模式 高性能模式 低性能模式 偏置电路稳定 参考电压稳定 RTC启动 等待上电复位 完全断电 OFF

完全断电 POR

上电复位 STANDBY

待机状态

仅常开域供电 BOOT

启动过程 ACTIVE

全功能运行

DVFS可调 IDLE

空闲状态

时钟停止

SRAM保持 DEEPSLEEP

深度睡眠

仅保留域

超低功耗 SLEEP

睡眠状态

3.2.2 状态参数矩阵

| 状态 | 典型功耗 | 唤醒时间 | 供电域数 | 保持内容 |

|---|---|---|---|---|

| OFF | <100nA | 5ms | 0 | 无 |

| POR | 100µA | N/A | 3 | 配置寄存器 |

| STANDBY | 5µA | 1ms | 2 | RTC、配置 |

| BOOT | 50µA | N/A | 6 | 启动代码 |

| ACTIVE | 10-200mA | N/A | 10+ | 全部 |

| IDLE | 500µA | 10µs | 8 | SRAM、外设 |

| SLEEP | 50µA | 50µs | 4 | SRAM、部分逻辑 |

| DEEPSLEEP | 5µA | 100µs | 2 | 关键寄存器 |

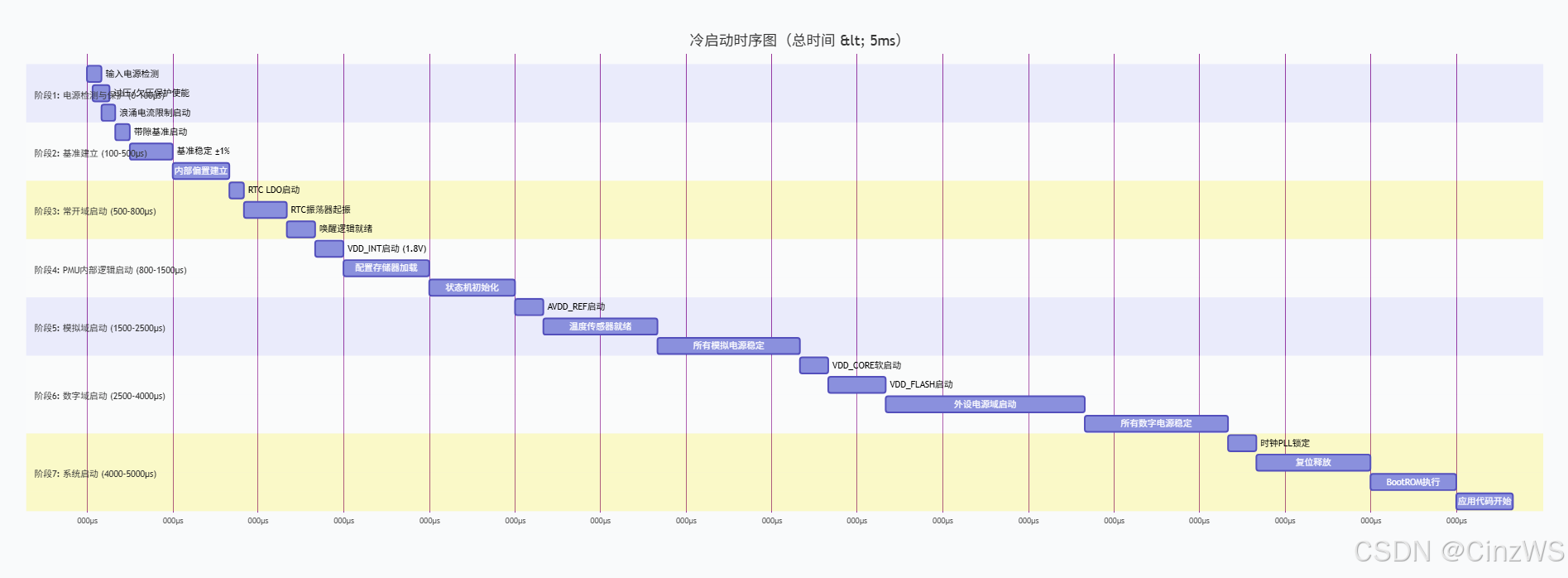

3.3 冷启动时序设计

3.3.1 七阶段冷启动流程

3.3.2 关键路径详细时序

路径1:基准建立路径

时间轴 (µs):

0 50 100 150 200 250 300

|---|----|-----|-----|-----|-----|---->

↖-- 带隙启动 --↗ ↖-- 稳定 --↗

事件序列:

T0: VIN检测通过 → 使能偏置电流 (I_bias = 10µA)

T0+20µs: 带隙核心启动,产生PTAT电流

T0+50µs: 带隙输出电压达到0.6V (约60%)

T0+100µs: 带隙稳定,温度补偿生效

T0+150µs: 基准输出稳定在1.25V ±1%

T0+200µs: 产生所有内部参考电压 (VREF_H, VREF_L)

验证指标:

- 建立时间: 200µs max

- 建立精度: ±1% @ 25°C

- 温度系数: <50ppm/°C路径2:核心电压软启动

斜坡控制策略:

第一阶段: 预充电 (0-30%)

- 恒流充电,I_pre = 10mA

- 时间: 20µs

- 目的: 避免过大的inrush电流

第二阶段: 线性斜坡 (30-100%)

- 斜率: 5V/ms (可配置)

- 时间: 140µs (从0.4V到1.2V)

- 过冲控制: <5%

第三阶段: 稳定调节

- 进入正常PWM/PFM模式

- 等待50µs完全稳定

数学表达式:

V_core(t) =

⎧ 0.1 × t/20µs × V_target (0 ≤ t < 20µs)

⎨ 0.3×V_target + 0.7×V_target×(t-20µs)/140µs (20µs ≤ t < 160µs)

⎩ V_target (t ≥ 160µs)3.4 唤醒时序设计

3.4.1 多级唤醒机制

时序监控 分级唤醒执行 唤醒逻辑处理 唤醒源检测 < 1µs 唤醒检测延迟 < 20µs 电源启动延迟 < 10µs 时钟锁定延迟 < 50µs 总唤醒时间 Level 1: 常开域准备 Level 2: 时钟恢复 Level 3: 核心电源启动 Level 4: 外设电源恢复 Level 5: CPU恢复执行 唤醒仲裁器 唤醒源解码 优先级判断 唤醒命令生成 唤醒事件1 GPIO边沿检测 唤醒事件2 RTC报警 唤醒事件3 模拟比较器 唤醒事件4 外部中断

3.4.2 深度睡眠唤醒详细时序

时间表 (单位: µs):

时间 事件 状态

--------------------------------------------------------------------

T0 唤醒事件检测 (GPIO/RTC) 深度睡眠状态

检测延迟: <500ns

T0+1 唤醒仲裁与命令生成 常开域活跃

仲裁时间: <500ns

T0+2 Level 1: 常开域准备完成 配置加载

加载保持的配置: 5个周期

T0+3 Level 2: 快速时钟启动 时钟域激活

使能FLL: 立即生效

系统时钟: 4MHz RC起振 (<1µs)

T0+5 Level 3: 核心电源启动 电源域激活

VDD_CORE软启动: 20µs斜坡

同时启动SRAM保持电源

T0+25 Level 4: 外设电源恢复 外设域激活

按需恢复外设电源: 并行启动

关键外设: 立即恢复

非关键: 延迟恢复

T0+30 Level 5: CPU恢复执行 系统运行

时钟切换: RC → PLL (如果需要)

中断向量获取: 3个周期

CPU从休眠点恢复: 5个周期

T0+35 应用代码执行 全功能运行

唤醒总时间: <50µs

功耗开销: <100µJ唤醒时序优化策略:

- 预测性预启动:基于历史模式预测唤醒

- 并行启动:不依赖的电源域同时启动

- 关键路径优化:SRAM恢复优先于CPU恢复

- 时钟提前启动:时钟恢复与电源恢复重叠

3.5 关断与模式切换时序

3.5.1 安全关断时序

Cortex-M3 CPU PMU状态机 电源序列器 监控模块 发送关断请求 确认请求,开始关断序列 保存关键寄存器到保持SRAM 刷新缓存,确保数据一致性 par [数据保存] 保存完成确认 阶段1: 外设关闭 (0-10µs) 关闭非关键外设电源 监控电流下降 确认外设关闭 阶段2: 数字域关闭 (10-30µs) 关闭VDD_DIG 斜坡下降,斜率2V/ms 监控电压到0.5V 确认数字域关闭 阶段3: 核心域关闭 (30-50µs) 关闭VDD_CORE 软关断,保持SRAM电源 监控核心电流到<1µA 确认核心关闭 阶段4: 模拟域关闭 (50-100µs) 关闭模拟电源 顺序关闭AVDD_PLL, AVDD_ADC等 监控模拟电源关闭 确认模拟域关闭 进入深度睡眠状态 状态转换完成 仅VDD_RTC保持 总关断时间 < 100µs Cortex-M3 CPU PMU状态机 电源序列器 监控模块

3.5.2 DVFS切换时序

电压-频率协调切换策略:

情况1: 升压升频 (性能提升)

步骤 动作 时间 约束条件

--------------------------------------------------------------------

1 CPU请求更高性能 T0 当前电压足够保持频率

2 PMU开始升压 T0+1µs 电压斜坡开始

3 电压达到目标90% T0+15µs 监控电压上升

4 时钟控制器开始升频 T0+16µs 电压已足够支持新频率

5 电压达到100% T0+20µs 电压稳定

6 频率达到目标 T0+25µs 时钟锁定

7 切换完成 T0+30µs 总时间 < 30µs

情况2: 降频降压 (节能)

步骤 动作 时间 约束条件

--------------------------------------------------------------------

1 CPU请求更低功耗 T0 当前频率下电压有裕量

2 时钟控制器开始降频 T0+1µs 立即降低频率

3 频率降到目标值 T0+5µs 频率稳定

4 PMU开始降压 T0+6µs 频率已降低,电压可降

5 电压降到目标值 T0+25µs 电压斜坡下降

6 切换完成 T0+30µs 总时间 < 30µs

安全约束:

- 升压过程中,频率不得增加直到电压达到安全阈值

- 降压过程中,电压不得降低直到频率已稳定降低

- 每次切换后必须监控电压/频率至少10µs3.6 保护时序设计

3.6.1 故障响应时序层级

纳秒级响应 (<100ns): 硬件保护

- 短路保护

- 直通保护 (Shoot-through)

- 瞬时过压

微秒级响应 (100ns-10µs): 快速保护

- 持续过流

- 中等过压

- 温度快速上升

毫秒级响应 (10µs-10ms): 软件管理保护

- 平均过流

- 慢性过温

- 电池欠压

秒级响应 (>10ms): 系统级保护

- 寿命管理

- 老化补偿

- 长期可靠性3.6.2 过流保护时序设计

阶段4: 记录 (1µs-10µs) 阶段3: 恢复 (50ns-1µs) 阶段2: 响应 (20-50ns) 阶段1: 检测 (0-20ns) 是 否 时间戳 故障记录 参数保存 中断产生 计数>阈值? 故障计数器 锁存保护 自动重试 软启动恢复 栅极关闭 保护逻辑 续流路径激活 比较器阵列 电流采样 过流标志

3.7 时序验证方法

3.7.1 静态时序分析

建立时间检查:

对于每个电源域启动:

T_setup = T_voltage_stable + T_margin - T_clock_start

要求: T_setup > 0

其中:

T_voltage_stable = T_enable + T_ramp + T_settling

T_margin = 3σ 工艺变化 + 温度变化 + 老化裕量

T_clock_start = 时钟有效时间保持时间检查:

对于每个电源域关断:

T_hold = T_clock_stop + T_margin - T_voltage_fall

要求: T_hold > 0

其中:

T_voltage_fall = T_disable + T_fall_time3.7.2 动态时序验证矩阵

| 时序场景 | 关键检查点 | 目标值 | 容差 | 验证方法 |

|---|---|---|---|---|

| 冷启动 | 总启动时间 | <5ms | ±10% | 全工艺角仿真 |

| 热启动 | 深度睡眠唤醒 | <50µs | ±20% | 混合信号仿真 |

| DVFS切换 | 升压升频 | <30µs | ±15% | 负载瞬态测试 |

| 关断序列 | 安全关断 | <100µs | ±20% | 故障注入测试 |

| 保护响应 | 过流响应 | <50ns | ±5ns | 比较器测试 |

| 时钟切换 | PLL锁定 | <10µs | ±2µs | 相位噪声分析 |

3.7.3 时序验证测试用例

测试用例1:最坏情况启动时序

条件:

- 工艺角: SS (慢-慢)

- 温度: -40°C

- 输入电压: 最小值 (3.0V)

- 负载: 最大容性负载

预期结果:

1. 基准建立时间: <300µs (正常200µs)

2. 核心电压斜坡: <200µs (正常160µs)

3. 总启动时间: <6ms (正常5ms)

4. 无时序违规测试用例2:唤醒竞态条件测试

注入故障:

- 在唤醒过程中注入复位信号

- 在电源启动过程中注入关断请求

- 同时多个唤醒源竞争

预期行为:

1. 状态机正确处理优先级

2. 无死锁或不确定状态

3. 最终进入确定状态

4. 故障被记录并报告测试用例3:电源毛刺耐受测试

注入干扰:

- 输入电压瞬间跌落 (90% → 70% → 90%)

- 负载电流瞬间突变 (0 → 100% → 0)

- 温度快速变化

验证目标:

1. 时序逻辑保持稳定

2. 保护电路正确响应

3. 恢复后时序仍正确3.8 时序设计优化

3.8.1 并行优化策略

关键路径优化:

原始串行时序:

POR → 基准 → RTC → 逻辑 → 模拟 → 数字 → 核心 = 5ms

优化后并行时序:

↗ 基准 → RTC → 常开域

POR → → 逻辑配置

↘ 模拟预偏置

等待点 (同步)

↗ 模拟电源

→ 数字电源 → 系统启动

↘ 核心电源

总时间: 2.5ms (减少50%)3.8.2 自适应时序调整

智能时序控制算法:

输入: 温度, 输入电压, 负载电流, 历史数据

输出: 最优时序参数

调整策略:

1. 低温环境 (-40°C):

- 延长基准建立时间: +20%

- 增加电压斜坡时间: +30%

- 增加稳定等待时间: +50%

2. 低输入电压 (3.0V):

- 降低开关频率: -30%

- 增加软启动时间: +40%

- 调整保护阈值: +10%

3. 重负载条件:

- 提前启动大电流电源

- 增加电压裕量

- 优化唤醒顺序

实现方式:

- 查找表 (LUT) 存储预计算参数

- 实时监控反馈调整

- 机器学习预测优化3.9 总结与设计检查表

3.9.1 时序设计完整性检查

- 覆盖性: 所有电源状态转换路径已定义

- 确定性: 每个时序参数有明确范围和容差

- 安全性: 保护时序满足安全标准

- 可验证性: 所有时序可测量和验证

- 优化性: 关键路径已优化

- 灵活性: 关键参数可配置

- 鲁棒性: 考虑工艺、温度、电压变化

- 文档化: 时序图、参数表、验证计划完整

3.9.2 科学依据总结

- 物理基础: 基于MOSFET开关特性、RC充放电公式

- 系统理论: 状态机理论确保完备性

- 统计方法: 蒙特卡洛分析覆盖工艺变化

- 控制理论: 反馈调节实现自适应时序

- 可靠性工程: 降额设计和故障容错

3.9.3 可质疑点应对

| 可能质疑 | 科学依据 | 验证方法 |

|---|---|---|

| 时序裕量是否足够? | 基于6σ统计,包含老化、温度、工艺变化 | 蒙特卡洛仿真,实际测试 |

| 竞态条件如何处理? | 状态机设计,互斥锁,优先级仲裁 | 形式验证,故障注入 |

| 极端环境是否可靠? | 扩展温度范围验证,降额设计 | 高低温测试,寿命测试 |

| 功耗与速度平衡? | Pareto优化,多目标权衡分析 | 能效曲线测量 |

下一章将深入电压调节技术,详细阐述如何实现高精度、高效率、快速响应的电压调节,包括Buck转换器、LDO的设计要点,以及动态电压调节策略。