目录

[I/O 控制方式](#I/O 控制方式)

[题:CPU 微操作与指令执行流程设计](#题:CPU 微操作与指令执行流程设计)

程序的局部性原理

程序的局部性原理是计算机体系结构的核心原理之一 ,是 Cache、虚拟内存等技术的设计基础,指程序在执行过程中,倾向于访问局部范围内的指令和数据 ,具体分为时间局部性 和空间局部性两类。

| 类型 | 核心概念 | 典型场景 |

|---|---|---|

| 时间局部性 | 某条指令或某个数据被访问后,短期内大概率会被再次访问 | 1. 循环语句中的指令(反复执行同一批指令)2. 频繁调用的变量(如循环计数器) |

| 空间局部性 | 某条指令或某个数据被访问后,其相邻地址的指令 / 数据大概率会被访问 | 1. 顺序执行的指令序列(CPU 按地址顺序取指)2. 数组的连续元素访问(数组在内存中连续存储) |

全相联映射的检索过程为:

CPU 访问内存时,先从地址提取主存块号,然后依次与 Cache 中每一行的标记字段比较,若某行标记等于块号且有效位为 1,则命中,用块内偏移量定位字节;若都不匹配或有效位为 0,则未命中,从主存读数据块加载到 Cache 。

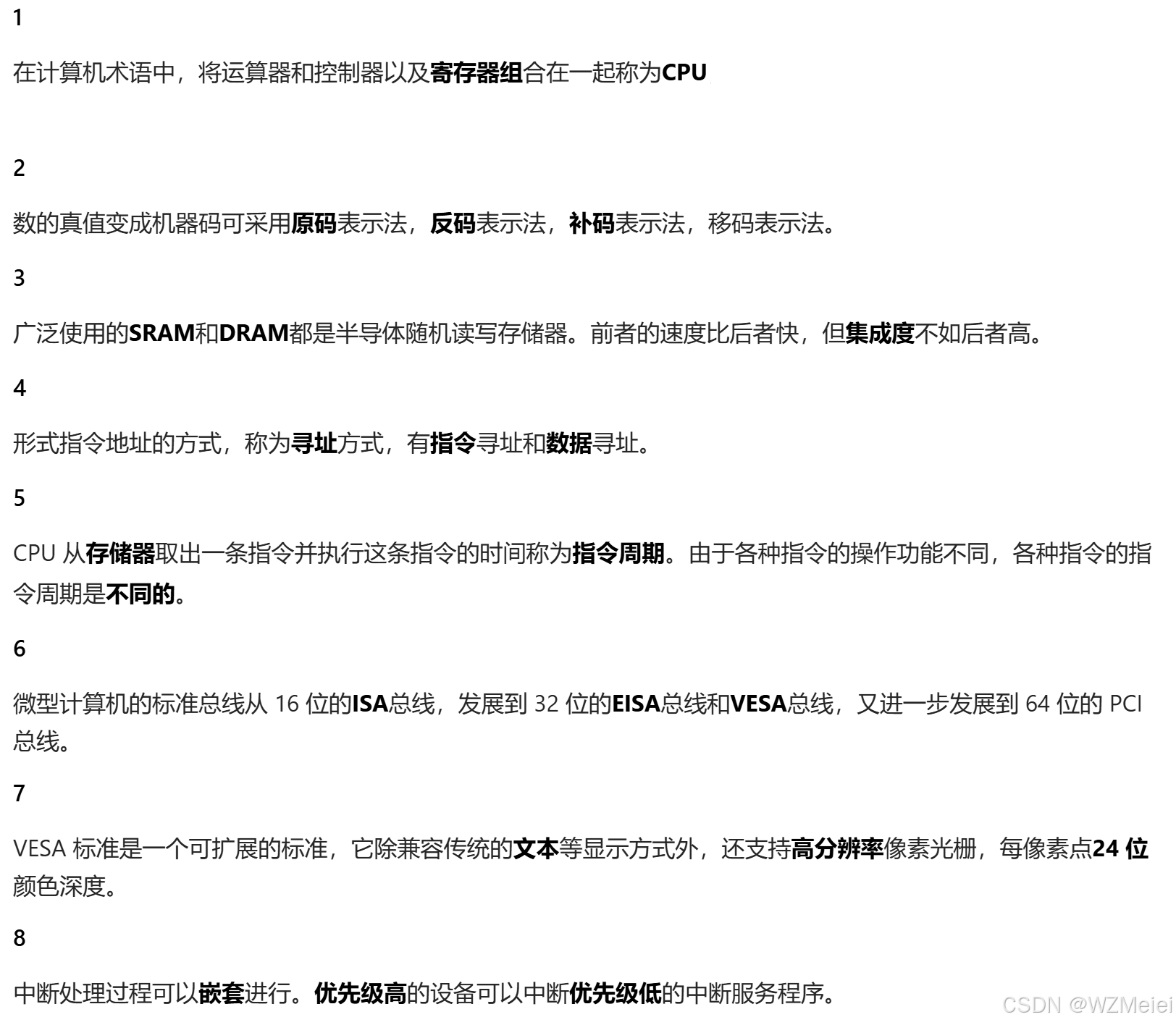

程序中断

程序中断 是指计算机在执行正常程序的过程中,由内部 / 外部事件 触发,暂停当前程序的执行,转而去处理该事件对应的中断服务程序,处理完成后再自动返回原程序断点处继续执行的机制。

中断系统的分类: 描述的是整个中断处理机制的硬件架构和管理能力:

- 单级中断系统:所有中断源只有一个优先级,CPU 只能按 "先来先服务" 的顺序处理,不支持中断嵌套。

- 多级中断系统:中断源被划分成不同优先级,CPU 可以暂停低优先级的中断服务程序,优先处理高优先级的中断,支持中断嵌套。

刷新存储器

刷新存储器(又称帧缓冲器 )是显示系统 的专用高速存储器,用于存储屏幕所有像素的颜色信息,支撑显示器按固定频率读取数据并稳定显示图像。

存储容量的决定因素

存储容量由 屏幕分辨率 和 像素深度 共同决定,

计算公式为:存储容量 = 屏幕分辨率(横向像素数 × 纵向像素数)× 像素深度(bit)

- 分辨率:屏幕像素总数,分辨率越高,容量需求越大;

- 像素深度:存储单个像素颜色信息的二进制位数,位数越多(颜色表现力越强),容量需求越大。

I/O 控制方式

| 方式 | CPU 干预程度 | 速度 | 硬件复杂度 | 适用场景 |

|---|---|---|---|---|

| 程序查询方式 | 完全干预 | 最慢 | 最低 | 低速、少量外设 |

| 程序中断方式 | 部分干预 | 中速 | 中等 | 中高速、需及时响应外设 |

| DMA(直接存储器访问)方式 | 无干预 | 最快 | 最高 | 高速批量数据传送(磁盘) |

| 通道方式 | 极少干预 | 高速 | 很高 | 大型机、多外设并行 |

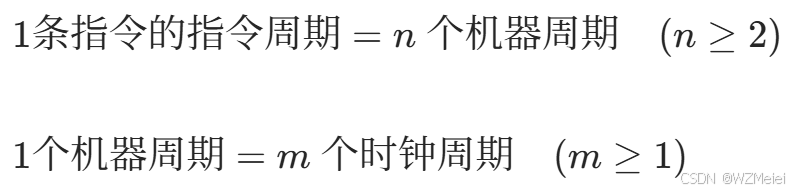

时钟周期,机器周期,指令周期

时钟周期是时间基准,机器周期是基本操作的时间单位,指令周期是一条指令的总执行时间。

-

时钟周期 又称节拍周期 ,是计算机中最基本的时间单位,等于CPU 主频的倒数 (例如主频 2GHz 的 CPU,时钟周期为 0.5ns)。它是 CPU 内部操作(如寄存器传输、ALU 运算)的最小时间刻度,由硬件振荡器的脉冲信号决定。

-

机器周期 又称CPU 周期 ,是 CPU 完成一个基本操作 所需的时间,由若干个时钟周期 组成。不同基本操作的机器周期可能包含 不同数量的时钟周期(例如取指操作、访存操作、运算操作各对应一个机器周期)。机器周期是衡量指令执行步骤的基本单位,常见的机器周期有取指周期、间址周期、执行周期、中断周期。

-

指令周期 是 CPU取出并执行一条指令 所需的全部时间,由若干个机器周期组成。不同指令的指令周期长度不同:

- 简单指令(如寄存器寻址加法指令)可能仅包含取指周期 + 执行周期;

- 复杂指令(如间接寻址访存指令)可能包含取指周期 + 间址周期 + 执行周期;

- 若执行后有中断请求,还会增加中断周期。

指令周期 > 机器周期 > 时钟周期 ,三者是包含与被包含的层级关系:

记忆知识点

-

CPU 与主存交换信息是以字 为单位,CPU 与 Cache 交换信息的单位是块

-

硬盘的磁头可分为固定 磁头和移动磁头

-

CPU 从内存取出一条指令并执行该指令的时间称为指令周期 ;它常用若干个机器周期来表示

-

-127的反码等于0的移码

-

高级语言的编译系统属于系统软件,不是应用程序

-

快速传递进位信号是并行进位实现手段,不是最终目的。

-

多级中断会有中断嵌套 的情况,需要按照**"后进先出"的顺序恢复现场** ,而堆栈的存储方式正好是"后进先出",能高效地依次保存和恢复各级中断的现场信息。

-

冯・诺依曼机按地址 访问存储器,依程序计数器 顺序取指令执行

-

同步控制 是由统一的时钟信号 来控制各个操作的时序,所有部件的动作都按照这个统一时钟的节拍来进行。

-

• A:PCI总线是与处理器无关 的高速外围设备总线。

• B:PCI总线的基本传输机制包含猝发式传送。

• C:PCI设备分为主设备和从设备,不是所有PCI设备都是主设备。

• D:系统中可以有多个PCI总线(比如通过桥接扩展),不是只允许一条。

-

IEEE 754是浮点数的标准格式;尾数影响精度,指数影响范围;浮点数与定点数的表示方式不同。

-

MIPS 受指令集影响,不能单独 作为性能评判依据;CPI越小表示效率越高;吞吐率和响应时间是衡量性能的重要指标。

-

一个汉字 通常占用2个字节或更多 ,而一个英文字符 才占用1个字节。

-

ASCII码 仅能表示英文字符和控制字符,不能表示中文字符。

-

在定点运算器中,内部总线 的主要作用 是连接 各个功能部件并传输 数据

内部总线用于在运算器的不同模块之间传输数据,是数据通路的重要组成部分。

-

定点运算器 通常由加法器、寄存器、逻辑运算单元和移位器等基本部件构成,共同完成算术和逻辑运算。

-

在补码加法 中,当两个同号数相加结果符号与原数相反时,可能发生溢出。而正负相加通常不会导致溢出。

-

多功能ALU可以执行多种算术和逻辑操作 ,通常由多个功能模块组成,并通过控制信号选择所需的操作。

-

多功能ALU 通常由算术运算模块 、逻辑运算模块 、控制模块 和数据通路 组成。

算术运算模块 负责执行加法、减法等操作;

逻辑运算模块 执行与、或、非、异或等逻辑操作;

控制模块 根据指令选择操作类型;

数据通路负责数据的传输和存储。 -

补码加法 中溢出的检测方法 主要有两种:一是双符号位法,二是比较符号位法。

双符号位法 通过检查 结果的两个符号位 是否相同 来判断溢出;

比较符号位法 则通过比较 操作数和结果 的 符号位来判断溢出。这些方法常用于定点运算器的设计中,以确保运算结果的正确性。

-

当I/O设备 需要CPU处理数据时,会向CPU发出中断请求信号。

-

显存大小 = 分辨率 × 每个像素所占字节数

-

微程序控制器 基本组成包括:

1**.控制存储器(CM)** :存放所有指令的微程序(微指令序列);

2.微指令寄存器(μIR) :存放当前执行的微指令,包括操作控制字段 和顺序控制字段 ;

3.微地址形成部件 :根据指令操作码(入口地址)、顺序控制字段、条件码等生成下条微指令地址;

4.微地址寄存器(μMAR):存放将要访问的微指令地址,控制对CM的读操作。

-

微程序控制器 由控制存储器(CM)、微指令寄存器(μIR)、地址转移逻辑等组成。

控制存储器 存放微程序,

微指令寄存器存 放当前微指令,

地址转移逻辑产生下条微指令地址。 -

程序计数器(PC)是指令寻址的部件,不属于 微程序控制器 特有。

-

数据通路的设计 主要关注硬件组件之间的连接 、控制信号的协调 以及数据传输的效率

-

柱面 是由多个磁道组成的,磁道 又由多个扇区构成,扇区是磁盘读写的基本单位 。而一个柱面 并不包含多个盘片,而是多个磁头同时访问的相同半径位置的磁道集合。

-

微程序控制器 通过微指令 实现控制逻辑,具有较高的灵活性,尤其适合复杂指令集的实现。然而,其执行速度不一定比硬连线控制器快。

-

基本的静态存储元(SRAM)通常由6个晶体管 组成,形成两个交叉耦合的反相器,用于稳定地存储一位数据。

-

在SRAM读操作中,当片选信号有效且地址稳定后 ,数据通常会在一个时钟周期后出现在数据总线上。

-

虚拟存储器 由操作系统 负责管理和调度,它扩展了程序可使用的地址空间,但其访问速度 通常低于主存。

-

存储器 的常见分类方式包括按存储介质 (如半导体、磁性材料)、按存取方式 (如随机存取、顺序存取)、按信息保存时间(如易失性、非易失性)。

-

SDRAM 是一种与系统时钟同步工作的DRAM,能够提高数据访问的速度和效率。

-

存取时间 是衡量存储器访问速度的重要指标,它指的是从发出访问请求 到数据可被使用的这段时间。

-

片选信号 :RAS (Row Address Strobe)信号用于激活行 地址,CAS (Column Address Strobe)信号用于激活列地址。

-

访问时间 是衡量存储器性能 的重要指标,通常以**纳秒(ns)**为单位。

-

页表 用于将逻辑地址 中的页号转换为对应的物理地址 中的块号,从而完成地址映射。

-

DRAM存储元 基于电容 工作,需要定期刷新 ,虽然比SRAM慢,但功耗较低,适合大规模存储。

-

存储系统的层次结构 由寄存器 、Cache 、主存 和辅存 组成。

设计目的是通过在不同层次之间平衡速度、容量和成本,提高整体系统的性能和效率。 -

cache存储器 的命中率 是指处理器访问的数据在cache中找到的概率。

命中率越高 ,意味着处理器可以直接从cache获取数据,减少了访问主存的次数,从而提高了系统的整体性能。反之,命中率低会导致更多的主存访问,增加延迟,降低系统效率。

-

DRAM存储元 基于电容的充放电特性 来存储数据。由于电容会逐渐放电 导致数据丢失 ,因此需要定期刷新以维持数据的完整性。

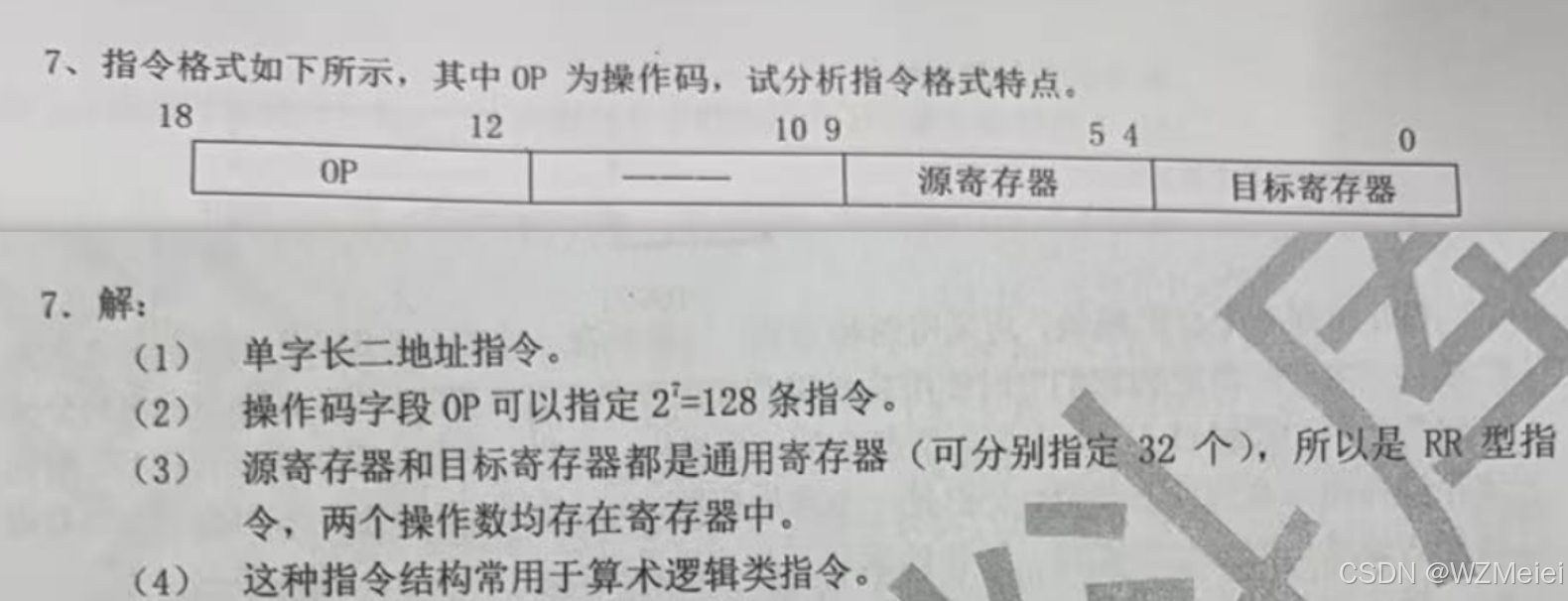

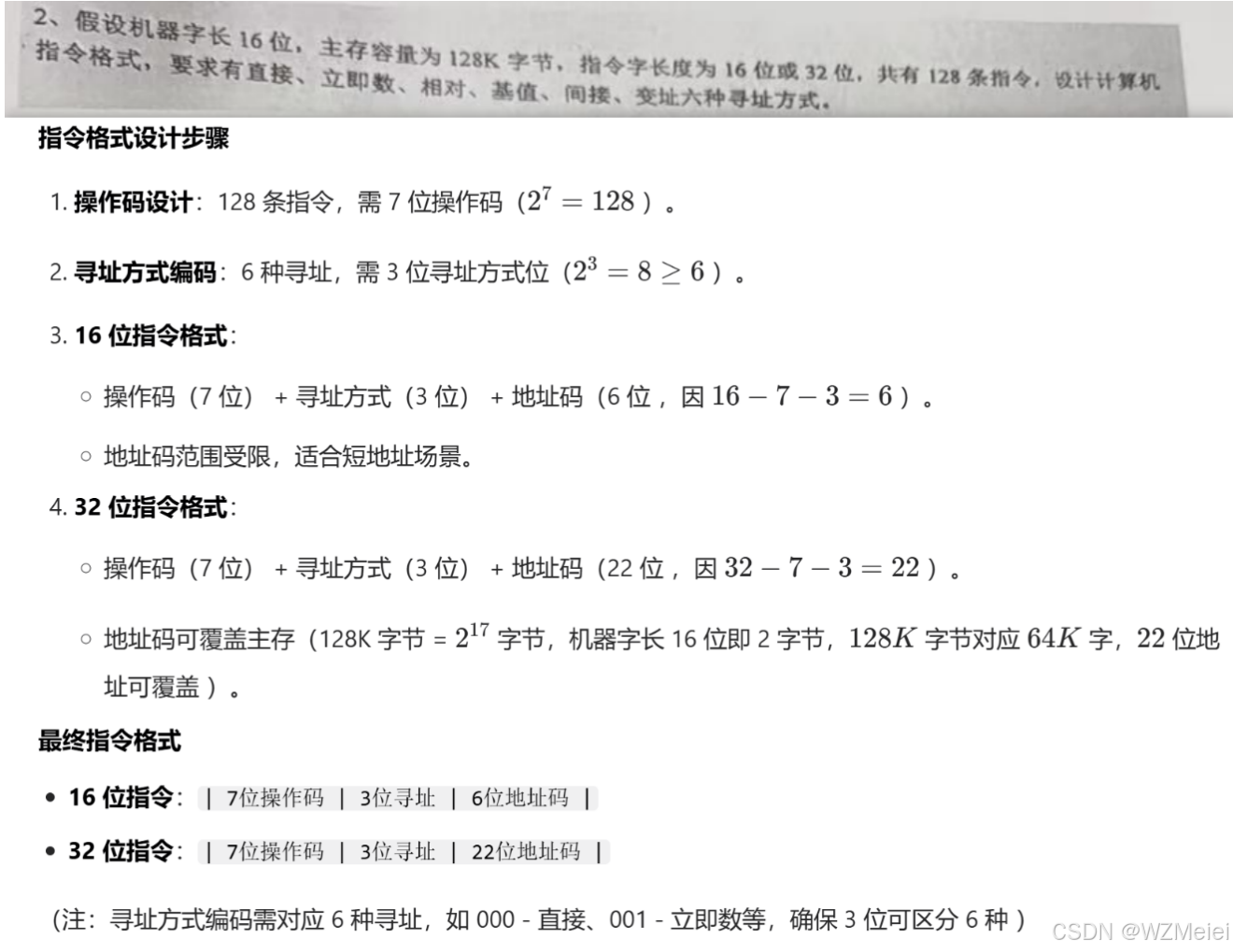

题:指令格式设计

题:扩展存储空间:位扩展

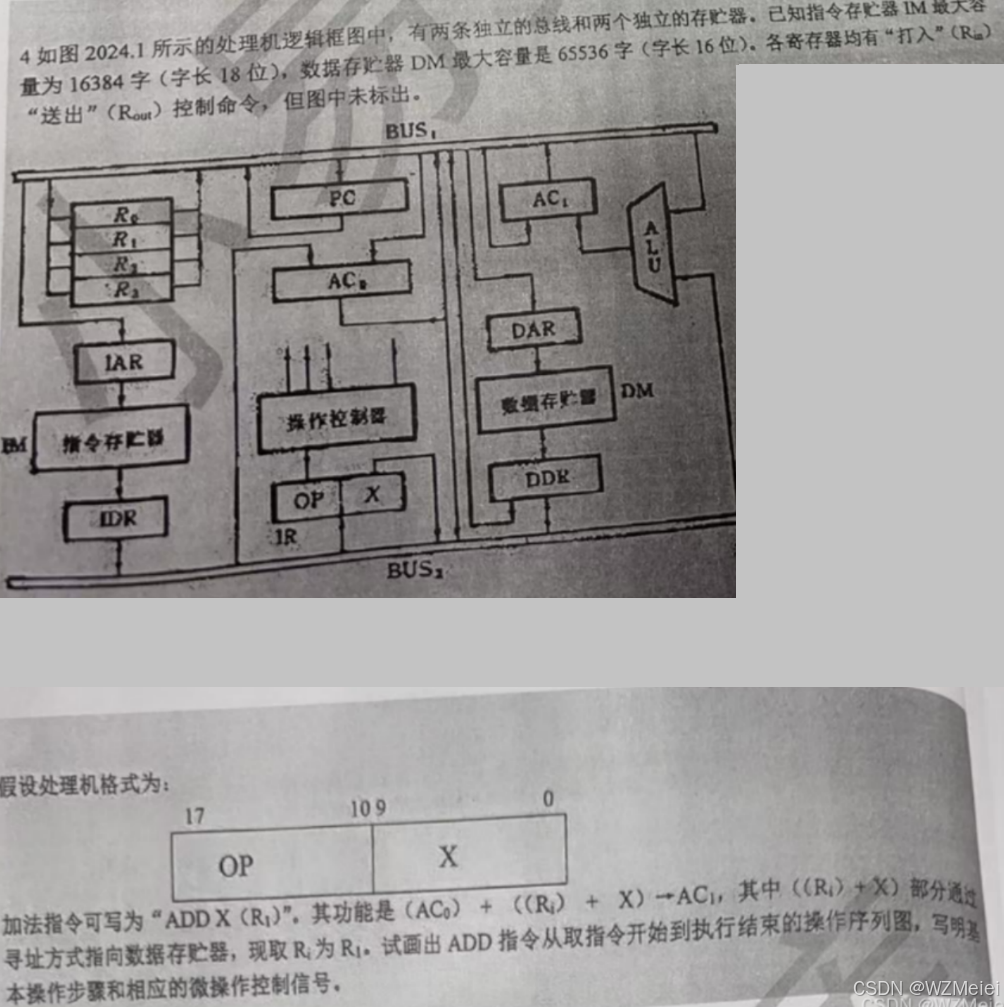

题:CPU 微操作与指令执行流程设计

题:指令格式特点