PSRR 仿真教程, 怎么仿真电路的psrr? [1]两个电路案例,一个是16分频的分频器; [2]一个是250MHz的环形压控振荡器; 仿真方法是用Cadence的psspxf。 PSRR的测量对于改善对噪声源的免疫力很重要; 如电源涟漪由于干扰或系统的数字部分。 同样的方法也被用来测量通过其深层耦合的基底噪声的影响。

在电子电路设计的奇妙世界里,PSRR(Power Supply Rejection Ratio,电源抑制比)如同一位默默守护电路稳定性的卫士,它的性能高低直接影响着电路对噪声源的免疫力。今天,咱们就深入探讨下怎么通过Cadence的psspxf来仿真电路的PSRR,还会结合两个有趣的电路案例,带大家一探究竟。

为什么PSRR测量如此重要

在实际的电路运行中,电源并非理想的纯净能源供应者。电源涟漪可能因为外界干扰,或者系统自身数字部分的"小动作"而产生,这些涟漪就像悄悄潜入电路的捣乱分子,可能会干扰电路的正常工作。而PSRR就像是电路的"盾牌",它能有效抵御这些电源噪声,PSRR越高,电路对电源噪声的抑制能力就越强,工作也就越稳定。同样,通过测量PSRR的方法,我们还能探究通过深层耦合的基底噪声对电路的影响,可谓一举多得。

仿真工具:Cadence的psspxf

Cadence的psspxf是我们此次仿真之旅的得力助手。它提供了强大的功能来模拟电路在不同电源条件下的响应,从而准确计算出PSRR。接下来,咱们结合具体电路案例,看看如何使用它。

案例一:16分频的分频器

- 分频器原理简述:分频器的作用是将输入信号的频率按照一定比例降低,16分频器就是把输入信号频率除以16输出。简单来说,就像是给信号的"脚步"放慢了16倍。

- 使用psspxf进行PSRR仿真步骤:

verilog

// 简单示意16分频器代码

module divide_by_16 (

input wire clk, // 输入时钟信号

input wire rst, // 复位信号

output reg [3:0] q // 4位输出,代表分频后的状态

);

always @(posedge clk or posedge rst) begin

if (rst) begin

q <= 4'b0000; // 复位时,输出清零

end else begin

if (q == 4'd15) begin

q <= 4'b0000; // 当计数到15时,回到0

end else begin

q <= q + 1; // 每次时钟上升沿,计数加1

end

end

end

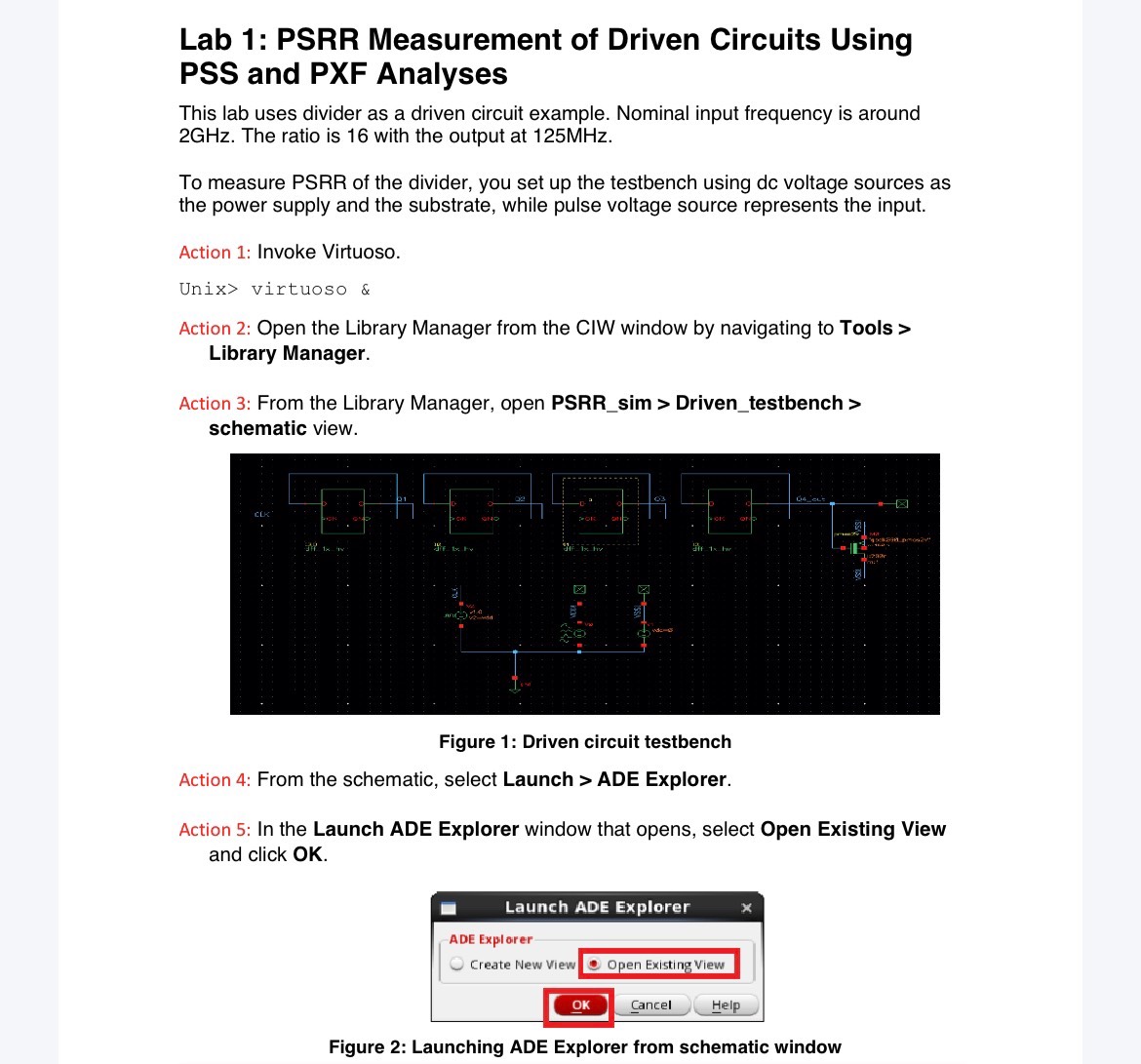

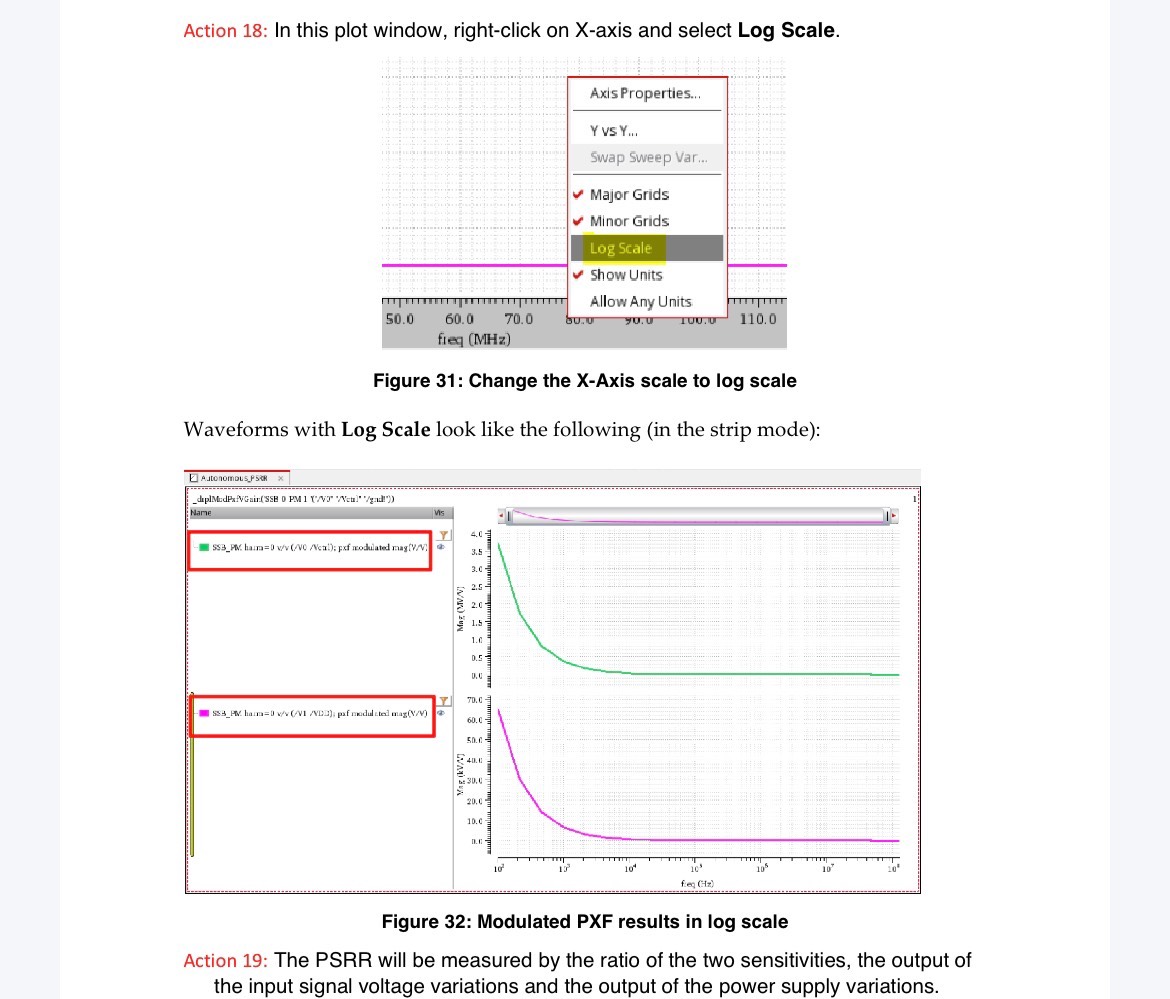

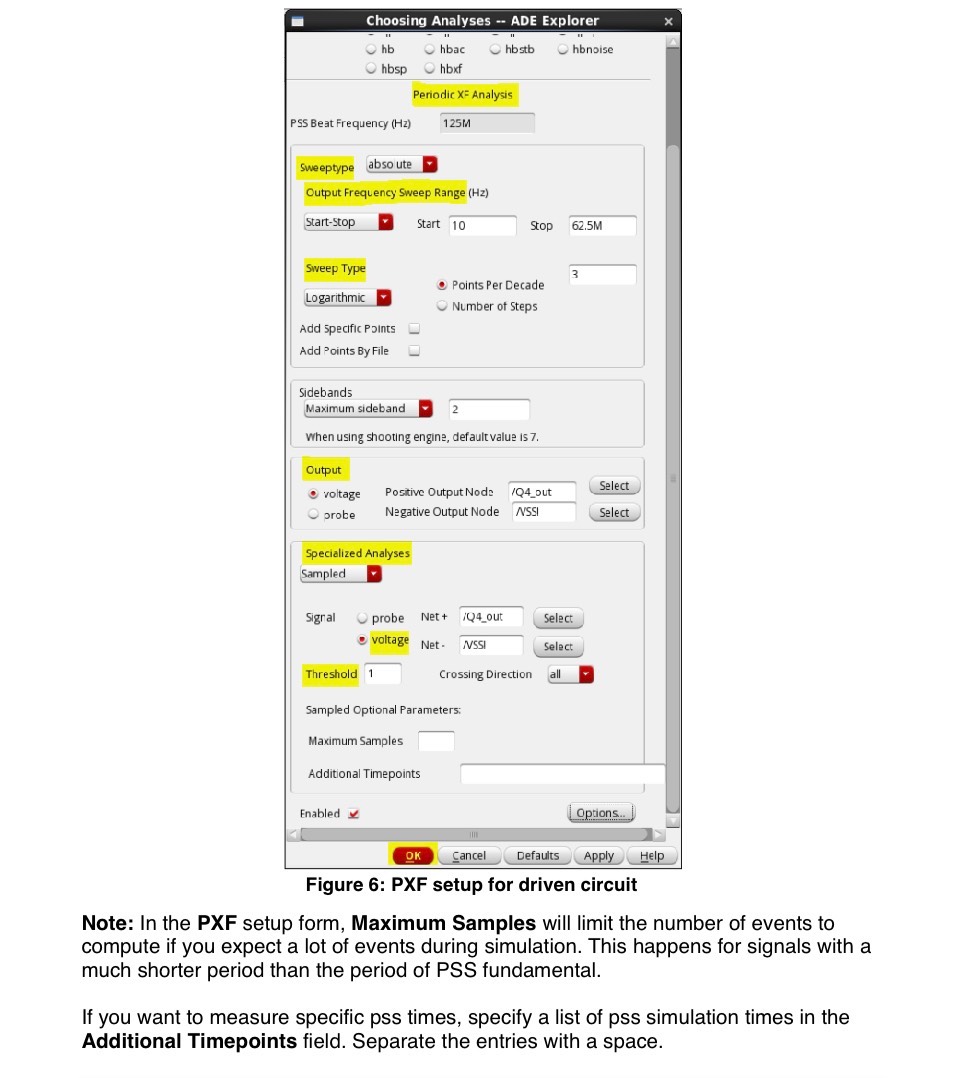

endmodule这段Verilog代码实现了一个简单的16分频器。在使用psspxf仿真时,我们首先要将这个设计导入到Cadence环境中。然后设置电源激励,这里我们可以给电源加上一个小的扰动信号(比如一个正弦波)来模拟实际中的电源涟漪。接着,在psspxf中设置相应的仿真参数,比如仿真时间、采样频率等。通过分析输出信号相对于电源扰动信号的幅度变化,就能计算出该分频器的PSRR。如果输出信号幅度变化很小,那就说明该分频器的PSRR较高,对电源噪声有较好的抑制能力。

案例二:250MHz的环形压控振荡器

- 环形压控振荡器原理:环形压控振荡器(VCO)是一种输出信号频率受输入控制电压影响的电路。在环形VCO中,多个反相器首尾相连形成环形结构,通过改变控制电压可以调整反相器的延迟,从而改变振荡频率。250MHz意味着这个VCO输出信号的频率为250兆赫兹。

- 基于psspxf的PSRR仿真实现:

verilog

// 简单环形VCO示意代码(假设由3个反相器构成)

module ring_vco (

input wire ctrl_volt, // 控制电压输入

output wire clk_out // 输出时钟信号

);

wire [2:0] ring;

assign ring[0] = ~(ctrl_volt & ring[2]);

assign ring[1] = ~ring[0];

assign ring[2] = ~ring[1];

assign clk_out = ring[0];

endmodule这段代码简单构建了一个环形VCO。在使用psspxf仿真其PSRR时,和分频器类似,先将设计导入Cadence。对于VCO,电源噪声不仅会影响输出信号的幅度,还可能导致频率的抖动。同样给电源加上扰动信号后,我们关注输出时钟信号频率和幅度相对于电源扰动的变化。如果频率抖动小,幅度变化也在可接受范围内,说明该VCO的PSRR表现良好,能够有效抑制电源噪声对其性能的影响。

通过这两个案例,相信大家对使用Cadence的psspxf进行电路PSRR仿真有了更清晰的认识。在实际的电路设计中,熟练掌握PSRR仿真方法,能帮助我们打造出更稳定、抗噪能力更强的电路。希望大家在自己的电路设计项目中,都能巧妙运用这些知识,让电路性能更上一层楼!