文章目录

- 说明

- [一 存储器](#一 存储器)

-

- [1.1 内存读写操作](#1.1 内存读写操作)

- [1.2 内存读取事务(三步流程)](#1.2 内存读取事务(三步流程))

- [1.3 内存写入事务(三步流程)](#1.3 内存写入事务(三步流程))

- [1.4 RAM:主存储器的基本组成单元](#1.4 RAM:主存储器的基本组成单元)

- [1.5 SRAM 与 DRAM 综合对比](#1.5 SRAM 与 DRAM 综合对比)

- [1.6 增强型DRAM技术](#1.6 增强型DRAM技术)

- [1.7 DRAM组织结构](#1.7 DRAM组织结构)

- [1.8 读取DRAM超单元(2,1)过程](#1.8 读取DRAM超单元(2,1)过程)

- [1.9 内存模块设计](#1.9 内存模块设计)

- [二 局部性原理](#二 局部性原理)

- [三 存储器层次结构](#三 存储器层次结构)

-

- [3.1 存储器的层次结构](#3.1 存储器的层次结构)

- [3.2 缓存基本概念](#3.2 缓存基本概念)

- [3.3 缓存未命中的类型](#3.3 缓存未命中的类型)

说明

- 庄老师的课堂,如春风拂面,启迪心智。然学生愚钝,于课上未能尽领其妙,心中常怀惭愧。

- 幸有课件为引,得以于课后静心求索。勤能补拙,笨鸟先飞,一番沉浸钻研,方窥见知识殿堂之幽深与壮美,竟觉趣味盎然。

- 今将此间心得与笔记整理成篇,公之于众,权作抛砖引玉。诚盼诸位学友不吝赐教,一同切磋琢磨,于学海中结伴同行。

- 资料地址:computing-system-security

一 存储器

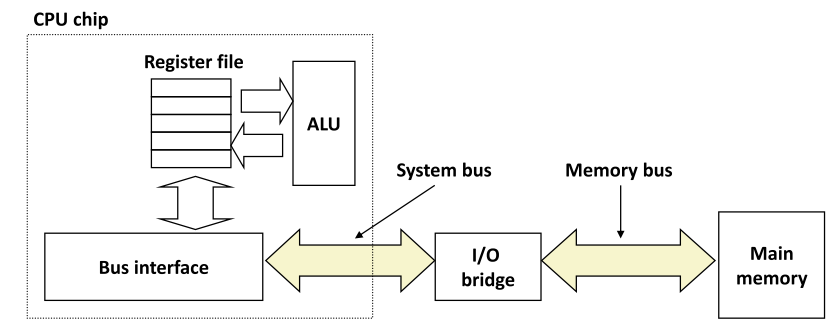

1.1 内存读写操作

- 写操作(Store):将数据从CPU传输到内存。示例指令:

movq %rax, 8(%rsp) - 读操作(Load):将数据从内存传输到CPU。示例指令:

movq 8(%rsp), %rax - 总线:一组并行导线,用于传输地址、数据和控制信号,多个设备共享总线资源。

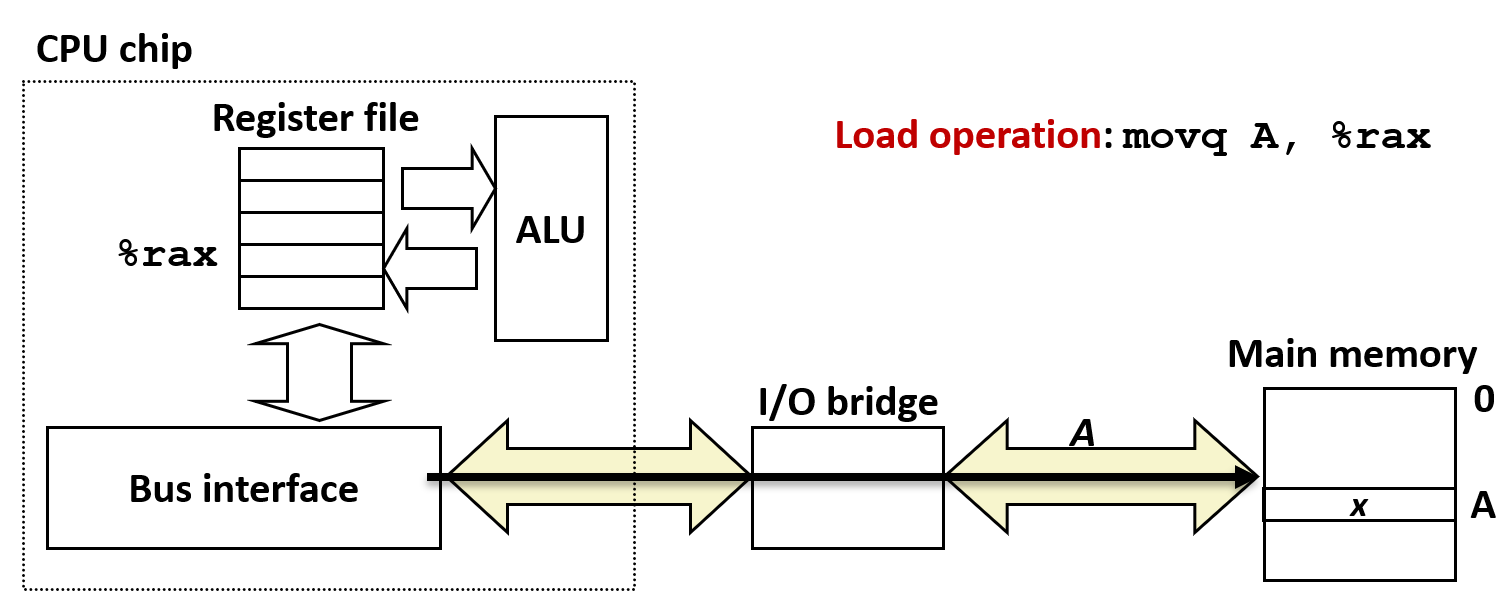

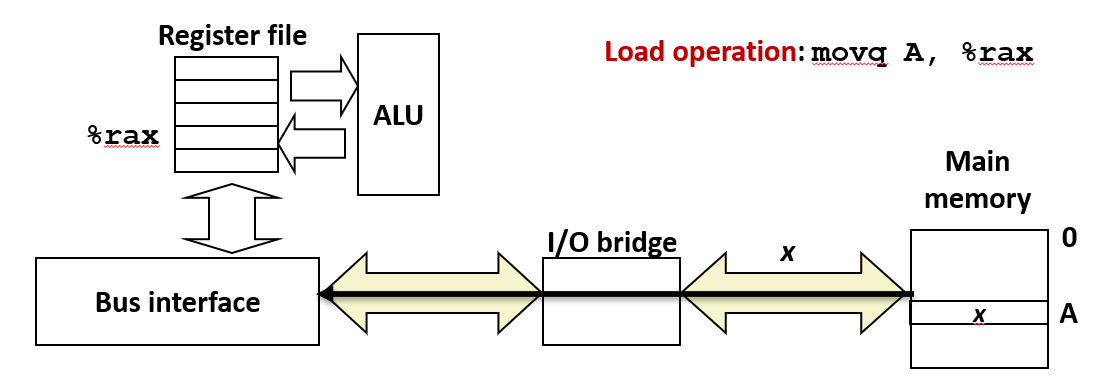

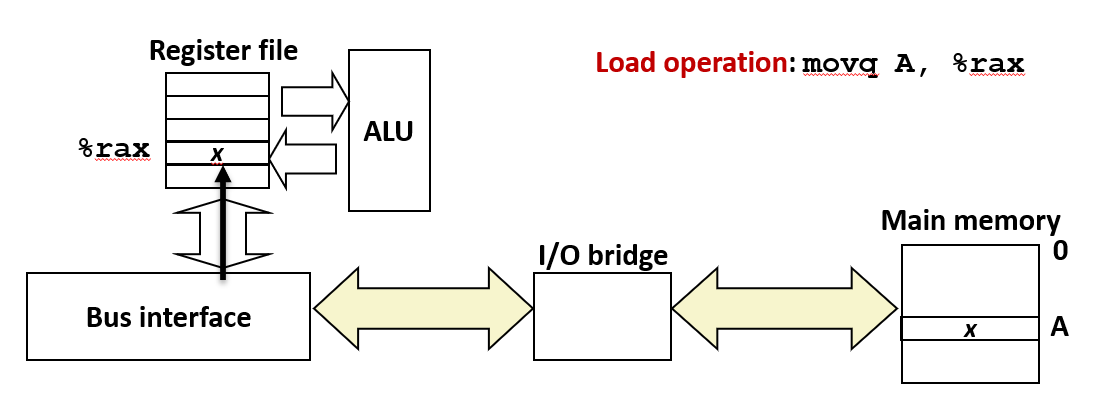

1.2 内存读取事务(三步流程)

步骤1:发送地址

- CPU将地址A放置在内存总线上

- 请求加载操作:

movq A, %rax

步骤2:主存响应

- 主存读取地址A,获取对应字x,并将其放回总线

步骤3:CPU接收数据

- CPU从总线读取字x,并复制到寄存器%rax中

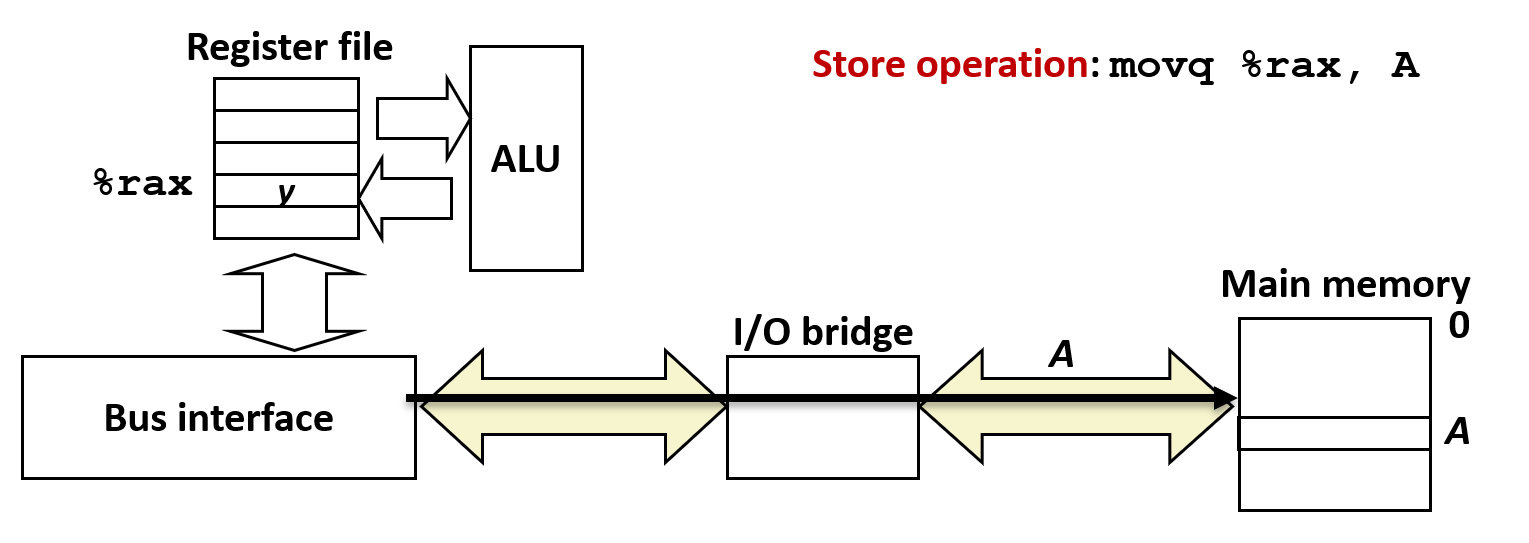

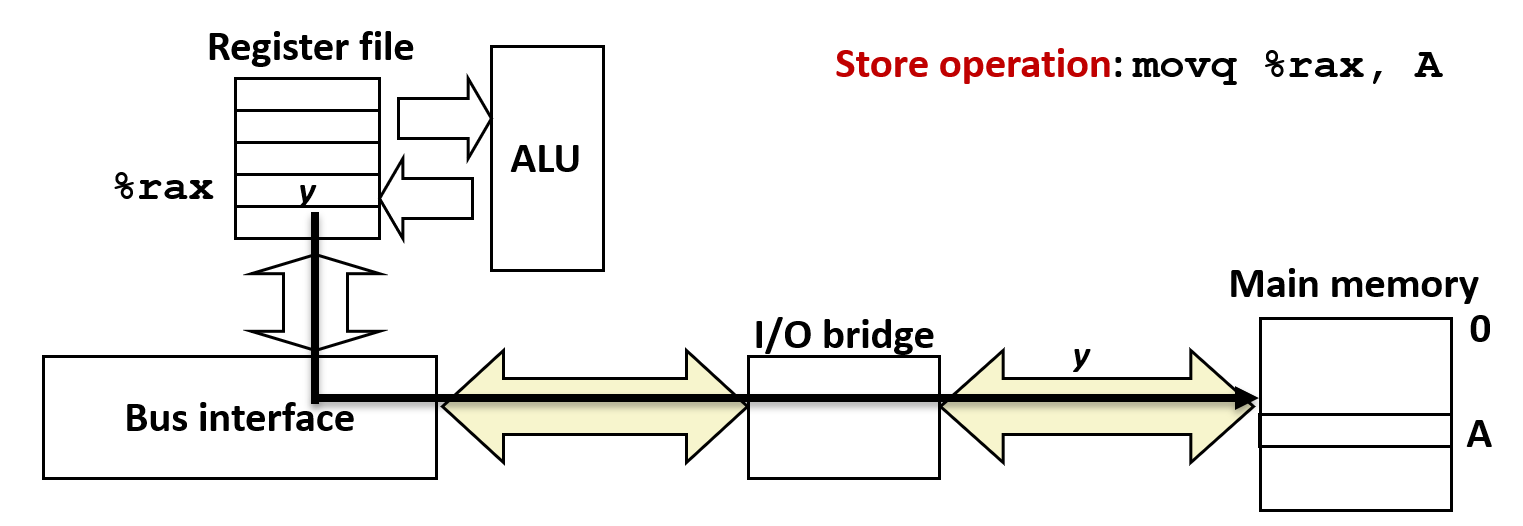

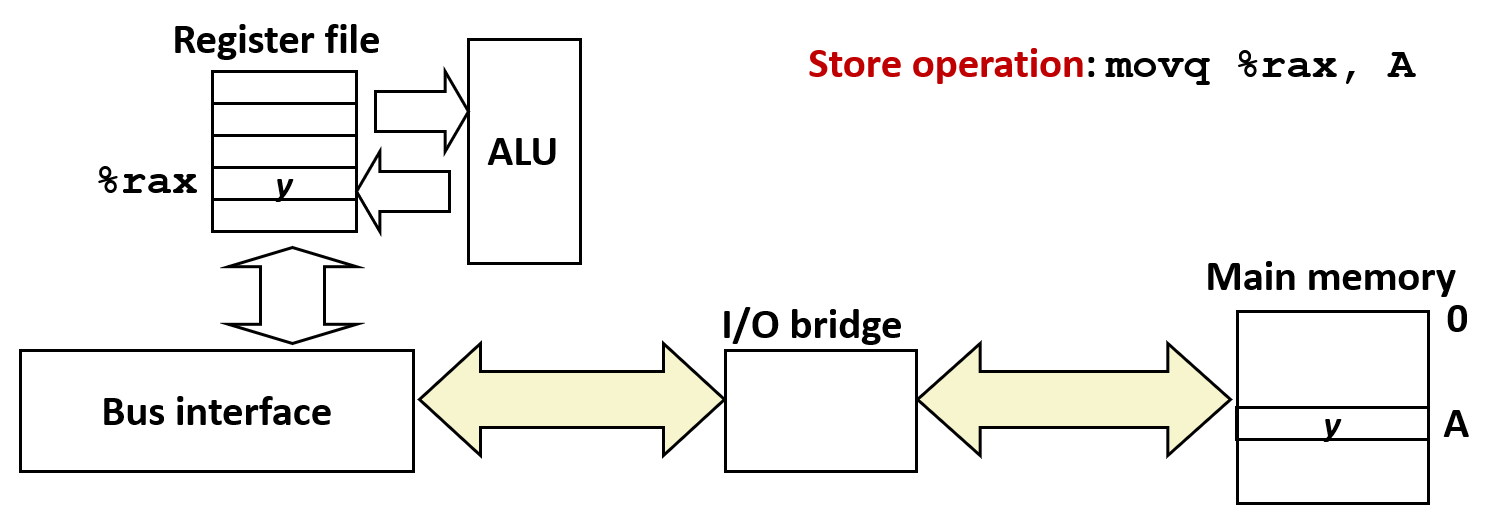

1.3 内存写入事务(三步流程)

步骤1:发送地址

- CPU将地址A放置在总线上

- 主存接收地址并等待数据到达

步骤2:发送数据

- CPU将数据字y放置在总线上

步骤3:主存存储数据

- 主存从总线读取数据字y,并将其存储在地址A处

1.4 RAM:主存储器的基本组成单元

- 随机存取存储器(RAM)扮演着至关重要的角色,它是系统运行时数据和指令暂存的核心场所。RAM 通常以独立芯片形式存在,或集成于现代处理器内部,其基本存储单元为 1 位(bit),多个 RAM 芯片共同构成完整的内存系统。

- RAM 主要分为两大类,它们在结构、性能与应用场景上各有特点:

- SRAM(静态 RAM)

- 使用 6 个晶体管构成一个存储单元(也有 8 晶体管版本用于特定设计)。

- 数据在通电状态下可无限保持,无需刷新。

- 速度快、功耗相对较高、成本高。

- DRAM(动态 RAM)

- 每比特仅使用 1 个晶体管 + 1 个电容。

- 利用电容存储电荷表示数据,电荷会自然泄漏,因此需要定期刷新。

- 密度高、成本低、速度相对较慢。

DRAM 结构特点

- 电容通常采用垂直堆叠或深槽结构,以缩小芯片面积。

- 需要外围刷新电路定期对每一行进行读取并重写,以维持数据。

- 常见封装形式:DDR SDRAM、LPDDR 等,广泛应用于主内存。

SRAM 结构特点

- 六晶体管结构形成两个互锁的反相器,提供稳定的状态存储。

- 无需刷新机制,访问速度快,常用于高速缓存(Cache)。

- 多采用 CMOS 工艺制造,集成于 CPU 或 SoC 内部。

- SRAM:得益于其高速特性,主要集成在 CPU、GPU 内部作为高速缓存(L1、L2、L3 Cache),用于暂存处理器最频繁访问的数据与指令。

- DRAM:因其高密度和低成本,用于构成系统主内存(如 DDR4、DDR5)、图形处理器的显存,以及各类需要大容量暂存数据的设备。

1.5 SRAM 与 DRAM 综合对比

| 参数 | SRAM | DRAM |

|---|---|---|

| 每比特晶体管数 | 6 或 8 个 | 1 个(+1 电容) |

| 访问速度 | 快(基准时间 1x) | 较慢(约 SRAM 的 10 倍) |

| 是否需要刷新 | 否 | 是 |

| 是否支持 EDC | 可能支持 | 通常支持 |

| 成本 | 高(约为 DRAM 的 100 倍) | 低(基准成本 1x) |

| 主要应用场景 | CPU 高速缓存 | 主内存、显存(帧缓冲区) |

| 功耗 | 较高(静态功耗显著) | 较低(需动态刷新) |

| 集成度 | 低 | 高 |

说明:EDC(Error Detection and Correction)指错误检测与纠正技术,在 DRAM 中因容量大、易受干扰而普遍采用,SRAM 中则视应用需求而定。

1.6 增强型DRAM技术

- 同步DRAM(SDRAM):使用标准时钟信号替代异步控制。

- 双倍速率同步DRAM(DDR SDRAM):利用时钟双边沿传输,每引脚每周期发送两位。

- DDR代际区分

- DDR:2位预取缓冲

- DDR2:4位预取缓冲

- DDR3:8位预取缓冲

- DDR4:16位预取缓冲

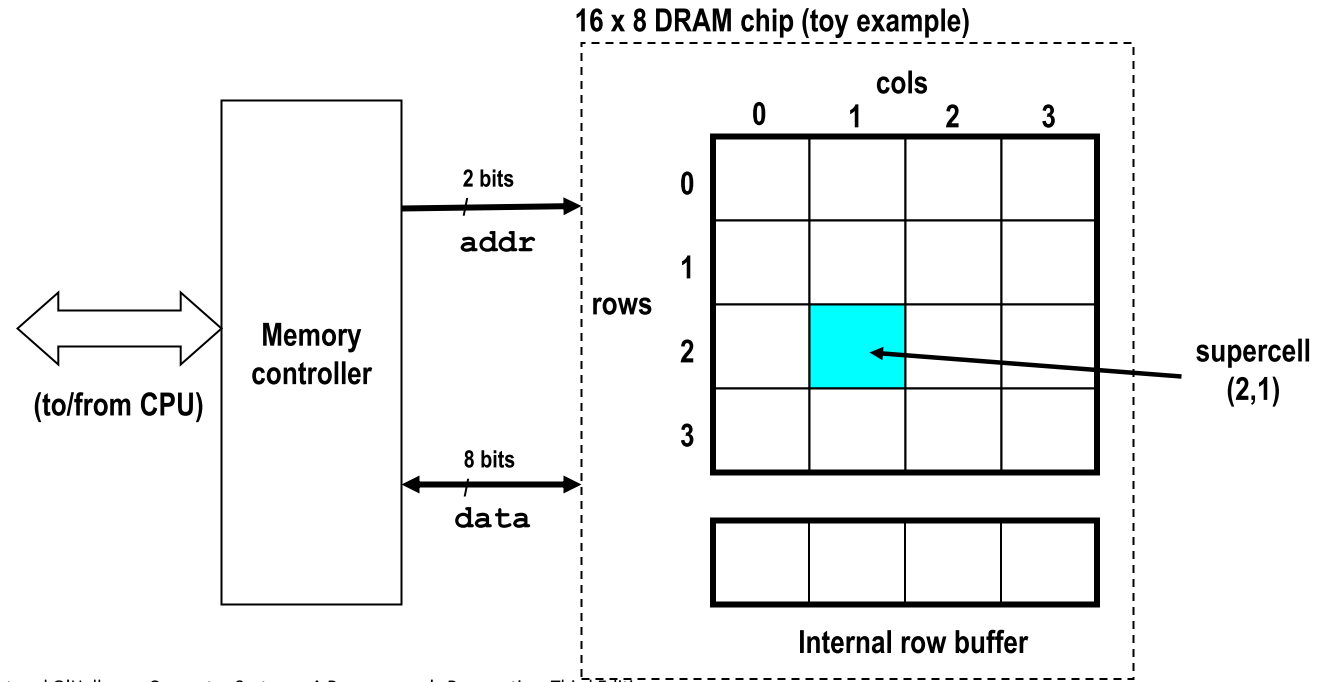

1.7 DRAM组织结构

- d × w D R A M d\times w DRAM d×wDRAM:总共 d ⋅ w d·w d⋅w位,组织为 d d d个大小为 w w w位的超单元。

- 16x8 DRAM芯片:地址输入为2位,数据输出为8位,内部包含行缓冲区,连接内存控制器与CPU的数据通路。

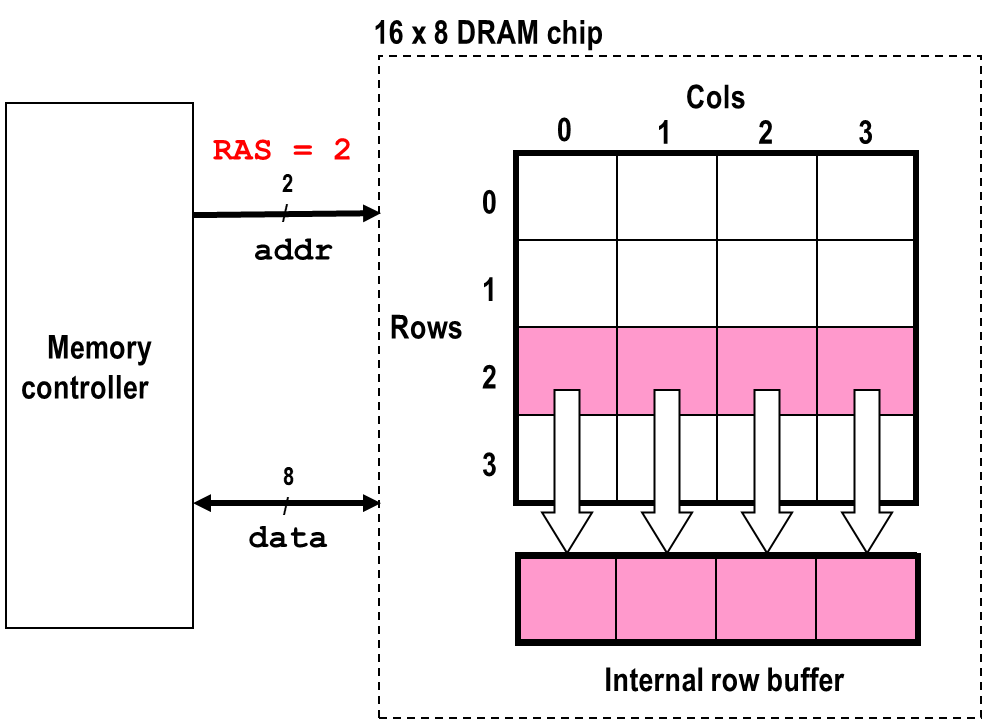

1.8 读取DRAM超单元(2,1)过程

步骤1(a):行选通(RAS),RAS选择第2行。

步骤1(b):行复制,第2行内容从DRAM阵列复制到内部行缓冲区。

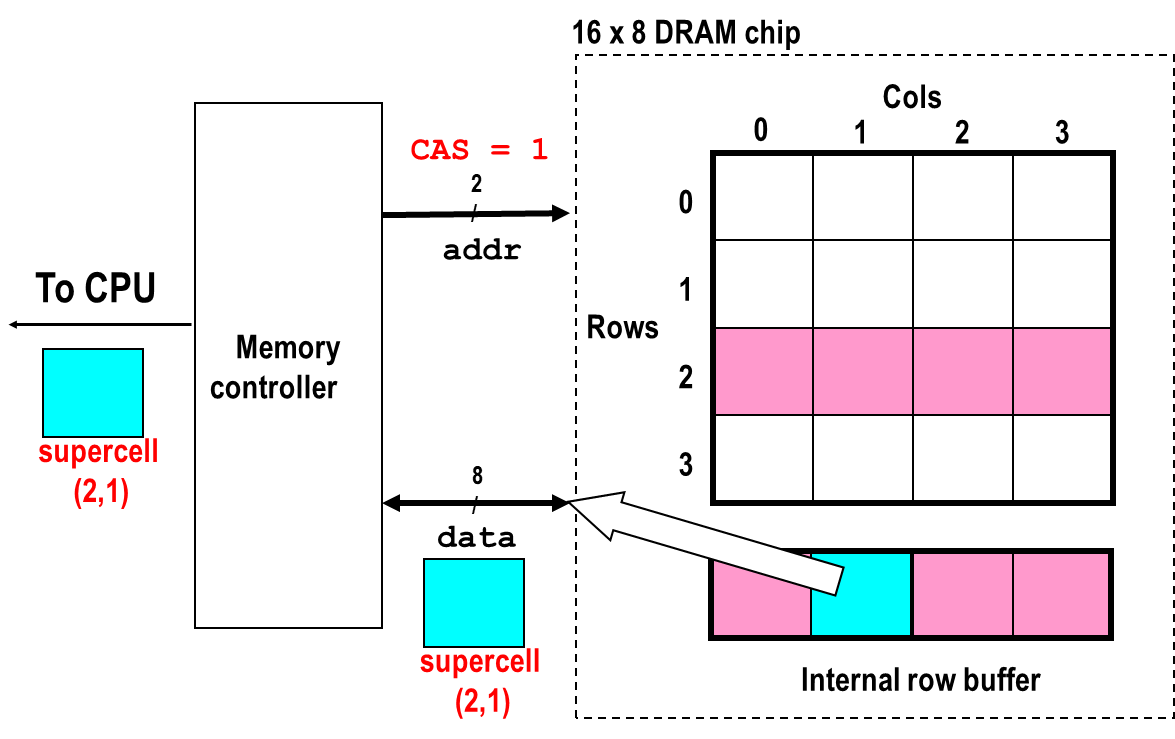

步骤2(a):列选通(CAS),CAS选择第1列

步骤2(b):数据输出,超单元(2,1)从缓冲区复制到数据线,最终传回CPU。

步骤3:刷新写回,所有数据写回原行以完成刷新操作。

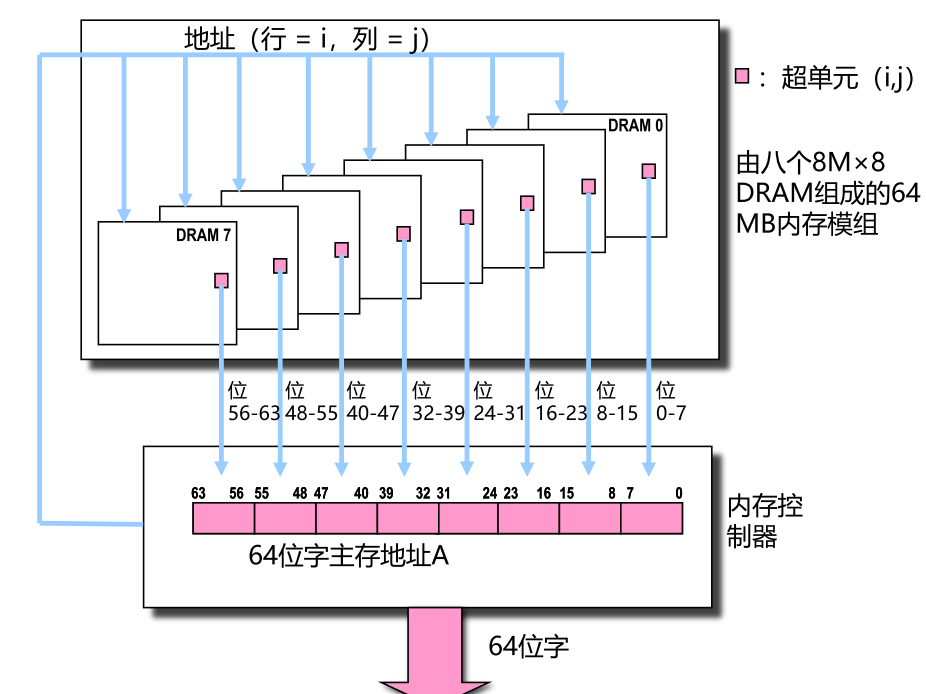

1.9 内存模块设计

- 64MB内存模块:由八个8Mx8 DRAM芯片组成,每个芯片提供8位数据(bit 0-7 至 bit 56-63),形成64位字宽的主存。

- 寻址机制:地址分为行 ( i ) (i) (i)和列 ( j ) (j) (j),超单元 ( i , j ) (i,j) (i,j)通过内存控制器统一管理,支持64位字的读写操作。

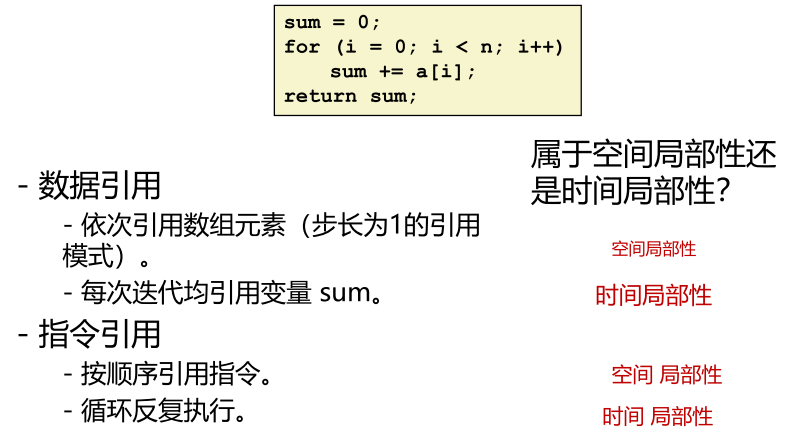

二 局部性原理

- 局部性原理:程序倾向于使用与其最近所用数据或指令地址相近或相同的地址处的数据和指令。

- 时间局部性:最近被引用的项很可能在近期被再次引用。

- 空间局部性:地址相近的项倾向于在时间上被临近引用。

三 存储器层次结构

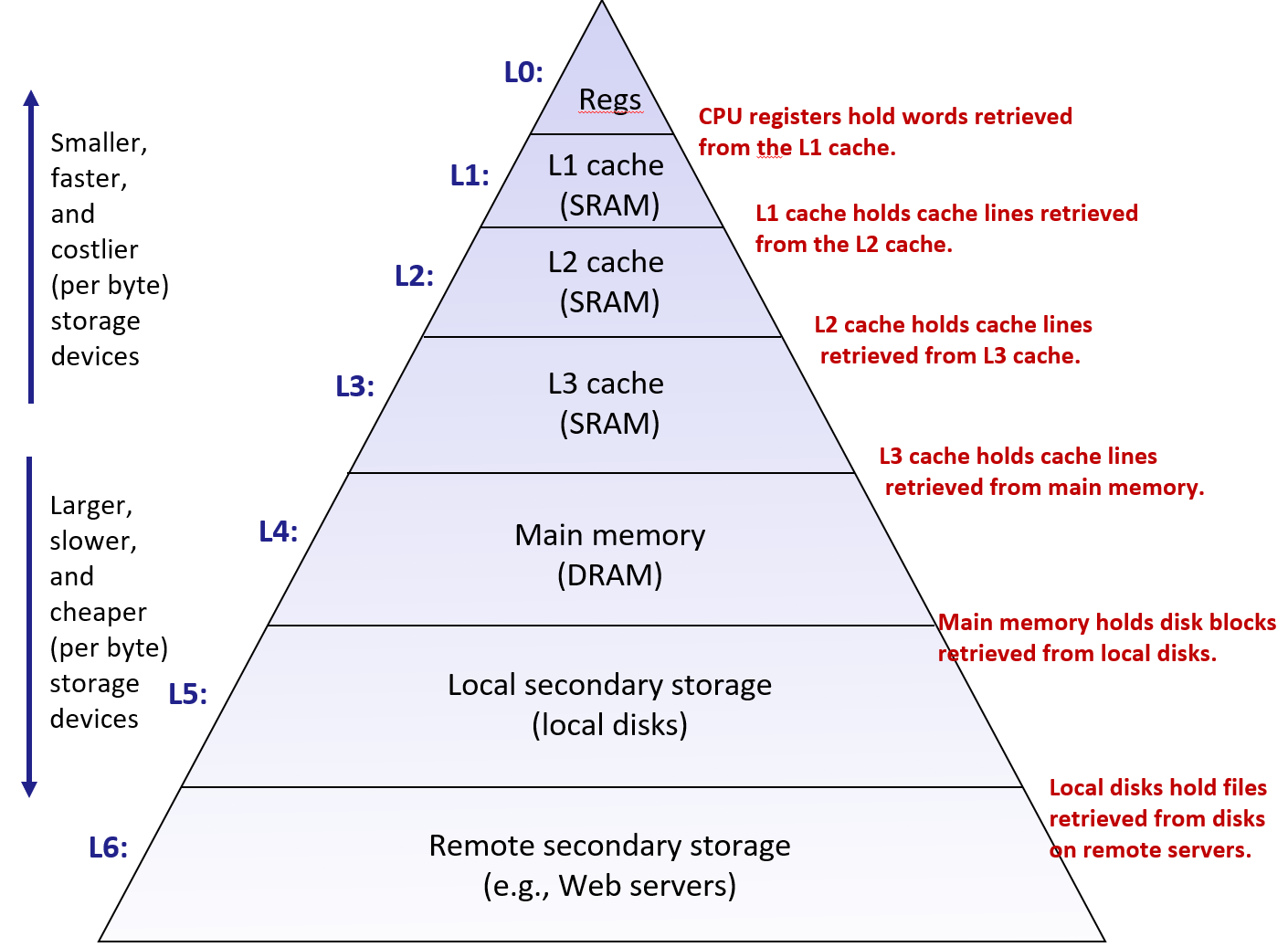

3.1 存储器的层次结构

- 快速存储技术单位字节成本更高、容量更小、功耗更大。

- CPU 与主存之间的速度差距持续扩大。

- 编写良好的程序通常表现出良好的局部性。

- 这些特性共同支持存储器层次结构的设计理念。

- L0:寄存器(CPU 核心)

- L1:L1 高速缓存(SRAM)

- L2:L2 高速缓存(SRAM)

- L3:L3 高速缓存(SRAM)

- L4:主存(DRAM)

- L5:本地辅助存储(本地磁盘)

- L6:远程辅助存储(如 Web 服务器)

- 每一层的较小、较快、较贵设备作为下一层较大、较慢、较便宜设备的缓存。

- 数据逐级加载:寄存器 ← L1 ← L2 ← L3 ← 主存 ← 本地磁盘 ← 远程服务器。

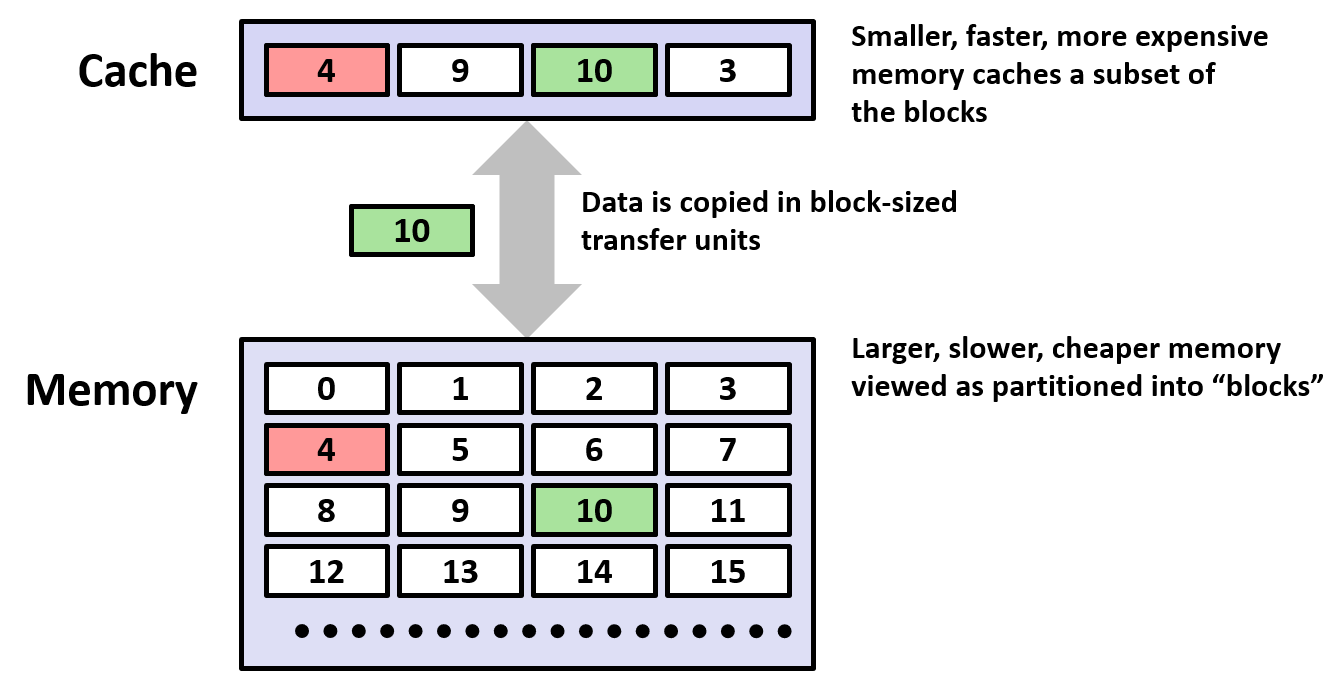

3.2 缓存基本概念

- 缓存是较小、较快的存储设备,用作较大、较慢设备中部分数据的临时存放区。

- 层次结构的核心思想:第 k k k层作为第 k + 1 k+1 k+1层的缓存。

- 工作原理:由于局部性,程序访问第 k k k层数据的频率高于第 k + 1 k+1 k+1层。

- 效益:第 k + 1 k+1 k+1层可更慢、更大、更便宜,整体系统接近顶层速度、底层成本。

数据组织与传输

- 大存储器被划分为"块"(block)。

- 小缓存存储这些块的子集。

- 数据以块为单位在缓存与主存间传输。

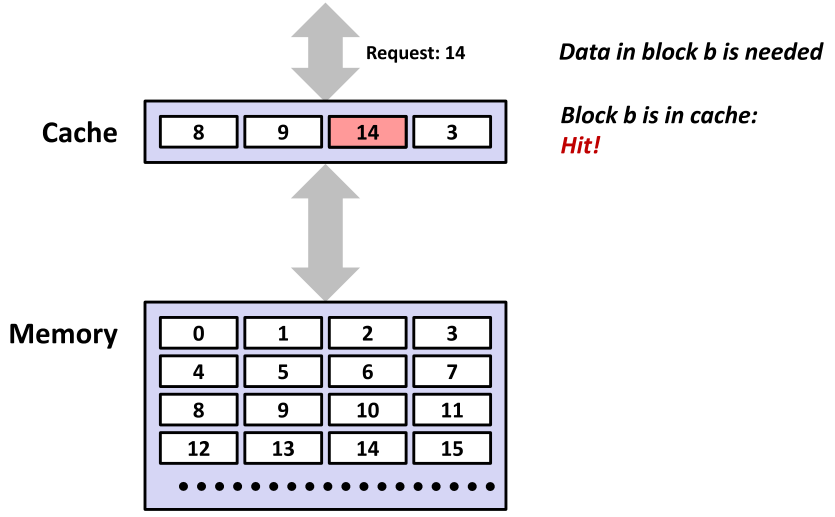

- 缓存命中(Hit):请求的数据块已在缓存中,直接从缓存读取,称为命中。

- 缓存未命中(Miss):请求的数据块不在缓存中,触发未命中,需从下层存储加载该块,加载后存入缓存。

- 涉及策略:

- 放置策略:决定块在缓存中的位置。

- 替换策略:决定哪个现有块被替换(牺牲块)。

- 空间局部性影响未命中次数:访问相邻数据时更可能命中。

3.3 缓存未命中的类型

三种未命中类型

- 冷启动未命中(强制性未命中):缓存初始为空,首次访问必然未命中。

- 容量未命中:活跃数据集(工作集)超过缓存容量。

- 冲突未命中:缓存限制某些块只能映射到特定位置。多个数据映射到同一缓存块导致频繁替换。示例:交替访问块 0 和 8,若均映射到同一位置,则每次访问都未命中。

| 缓存类型 | 缓存内容 | 位置 | 延迟 | 管理者 |

|---|---|---|---|---|

| 寄存器 | 4--8 字节字 | CPU 核心 | 0 周期 | 编译器 |

| TLB | 地址翻译 | 芯片上 TLB | 0 周期 | 硬件 MMU |

| L1 缓存 | 64 字节块 | 片上 L1 | 4 周期 | 硬件 |

| L2 缓存 | 64 字节块 | 片上 L2 | 10 周期 | 硬件 |

| 虚拟内存 | 4KB 页面 | 主存 | 100 周期 | 硬件 + 操作系统 |

| 缓冲区缓存 | 文件部分内容 | 主存 | 100 周期 | 操作系统 |

| 磁盘缓存 | 磁盘扇区 | 磁盘控制器 | 100,000 周期 | 磁盘固件 |

| 网络缓冲缓存 | 文件部分内容 | 本地磁盘 | 10,000,000 周期 | NFS 客户端 |

| 浏览器缓存 | 网页 | 本地磁盘 | 10,000,000 周期 | Web 浏览器 |

| Web 缓存 | 网页 | 远程服务器磁盘 | 1,000,000,000 周期 | Web 代理服务器 |