文章目录

说明

- 庄老师的课堂,如春风拂面,启迪心智。然学生愚钝,于课上未能尽领其妙,心中常怀惭愧。

- 幸有课件为引,得以于课后静心求索。勤能补拙,笨鸟先飞,一番沉浸钻研,方窥见知识殿堂之幽深与壮美,竟觉趣味盎然。

- 今将此间心得与笔记整理成篇,公之于众,权作抛砖引玉。诚盼诸位学友不吝赐教,一同切磋琢磨,于学海中结伴同行。

- 资料地址:computing-system-security

缓存存储器

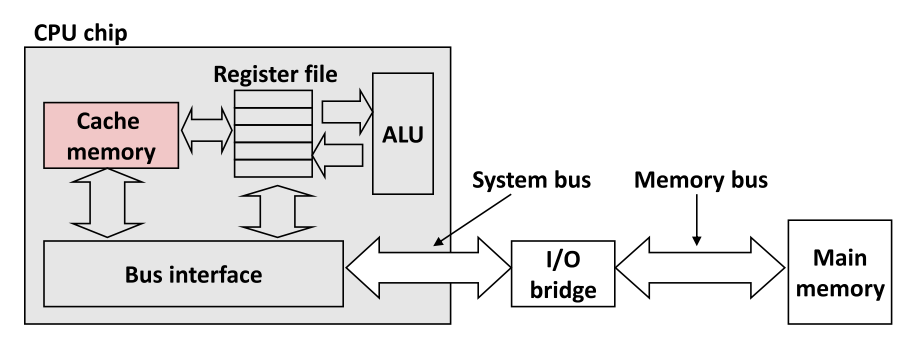

- 缓存存储器是小型、高速、基于SRAM的存储器,由硬件自动管理,存储主存中频繁访问的数据块。

- CPU访问流程:CPU首先在缓存中查找数据,若命中则直接使用;否则从主存加载并存入缓存。

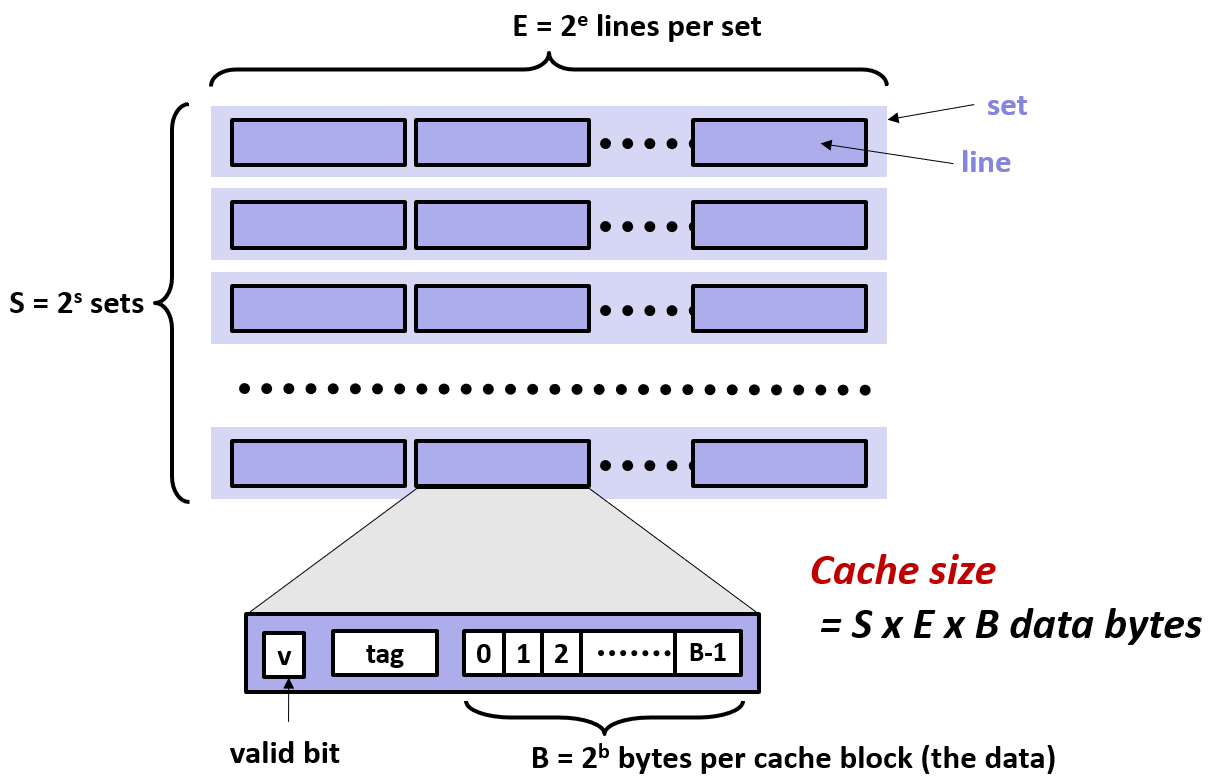

缓存通用组织结构(S, E, B)

- S = 2 s S = 2^s S=2s:缓存组数

- E = 2 e E = 2^e E=2e:每组路数(lines per set)

- B = 2 b B = 2^b B=2b:每块字节数(block size)

- 缓存总大小 = S × E × B 字节 缓存总大小 = S × E × B 字节 缓存总大小=S×E×B字节

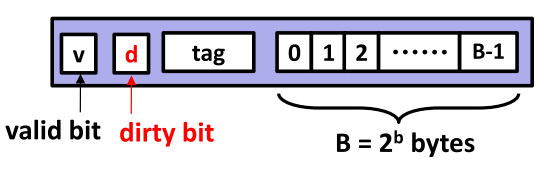

- 缓存行结构包含有效位(valid bit)、标记字段(tag)、数据块(data block) ,可选脏位(dirty bit)用于写回策略。

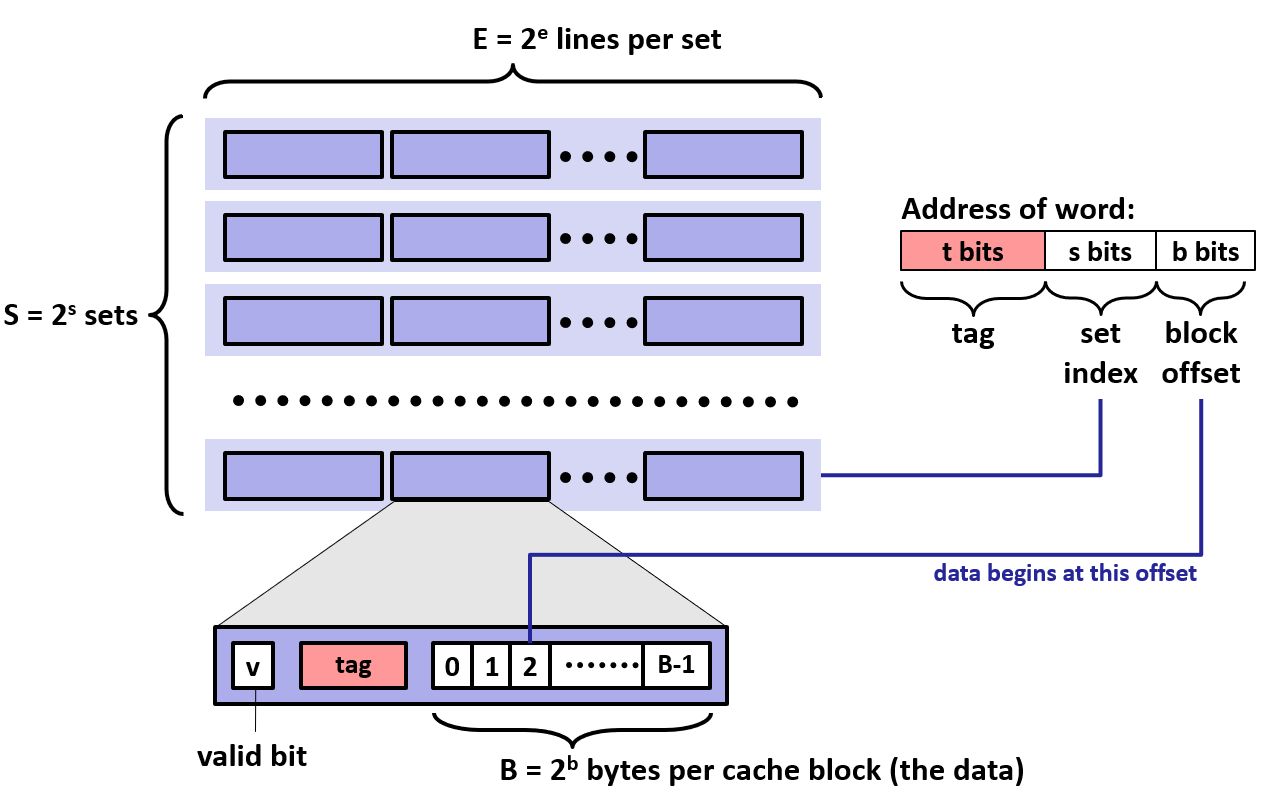

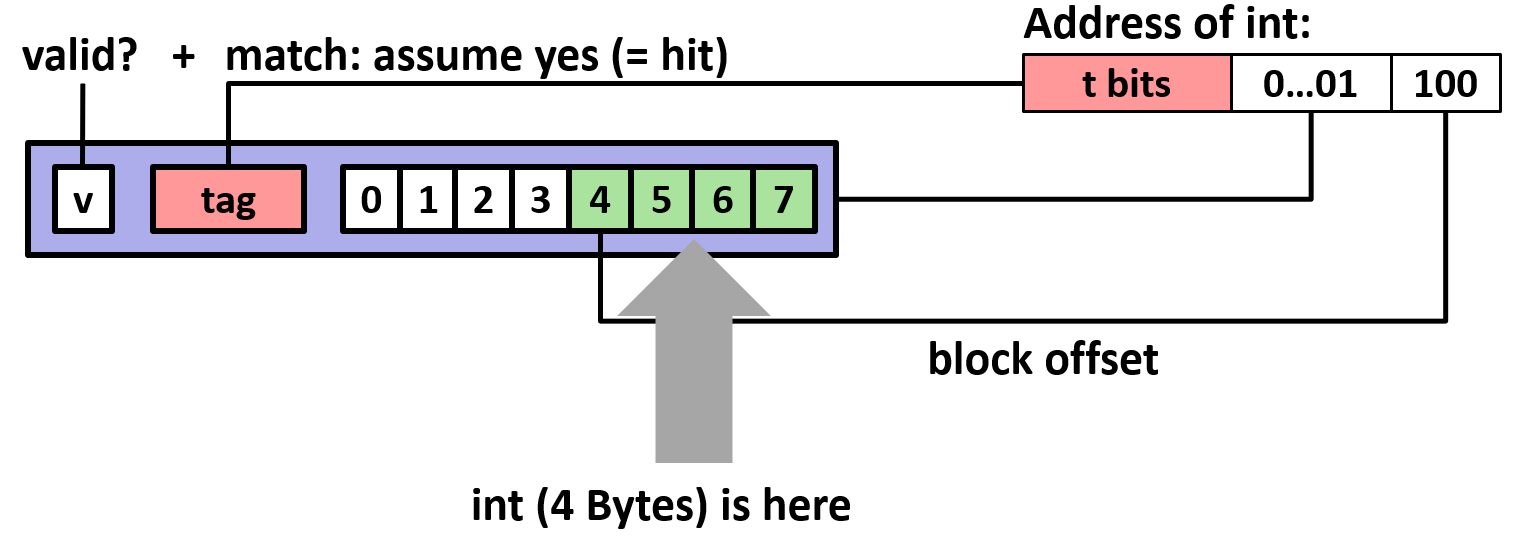

缓存读取过程

- 地址解析:地址划分为三部分标记(t bits)、组索引(s bits)、块内偏移(b bits)。

查找步骤

- 根据组索引定位对应组。

- 在该组所有路中比较标记是否匹配且有效位为1。

- 若命中,则根据偏移提取所需数据。

映射方式(重点)

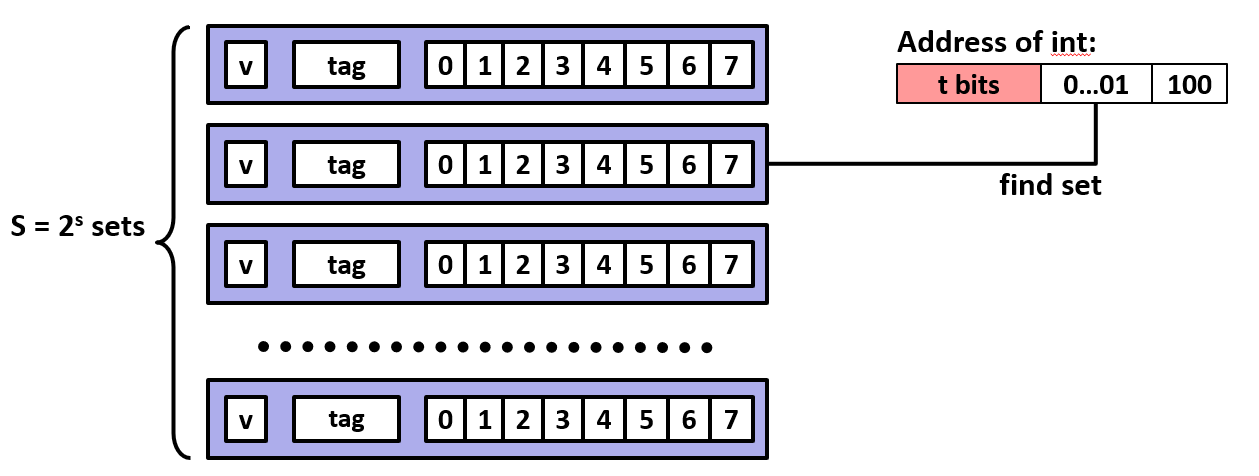

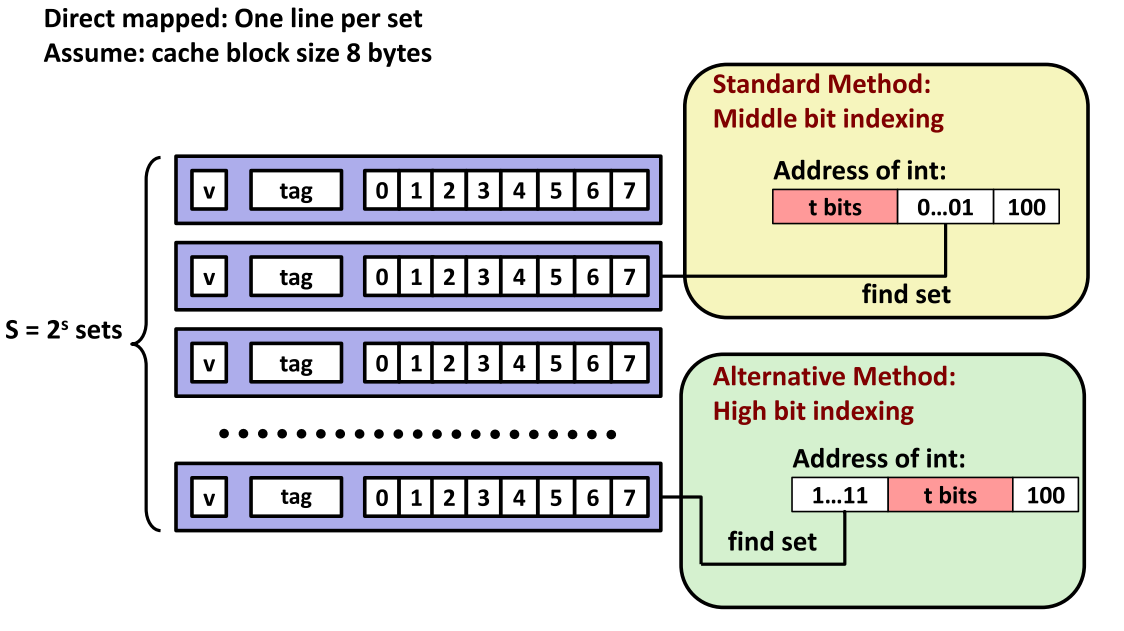

直接映射(E=1)

- 直接映射的特点是每组仅一条缓存行(1路组相联),结构简单但易产生冲突未命中 。

- 地址映射案例:每组仅一行,给定块大小B=8字节。

- 命中判断:若对应行有效且标记匹配,则命中;否则为未命中,需替换旧行。

- 最后,冲突的处理

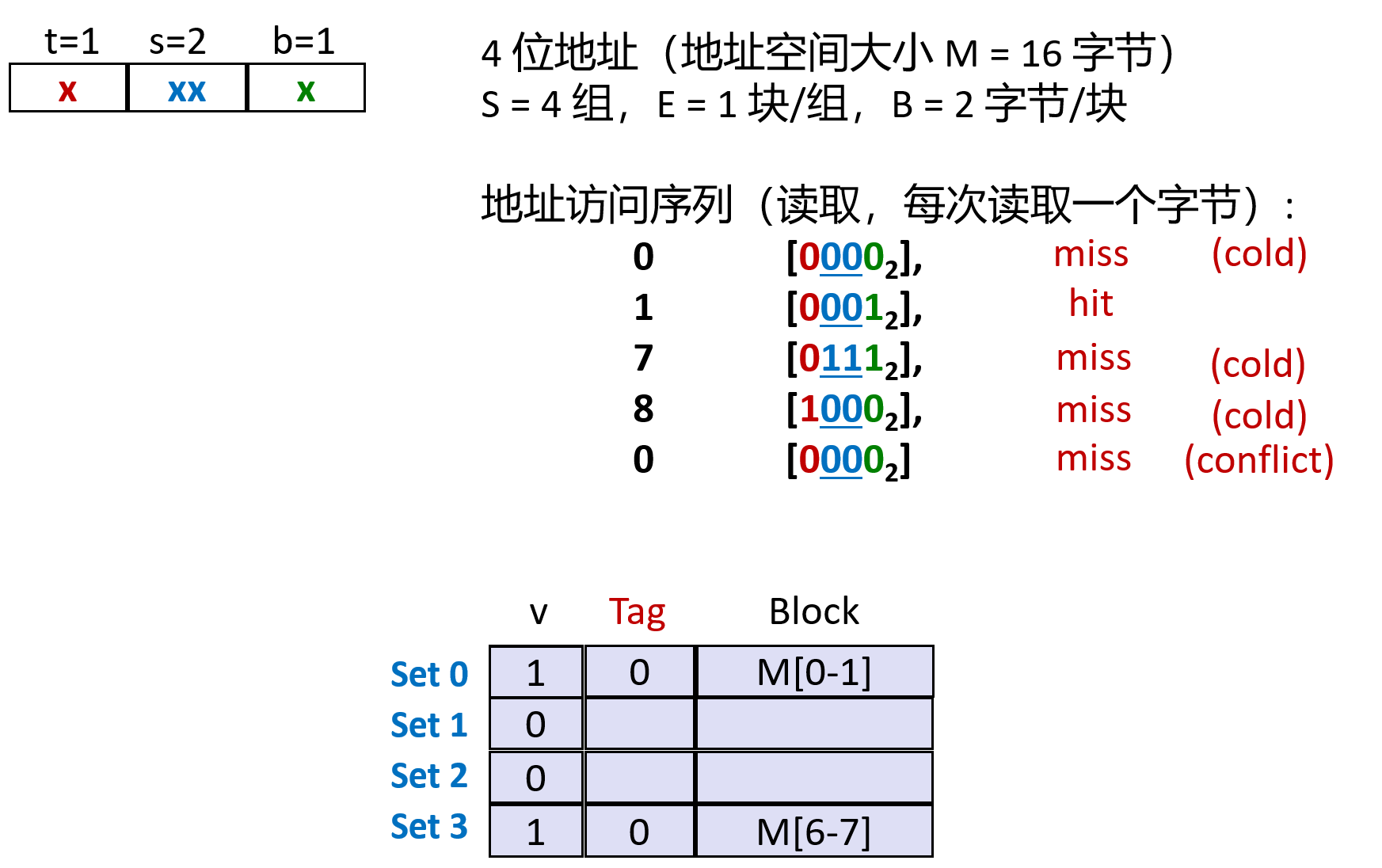

- 缓存结构分析

- 地址空间 :4 位地址(16 字节,

M=16)。 - 缓存配置 :

S=4个组(Set),每组E=1个块(Block)。每块B=2字节(Block size)。 - 地址划分 :

- 组索引(s=2 位) :选择 4 个组之一(

00、01、10、11)。 - 块内偏移(b=1 位) :选择块内的 2 字节(

0或1)。 - 标签(t=1 位) :剩余高位(

0或1)。

- 组索引(s=2 位) :选择 4 个组之一(

- 地址

0000₂的解析

- 二进制地址:

0000。 - 组索引 :中间2 位

00→ 对应 Set 0。 - 标签 :高 1 位

0。 - 块内偏移 :最低位

0(选择块内第 0 字节)。

- 地址序列的影响

- 地址序列:

0(0000₂)、1(0001₂)、7(0111₂)、8(1000₂)、0(0000₂)。 - 第一次访问

0:冷启动未命中(Cold Miss),加载M[0-1]到 Set 0。 - 访问

1:命中(Hit),因为1与0同属 Set 0,标签匹配。 - 访问

7:冷启动未命中(Cold Miss),加载M[6-7]到 Set 3(组索引11)。 - 访问

8:冷启动未命中(Cold Miss),加载M[8-9]到 Set 0(组索引00),替换原 Set 0 的数据。 - 再次访问

0:冲突未命中(Conflict Miss),因为 Set 0 的块已被8的数据覆盖,标签匹配但数据不正确。

E路组相联缓存(E=2)

- 结构特点:每组包含E条缓存行,提供更高的灵活性,降低冲突未命中概率

- 查找方式:同时比较组内所有行的标记,只要任一行匹配且有效即为命中

- 替换策略:未命中时选择一条行替换,常见策略有随机、LRU(最近最少使用)。

- 2路组相联缓存模拟:

S=2组,E=2路/组,B=2字节/块->t=2, s=1, b=1 → 4位地址空间(M=16字节)

写操作处理

- 多副本问题:数据存在于L1、L2、L3、主存甚至磁盘中,必须保证一致性

写命中策略分为写直达(Write-through)和写回(Write-back)

- 写直达(Write-through):立即将修改写入下层存储,简单但增加总线流量。

- 写回(Write-back):推迟到替换时才写回主存,每行需设"脏位"标识是否修改过,减少写操作次数,提升性能。

写未命中策略分为写分配和非写分配

- 写分配(Write-allocate):将目标块加载进缓存后再更新,适用于后续还有写操作的情况。

- 非写分配(No-write-allocate):直接写入主存,不加载进缓存,常与写直达搭配使用。

典型组合

- 写直达 + 非写分配

- 写回 + 写分配

使用中间位作为索引

- 假设直接映射缓存设计,块大小为8字节

对比两种索引方法

- 中间位索引(Standard Method)

- 使用地址中间几位作为组索引

- 更好地利用空间局部性

- 连续地址分布到不同组,减少冲突

- 高位索引(Alternative Method)

- 使用地址高位作为组索引

- 导致具有空间局部性的程序频繁冲突

- 不利于性能优化

缓存性能指标

- 失效率(Miss Rate):未在缓存中找到的内存访问比例(失效率 = 失效次数 / 总访问次数)

- 典型值:

- L1 缓存:3--10%

- L2 缓存:<1%(取决于大小等)

- 命中时间(Hit Time):将缓存块传送到处理器所需时间,包含判断是否命中的开销

- 典型值:

- L1:约 4 个时钟周期

- L2:约 10 个时钟周期

- 失效惩罚(Miss Penalty):因缓存失效导致的额外延迟

- 典型值:主存访问需 50--200 周期(趋势:逐渐增加)