简介

Bedrock 是由 Lawrence Berkeley National Laboratory(LBNL)多年累积的一套开源 Verilog 代码库,旨在把可移植的数字与射频模块快速带到 FPGA 平台(如 Xilinx)上。项目包含平台无关的 Verilog 源码、仿真环境、板级支持以及将设计综合、实现并生成 bitstream 所需的脚本与约束。它更像一套工程级参考实现集合,而不是单一的示例工程,适合用于研究原型、教学与工程开发。

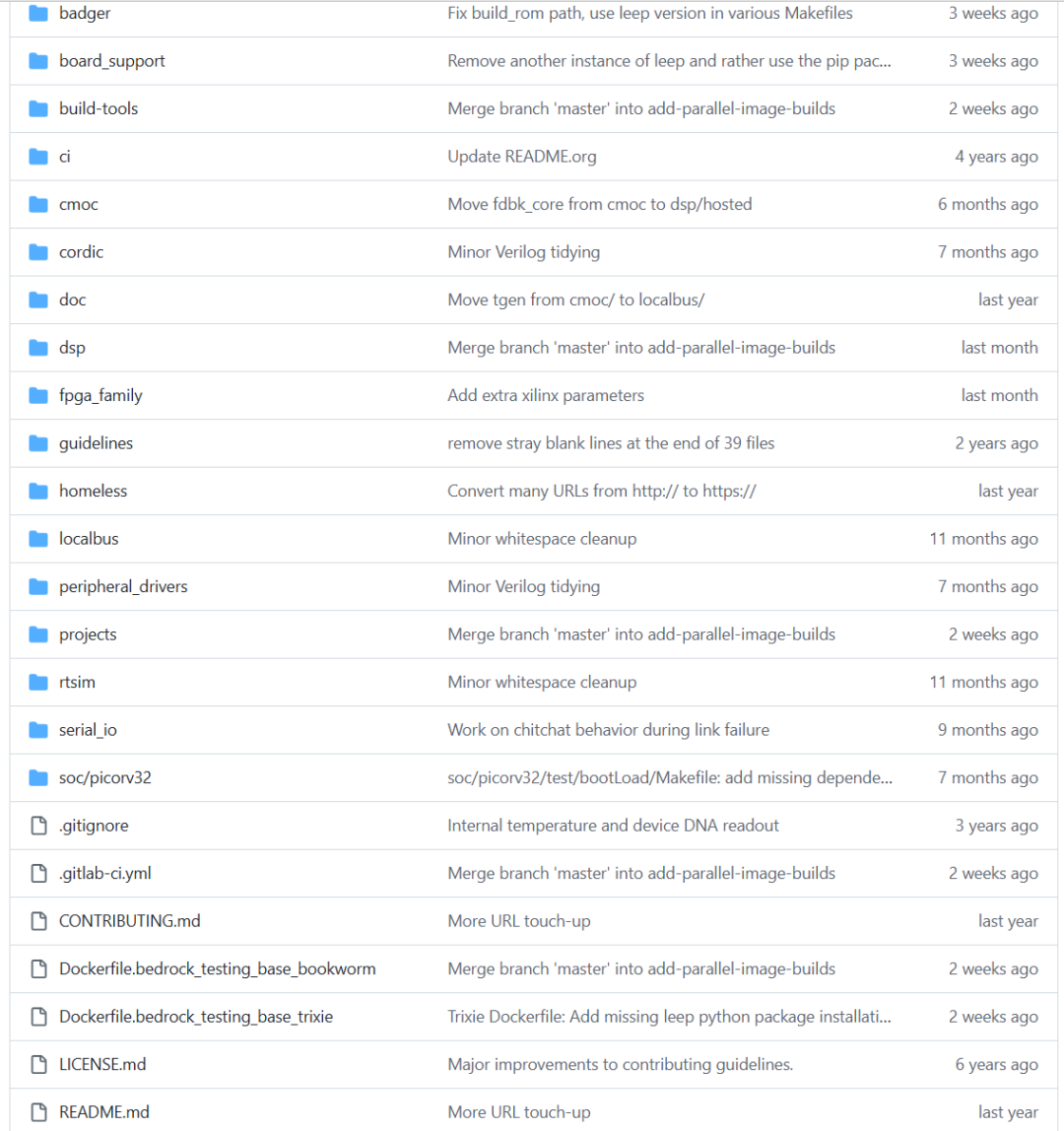

代码组织(主要子目录)

dsp:平台无关的数字信号处理模块及 testbench(例如 DDS、上/下变频、CIC 滤波器、低/高通滤波器、混频器等)。

cordic:独立的 CORDIC Verilog 实现,支持多种工作模式(可在编译时或运行时选择)。

rtsim:射频系统的实时仿真组件,包括谐振腔、电/机电模式、ADC、电缆、压电器件等,用于在上板前做系统级仿真。

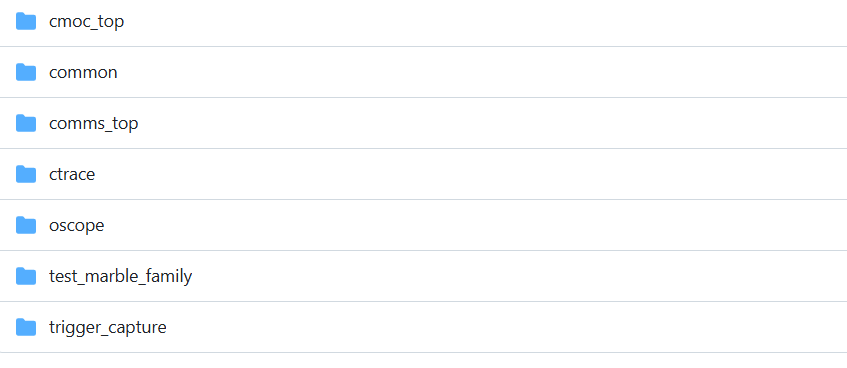

cmoc:RF 控制器的 Verilog 实现,可连接真实 ADC 或 rtsim 仿真模块,支持软硬件协同验证。

badger:在 FPGA fabric 中运行的实时以太网/IPv4/UDP 报文响应核心。

fpga_family:针对不同 FPGA 家族的约束文件与 vendor 特性钩子(hooks)。

localbus:项目内部广泛使用的片内 localbus(总线)规范与文档。

board_support:板级引脚映射与板相关配置文件。

projects:若干已实例化的工程,能被编译、综合并生成可下板的 bit 文件(覆盖不同板卡/平台)。

构建、仿真与工具链

开发环境:面向 *nix 系统(Linux/macOS),构建与自动化以 GNU Make 为中心。

仿真工具:默认使用 iverilog 进行仿真;部分模块开始支持并使用 Verilator。

综合 / 实现:主要以 Xilinx 工具链为主,部分模块或示例也正在支持开源工具链(如 Yosys)。

持续集成:仓库接入 GitLab CI,提交后会自动运行基于仿真的回归测试,降低破坏性改动风险。可在本地通过 selftest.sh 运行一套子集测试以重现部分 CI 步骤。

命令行自动化与图形化操作并存

Bedrock 借助传统的 *nix 工具(make、grep、shell、python)实现强自动化能力,方便脚本化构建、生成接口、代码骨架等。不过在以下情形,图形化界面仍然有用:查看综合或实现后的电路图、手动调整布局/约束、定制厂商 IP 等。

为此,Bedrock 会把厂商相关的生成文件放到合成目录中的 _<VENDOR_NAME> 子目录(例如 _xilinx),这样可以在自动化流程之外,直接用厂商工具打开该项目,例如在 Vivado 中打开:

go

vivado <PROJECT_DIRECTORY>/_xilinx/<TOP_LEVEL_DESIGN_NAME>/<TOP_LEVEL_DESIGN_NAME>.xpr其中 <PROJECT_DIRECTORY> 是你运行 make 的目录,<TOP_LEVEL_DESIGN_NAME> 为 bitstream 名称(不含 .bit 扩展名)。

开发与贡献

项目提供了一套基本的贡献指南(见仓库 "On contributing"),并通过 CI 保证提交的质量。欢迎通过 fork/PR 的方式提交补丁、测试或文档改进。项目采用开源许可证(详见仓库 LICENSE 文件),在贡献前建议先阅读许可条款。