总线的操作 是指主设备与从设备通过总线完成一次数据传输的完整流程,定时(时序)是指总线操作中各信号的时序配合规则,两者结合确保数据传输的有序性和准确性。总线定时直接决定传输效率和可靠性,是总线规范的核心内容。

一、 总线的基本操作类型

总线操作由主设备发起 ,从设备响应,核心围绕数据传输展开,常见操作类型如下:

| 操作类型 | 核心流程 | 适用场景 |

|---|---|---|

| 读操作 | 主设备发送地址 + 读控制信号 → 从设备解码地址并准备数据 → 从设备将数据送上总线 → 主设备读取数据 | CPU 读取内存数据、读取外设寄存器 |

| 写操作 | 主设备发送地址 + 写控制信号 + 待写数据 → 从设备解码地址 → 从设备从总线接收数据并写入指定位置 | CPU 写入内存数据、配置外设寄存器 |

| 读 - 修改 - 写操作 | 读操作 → 主设备修改数据 → 写操作(原子操作,不可中断) | 多处理器系统中对共享变量的操作、硬件寄存器的位修改 |

| 块传输操作 | 主设备发送起始地址 + 块传输命令 → 从设备连续传输多个数据(无需重复发送地址) | 内存批量读写、硬盘数据传输(如 DMA 传输) |

| 仲裁操作 | 多主设备竞争总线时,仲裁器分配总线使用权(隐含在其他操作前) | 多主设备总线(如 I2C、PCIe)的冲突解决 |

典型操作流程(以 CPU 读内存为例)

- 总线请求:CPU 向仲裁器发送总线请求信号(BR);

- 总线授权:仲裁器授权后,向 CPU 发送总线授权信号(BG);

- 地址阶段 :CPU 将内存地址送上地址总线 ,并发送读控制信号(RD#);

- 数据阶段 :内存解码地址,将对应数据送上数据总线;

- 结束阶段:CPU 读取数据,撤销地址和控制信号,释放总线。

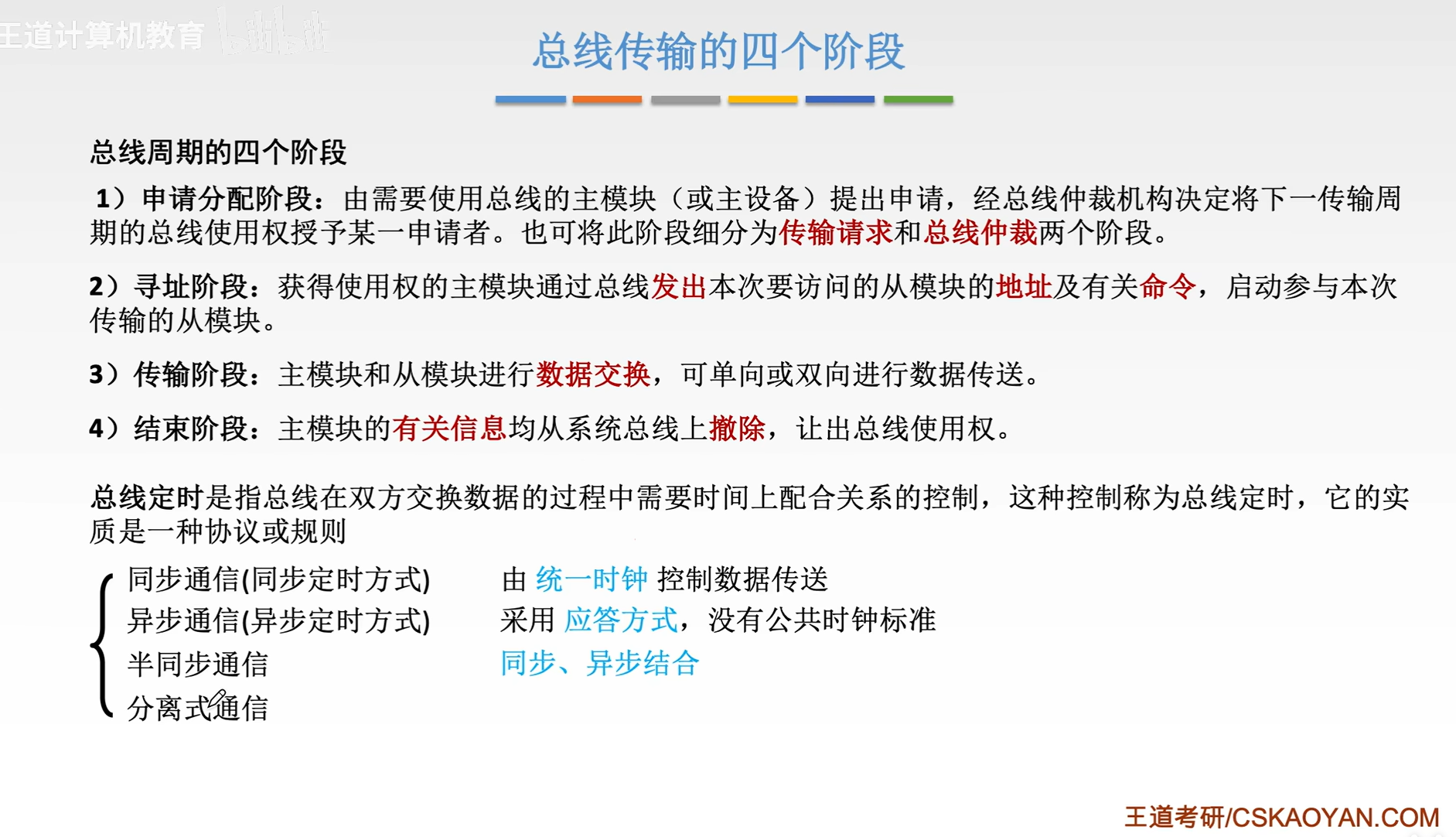

二、 总线的定时方式

总线定时的核心是协调主从设备的时序 ,确保主设备发送的信号能被从设备正确采样,从设备的响应能被主设备正确接收。根据时钟信号的作用,分为同步定时 和异步定时两大类,部分总线采用混合定时方式。

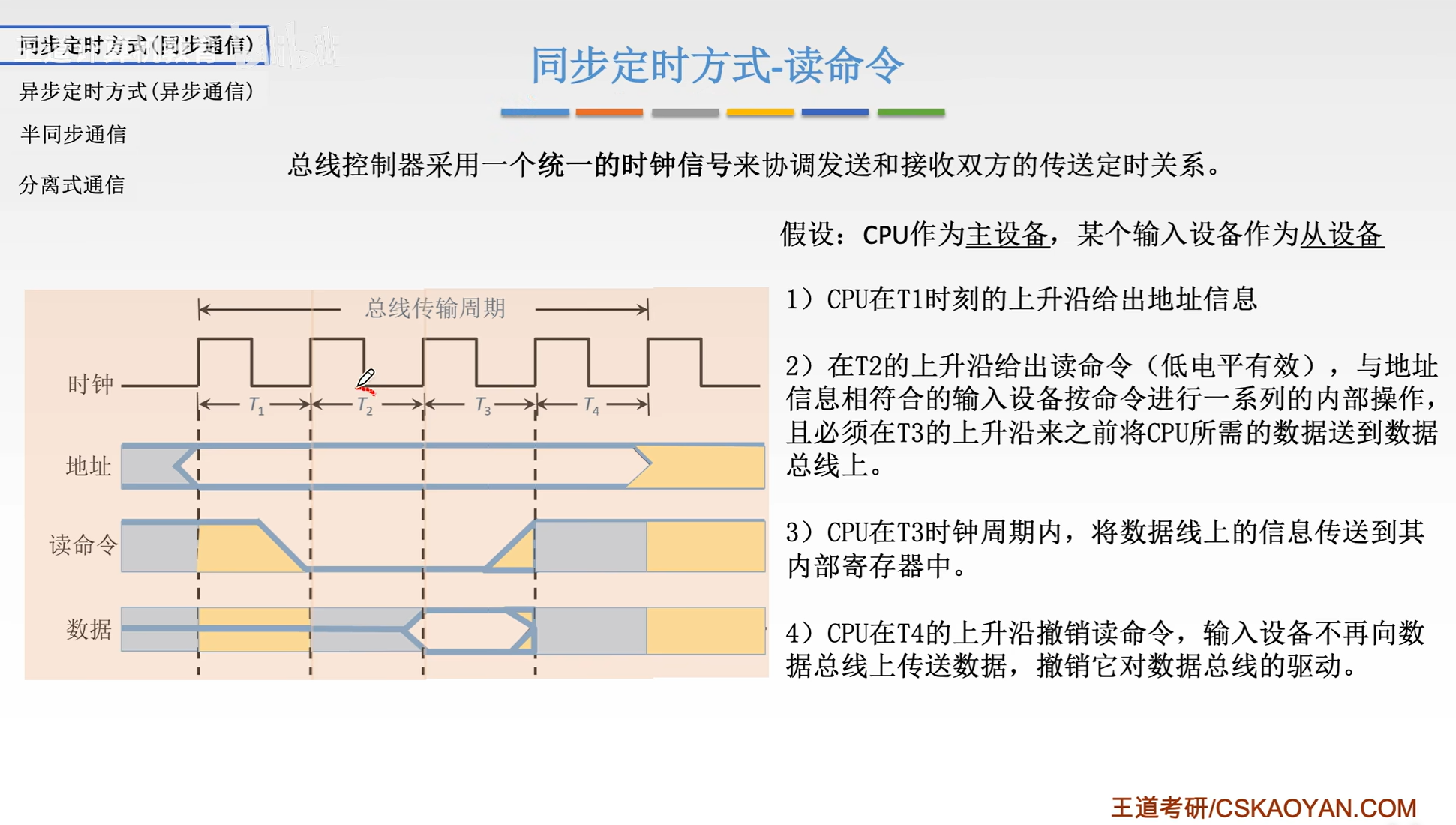

1. 同步定时(Synchronous Timing)

核心原理

所有总线操作都由统一的系统时钟信号(CLK) 同步,时钟信号的上升沿 / 下降沿作为信号采样的基准。主从设备的所有动作都必须在规定的时钟周期内完成。

时序特点

- 时钟信号由主设备或仲裁器提供,所有设备严格同步于时钟;

- 总线操作的每个阶段(地址、数据、控制)都占用固定数量的时钟周期,传输周期固定。

典型时序图(读操作)

┌─────┐ ┌─────┐ ┌─────┐ ┌─────┐

CLK ─┘ └─────┘ └─────┘ └─────┘ └───

↑ ↑ ↑ ↑

T1 T2 T3 T4

ADDR ─────────────────────────────────────────────── (T1发送地址)

RD# ─────────────────────────────────────────────── (T1发送读信号)

DATA ────────────────────────┬──────────────────────

│ (T3从设备输出数据)- T1 周期:主设备发送地址和读控制信号;

- T2 周期:从设备解码地址,准备数据;

- T3 周期:从设备将数据送上数据总线;

- T4 周期:主设备读取数据,撤销地址和控制信号。

优缺点

| 优点 | 缺点 |

|---|---|

| 时序逻辑简单,硬件实现成本低 | 传输速度受限于最慢设备(需满足所有设备的响应时间) |

| 信号采样清晰,不易出错 | 时钟频率提升受限(高频易出现时序偏移和串扰) |

| 适合高速总线的流水线操作 | 灵活性差,无法适配不同速度的设备 |

适用场景

- 设备速度一致的短距离总线:如CPU 与内存的总线 、片内总线(AXI/AHB)、PCIe 总线;

- 对时序一致性要求高的场景:如流水线 CPU 的内部数据传输。

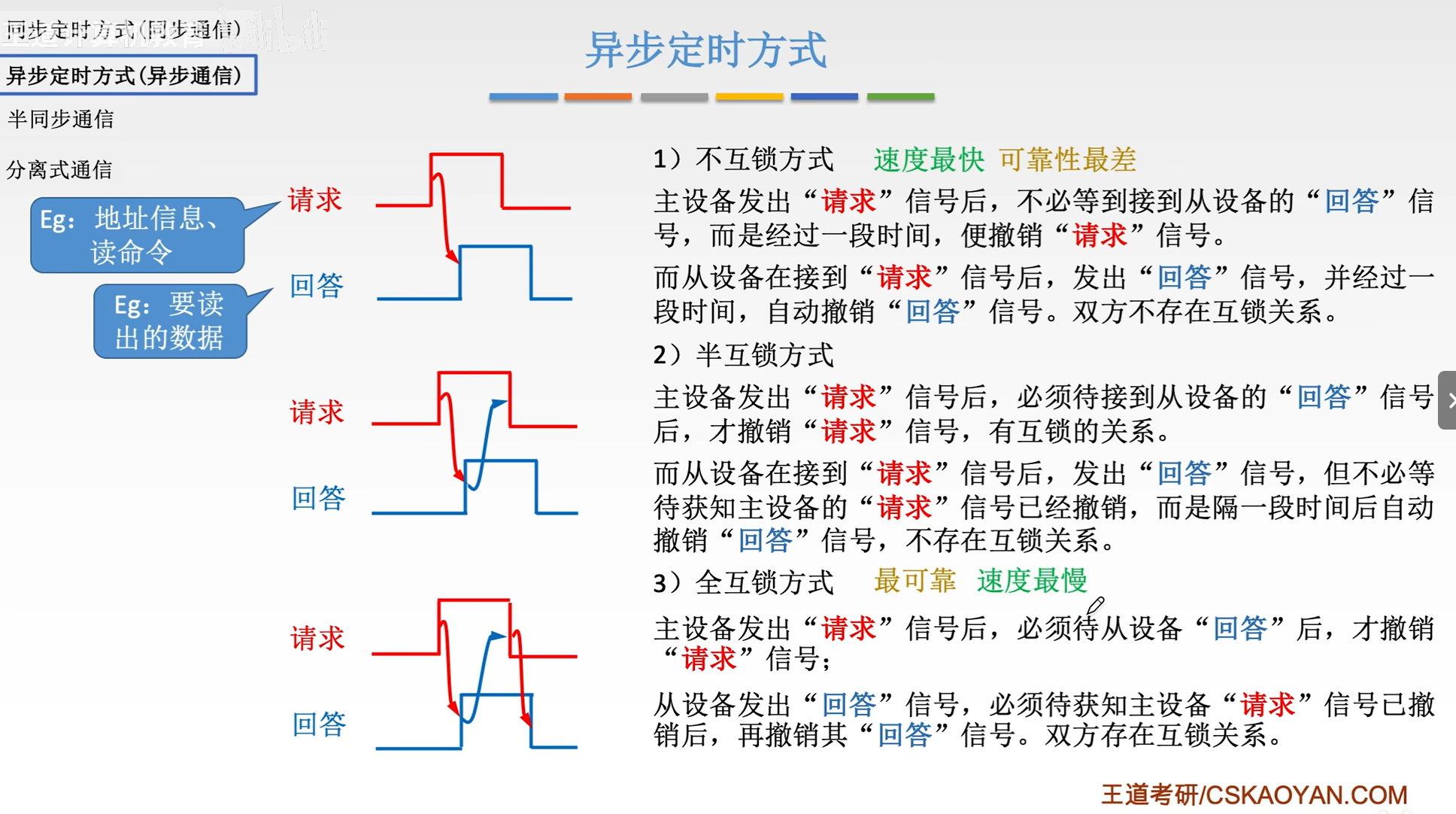

2. 异步定时(Asynchronous Timing)

核心原理

无统一的系统时钟,总线操作的时序由主从设备之间的 "握手信号" 协调。主设备发起操作后,等待从设备的响应信号,再进行下一步动作,传输周期按需动态调整。

关键握手信号

- 请求信号(REQ):主设备向从设备发送,发起读 / 写操作;

- 响应信号(ACK):从设备向主设备发送,确认数据已准备好(读操作)或数据已接收(写操作)。

时序类型(按握手方式分类)

(1) 全互锁异步定时(最常用)

主从设备的请求和响应信号相互锁定,确保双方完全同步,是最可靠的异步定时方式。

- 流程:

- 主设备发送地址 + 控制信号 + REQ → 等待从设备响应;

- 从设备准备数据 → 发送 ACK → 等待主设备撤销 REQ;

- 主设备读取数据 → 撤销 REQ → 等待从设备撤销 ACK;

- 从设备撤销 ACK → 总线回到空闲状态。

- 特点:REQ 和 ACK 信号的上升沿 / 下降沿相互触发,无时序风险,适配任意速度的设备。

(2) 半互锁异步定时

- 流程:主设备发送 REQ 后,无需等待 ACK 撤销,即可进入下一次操作;从设备收到 REQ 后,发送 ACK 并保持,直到 REQ 撤销。

- 特点:比全互锁速度快,但可靠性略低,适合从设备响应速度稳定的场景。

(3) 非互锁异步定时

- 流程:主设备发送 REQ 后,直接发送数据;从设备接收数据后,发送 ACK,双方无需等待对方信号撤销。

- 特点:速度最快,但可靠性最差,仅适用于主从设备距离极近、延迟可忽略的场景。

优缺点

| 优点 | 缺点 |

|---|---|

| 灵活性强,适配不同速度的主从设备 | 时序逻辑复杂,硬件实现成本高 |

| 传输效率高,无需为慢速设备等待 | 握手信号增加总线开销,低速总线更明显 |

| 时钟频率不受限,适合长距离传输 | 不适合流水线操作,难以实现高速并行传输 |

适用场景

- 主从设备速度差异大的总线:如CPU 与外设的总线(UART、I2C);

- 长距离通信总线:如RS485、CAN 总线(信号延迟不确定,无法同步时钟)。

3. 混合定时(Semi-synchronous Timing)

核心原理

结合同步定时和异步定时的优点:用时钟信号同步高速操作,用握手信号适配低速设备。

- 基础操作(如地址发送)由时钟同步,保证速度;

- 当从设备响应缓慢时,通过等待信号(WAIT) 延长时钟周期,避免数据丢失。

典型应用

- PCI 总线:基础传输由时钟同步,当外设响应慢时,外设发送 WAIT 信号,强制 CPU 等待一个或多个时钟周期。

三、 核心总结

- 总线操作的核心是读 / 写 / 块传输,由主设备发起、从设备响应,仲裁操作是多主设备场景的前提;

- 总线定时分为同步定时 和异步定时:同步定时依赖统一时钟,简单高效但灵活性差;异步定时依赖握手信号,灵活适配但逻辑复杂;

- 高速总线(如内存、PCIe)多用同步定时 ,低速外设总线(如 I2C、CAN)多用异步定时,混合定时兼顾两者优势;

- 定时参数(建立时间、保持时间)是总线稳定传输的关键,直接影响总线频率和传输可靠性。