一、 概况

在上一章节我们把DDR的乒乓操作的代码进行了讲解,在本章节来进行验证功能,使用两个模块来产生数据并接收数据。产生递增数据,可以通过接收数据的值,来验证数据的传输。

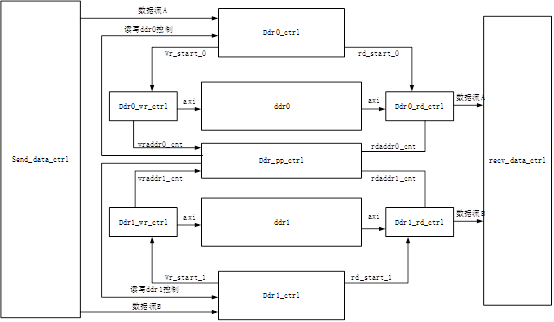

二、 流程框图

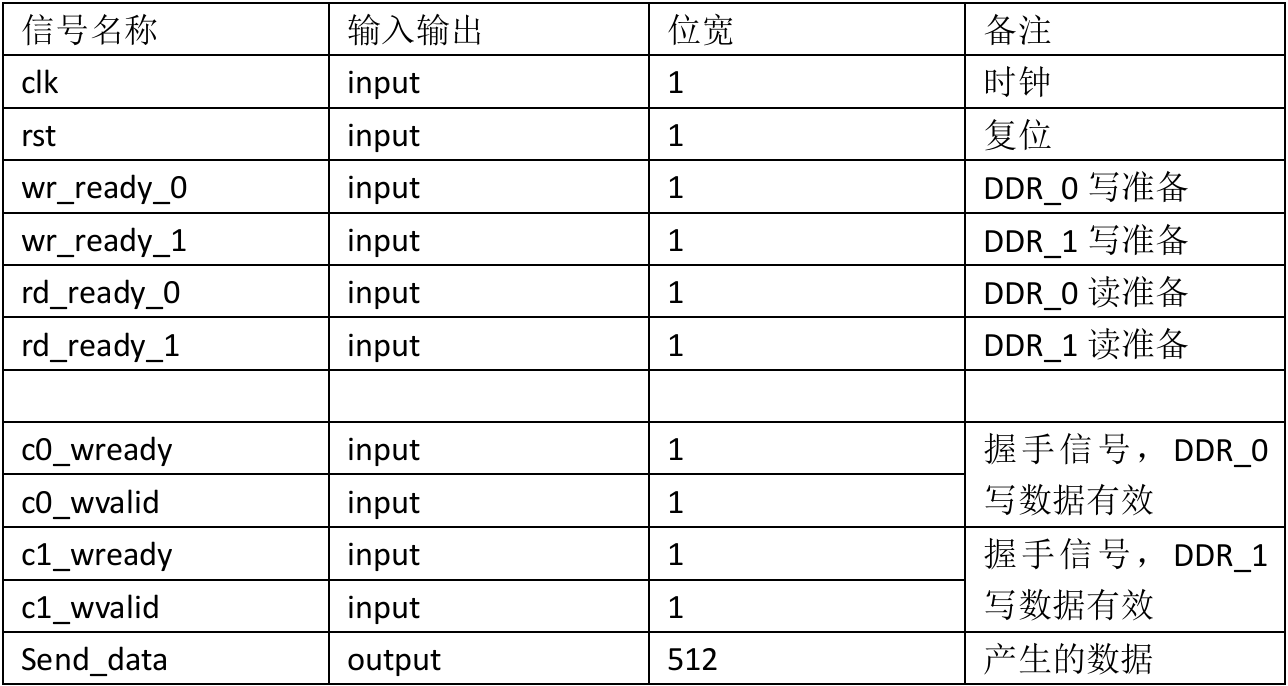

三、 send_data_ctrl模块

模块接口列表:

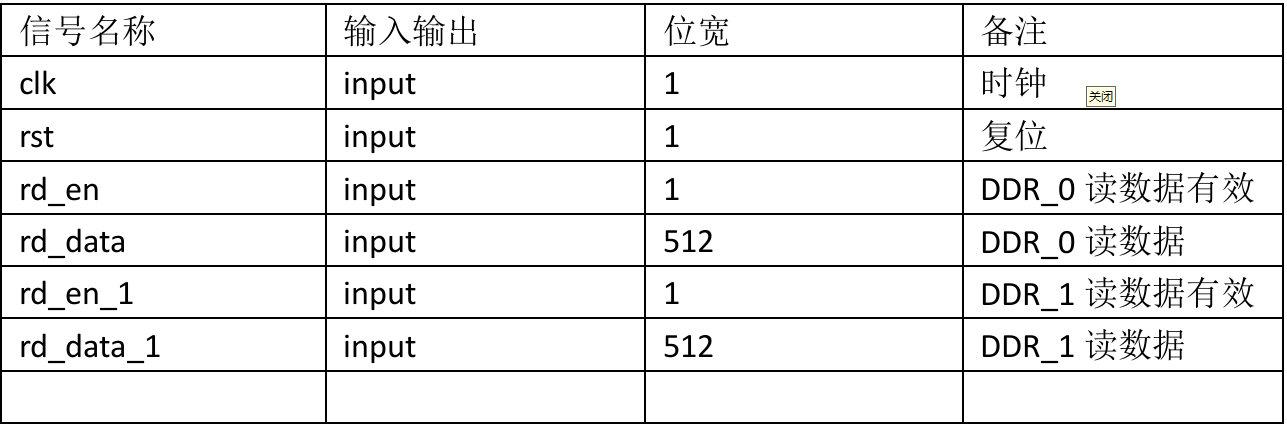

产生递增数据,控制信号已经将DDR_0的DDR_1分开,不会重叠,所以可以直接使用DDR_0和DDR_1的数据有效信号产生连续的递增数据。

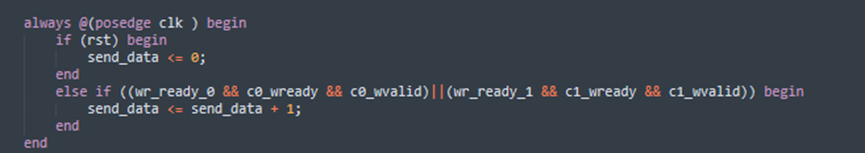

四、 recv_data_ctrl模块

模块接口列表:

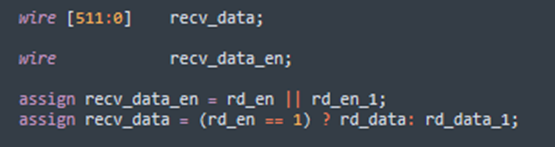

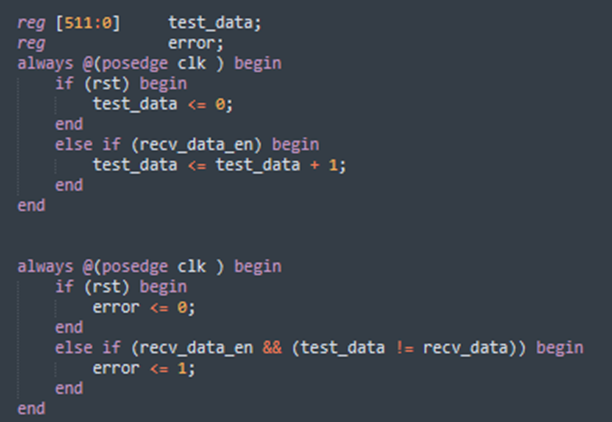

将DDR_0和DDR_1读出的数据作为接收数据

因为发送的数据为递增数据,这里就使用递增数据来验证读出的数据。

五、 仿真验证

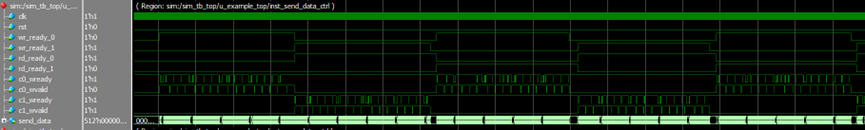

1、Send_data_ctrl模块仿真波形:

可以看到通过DDR_0和DDR_1交替发送数据。

在工程中,设置了DDR的最大内存大小为'h40000。

在DDR翻转时刻,可以看出每4096个数据翻转一次。

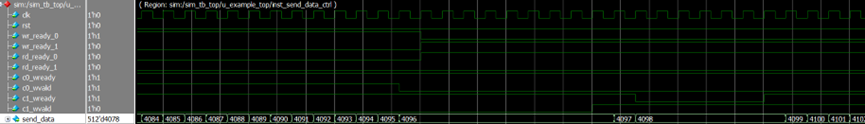

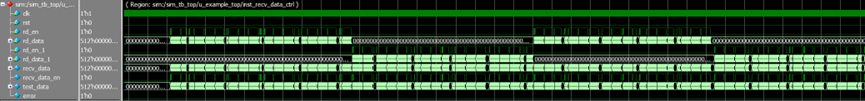

2、Recv_data_ctrl模块仿真波形:

DDR_0和DDR_1的读数据为接收的数据,通过递增数据验证,可以看到error为0,证明数据的乒乓传输正常。

六、 总结

本章节使用递增数据验证了DDR的乒乓操作,并通过仿真波形可以看出数据的发送和接收过程,下一章节我们使用dds生成sin波形来进行验证,并通过仿真来观察数据在各自DDR中的传输过程。

本文章由威三学社出品

对课程感兴趣可以联系