一、cotex-m trace组件

Cortex-M 的设计中,许多调试组件是可选的 IP 模块,请务必查阅所选芯片的相关文档。跟踪组件可能包括:

Micro Trace Buffer (MTB)

将程序流数据保存到内部 SRAM 中,数据可通过 JTAG 或SWD接口读取。SRAM 的大小和缓冲区位置可通过软件配置。当trace数据的写入与 AHB-Lite 接口的系统写入同时发生时,trace写入会优先于系统写入,并会在 AHB-Lite 访问中插入一个或多个等待状态。在高总线负载情况下,这可能会影响被跟踪应用程序的运行时性能。

Embedded Trace Macrocell (ETM)

该单元可将程序流数据传输至 TPIU,在 TPIU 中对数据进行格式化,最终传输至片外跟踪工具。可捕获的跟踪数据量取决于外部工具中(一般是外部的调试跟踪器)的缓冲区大小;若为流模式,则取决于主机硬盘的大小。

Instrumentation Trace Macrocell (ITM)

该单元提供三项主要功能:软件指令跟踪、将 DWT 的跟踪数据包整合到跟踪流中、为 ITM 和 DWT 跟踪数据包生成时间戳。

Data Watchpoint and Trace (DWT)

这一可选组件提供多项类跟踪功能,包括中断跟踪、数据跟踪、ETM 触发、PC 采样器和触发功能,后续章节将详细介绍各项功能。DWT 的输出会传输至 ITM,进行格式化后纳入跟踪流。

Trace Port Interface Unit (TPIU)

该模块负责将跟踪数据路由至最终目的地(片外或片内),可将多个来源的跟踪数据聚合为单个流,支持多核设计的跟踪。支持两种off-chip模式:SWV/SWO,以及并行跟踪。

- SWV 或 SWO 是单比特宽的跟踪端口,适用于低速跟踪(通常来自 ITM/DWT),选择此选项时,TPIU 会静默 "丢弃" ETM 数据包,不进行传输;

- 选择并行跟踪时,所有来源的数据包都会被传输。并行端口宽度可为 1 至 4 比特,其时钟可独立于 CPU。

|---------|-------------|------------------------------------------------|

| Armv6-M | Cortex-M0 | 无跟踪选项 |

| Armv6-M | Cortex-M0+ | 可选:MTB;可选:可能包含有限功能的 DWT,支持数据断点和 PC 采样器 |

| Armv6-M | Cortex-M1 | 无跟踪选项 |

| Armv7-M | Cortex-M3 | 可选:ITM、DWT、ETMv3 |

| Armv7-M | Cortex-M4 | 可选:ITM、DWT、ETMv3 |

| Armv7-M | Cortex-M7 | 可选:ITM、DWT、ETMv4(可选全数据跟踪) |

| Armv8-M | Cortex-M23 | 可选:DWT;可选:ETMv3 或 MTB(二者互斥) |

| Armv8-M | Cortex-M33 | 可选:ITM、DWT、ETMv4、MTB(设计可支持同一器件中同时存在 MTB 和 ETM) |

| Armv8-M | Cortex-M35P | 可选:ITM、DWT、ETMv4、MTB(设计可支持同一器件中同时存在 MTB 和 ETM) |

| Armv8-M | Cortex-M55 | 可选:ITM、DWT、ETMv4 |

| Armv8-M | Cortex-M85 | 可选:ITM、DWT、ETMv4 |

| Armv8-M | STAR | 可选:ITM、DWT、ETMv4 |

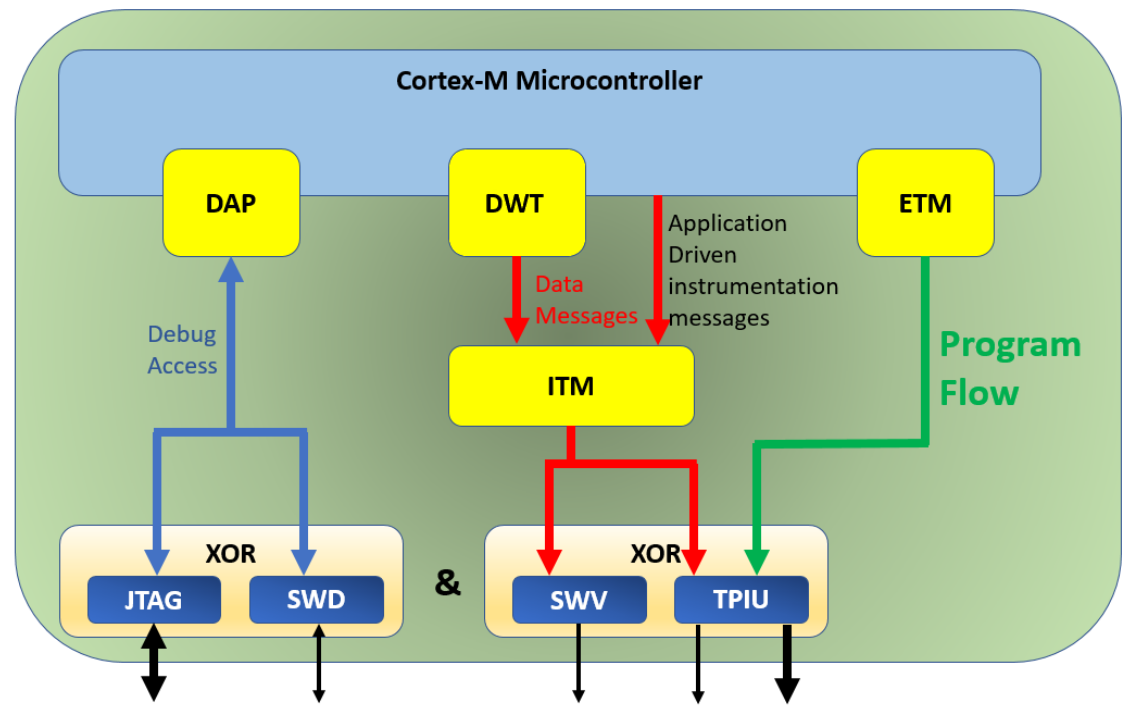

Cortex-M(≥M23)调试组件的图形概览如下图所示:

二、劳特巴赫trace基本配置

不同跟踪方式的配置

- off-chip trace(ETM、ITM):选择 Trace.METHOD 为 CAnalyzer 或 Analyzer,如果不插PowerTrace模块这里是灰色的

- on-chip trace(MTB):选择 Trace.METHOD 为 Onchip。

缓冲区大小设置

- 片外跟踪:缓冲区大小会根据芯片或工具中跟踪数据的存储量自动填充,若需较小数据量,可手动输入新值或使用命令 Trace.SIZE <n>。

- 片内跟踪(MTB):必须手动指定缓冲区大小。

模式(Mode)设置说明

| 模式 | 说明 |

|---|---|

| FIFO | 跟踪数据存储在 TRACE32 跟踪硬件的缓冲区内存中,缓冲区填满后,新数据会覆盖旧数据,跟踪采样停止时,可获取最大量的跟踪历史数据 |

| Stack | 跟踪数据存储在 TRACE32 跟踪硬件的缓冲区内存中,缓冲区接近填满时,采样停止,但目标器件继续运行 |

| Leash | 跟踪数据存储在 TRACE32 跟踪硬件的缓冲区内存中,缓冲区接近填满时,跟踪采样停止,目标器件暂停 |

| STREAM | TRACE32 跟踪硬件的缓冲区内存用作大型 FIFO,跟踪数据流式传输至主机系统硬盘上的文件,捕获的跟踪数据量受硬盘分区大小、用户指定量或(2^64)-1 帧限制 |

| PIPE | TRACE32 跟踪硬件的缓冲区内存用作大型 FIFO,跟踪数据流式传输至主机系统上读取管道或 FIFO 的应用程序,需实时处理跟踪流,不进行存储,跟踪流理论上无长度限制 |

其他关键配置

- Trace.CLOCK:需设置为mcu核心时钟频率。

- Trace.TDelay:用于将触发点设置在缓冲区起始位置(Stack 或 Leash 模式)或结束位置(FIFO 模式)之外,触发条件为 TraceTrigger 类型的断点,该断点不会停止核心,仅触发跟踪系统,也可设置为停止核心。

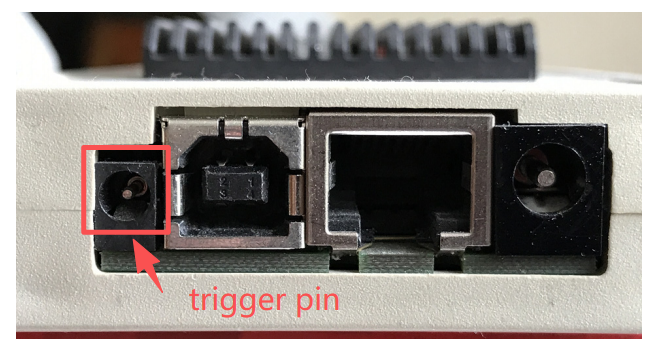

- Trace.TSELect 和 Trace.TOut:允许使用外部触发,可选择 PODBUS 上的 BusA 信号或 TRACE32 调试硬件外部的 Trigger 引脚(下图所示)。Trigger 引脚通过 Trigger Bus Window(TrBus)控制,选择 <trace>.TSELect BusA 会将 Trigger 引脚用作跟踪触发事件,选择 <trace>.TOut BusA 会在跟踪系统触发或停止跟踪时触发该引脚。

Selecting <trace>.TSELect BusA will use

the Trigger pin as the trace trigger event. Selecting <trace>.TOut BusA will trigger the pin when the trace

system triggers or stops tracing.

三、跟踪缓冲区管理

一般来说,trace buffer是有限的。可以通过设置一些触发条件来确保buffer中数据的有效性。

ref:

https://www2.lauterbach.com/pdf/training_cortexm_etm.pdf

https://blog.csdn.net/guojingyue123/article/details/147277221

https://support.lauterbach.com/kb/articles/coresight-trace-cortex-m-processors

https://wenku.baidu.com/aggs/45bc9a4e852458fb770b566d?index=0&wkts=1766932520536