背景

公司一款产品用到了该32-Bit SAR ADC芯片,测试发现在输入信号剧烈变化(比如信号切断/接通)的情况下,FPGA读出来的前几个采样点是变化前的值。

当内置滤波器选择SSINC,DF(降采样系数)配置成16384时情况尤甚。

定位

群延迟

一开始以为是FPGA内部的DMA FIFO没清空,但FPGA同事说ADC采集逻辑没设置FIFO,收到转换完成(conversion complete)中断就立即将数据从ADC读走并写入CPU侧DDR。

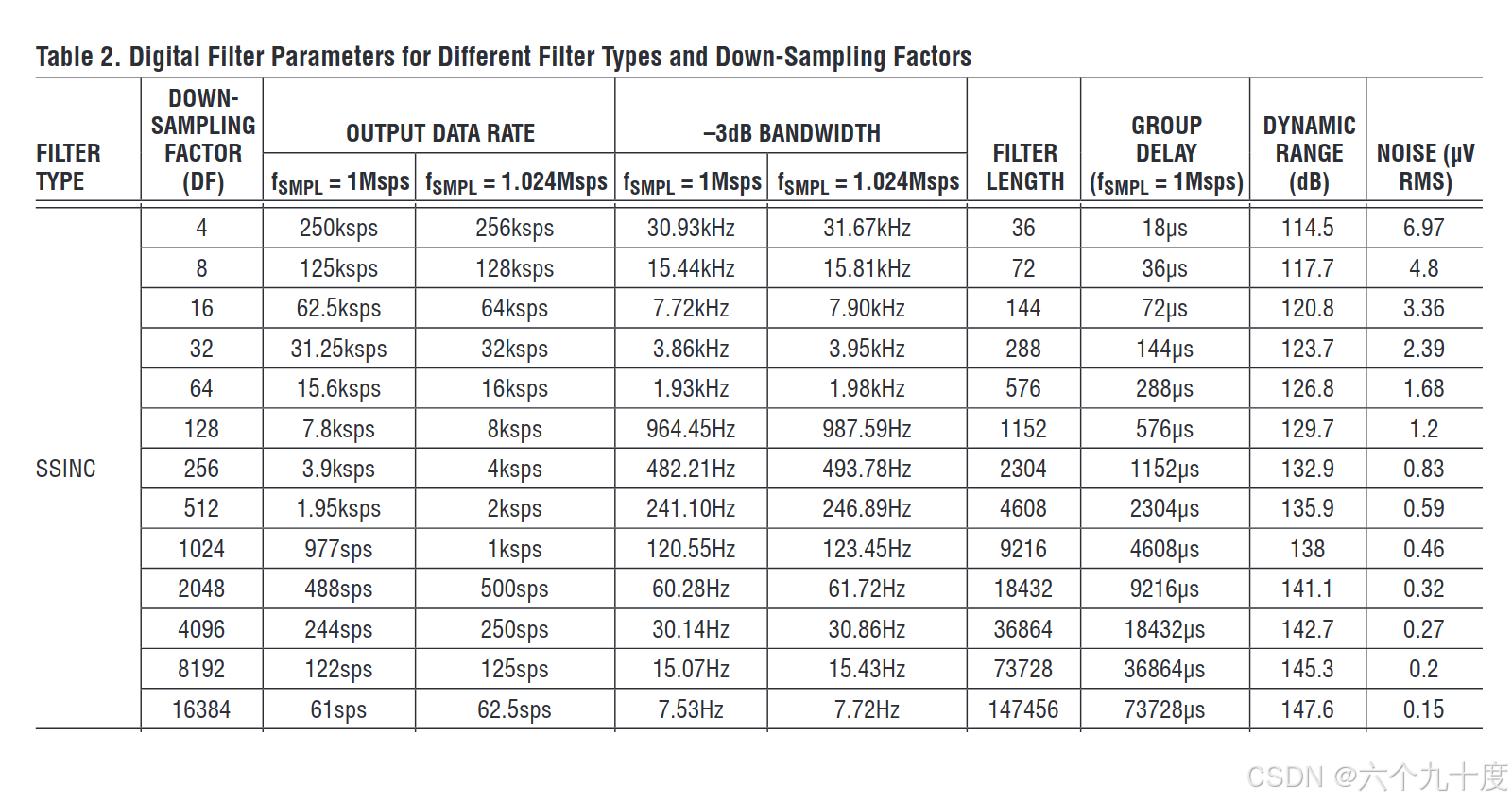

后来FPGA同事阅读datasheet才知道可能是群延迟(Group Delay)的影响,贴上SSINC滤波器的群延迟

可以看到,当DF=16384时,群延迟高达73ms,于是尝试FPGA采集group delay长的时间后再上报数据,观察数据间的关系,可以得出映射函数

c

uint32_t get_adc_group_delay(uint8_t filter, uint16_t df /*power, not exponent*/)

{

uint32_t delay = 0; // unit us

switch (filter) {

case ADC_FILTER_SINC1:

delay = (df + 2) / 2;

break;

case ADC_FILTER_SINC2:

delay = (df * 2 + 1) / 2;

break;

case ADC_FILTER_SINC3:

delay = (df * 3) / 2;

break;

case ADC_FILTER_SINC4:

delay = (df * 4 - 1) / 2;

break;

case ADC_FILTER_SSINC:

delay = (df * 9) / 2;

break;

case ADC_FILTER_FLAT:

delay = (140 * (df / 4)) / 2;

break;

case ADC_FILTER_AVG:

delay = df / 2;

break;

default:

break;

}

return delay;

}可以看出,SSINC滤波器是9个采样点滤出1个点,至于为啥要除以2,先不管。

实测发现问题有改善,但仍未彻底解决。

Settling Time

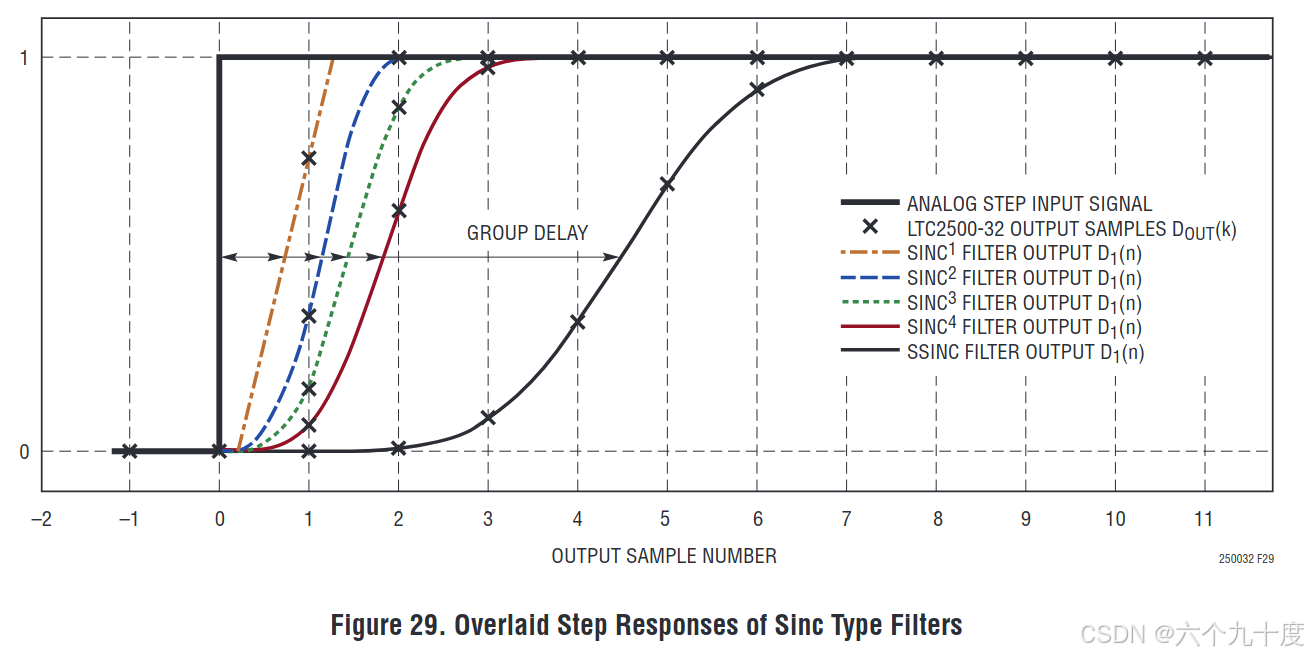

翻datasheet,发现图29

可以看到,模拟信号(最左侧的黑色粗实线)从0变成1时,不同滤波器的输出从0变成1所需要的采样点数是不一样的,SSINC至少需要7个,稳妥起见,我选择了9,相当于删掉了群延迟公式里的除以2。

结果

将群延迟计算公式调整后,实测没再出现过问题。

猜测

除以2可能是因为群延迟的定义吧?

Group delay of the digital filter is defined to be the delay to the center of the impulse response是center不是end