目录

[4. 倒装芯片布局规划](#4. 倒装芯片布局规划)

[4.1 外围 IO 引脚布局与芯片尺寸设置](#4.1 外围 IO 引脚布局与芯片尺寸设置)

[4.2 bump创建与分配](#4.2 bump创建与分配)

[4.2.2 bump分配](#4.2.2 bump分配)

[4.2.3 分配中的端口编号方法](#4.2.3 分配中的端口编号方法)

[4.3 bump分配优化](#4.3 bump分配优化)

[4.3.1 自动bump分配优化](#4.3.1 自动bump分配优化)

[4.3.2 手动bump分配优化](#4.3.2 手动bump分配优化)

[4.4.3 使用bump分配约束](#4.4.3 使用bump分配约束)

[五、Innovus 中电源 / 地焊盘的实操步骤](#五、Innovus 中电源 / 地焊盘的实操步骤)

摘要:本文详细介绍了Innovus工具中倒装芯片的布局规划流程,重点阐述了外围IO引脚布局、bump创建与分配优化方法。在IO布局阶段,提供了三种方式:加载IO文件、读取布局规划文件或自动布局。bump创建支持多种阵列模式,分配过程包括自动/手动信号分配和电源/地网络分配。优化方法包含自动全局优化、手动交换信号和使用约束文件进行精确控制,其中约束文件支持端口筛选、网络分类和焊盘-bump比例设置等高级功能。最后给出了电源/地焊盘的具体实现步骤,包括bump创建、网络绑定和RDL层布线。整个流程强调约束驱动的优化策略,以实现高效的倒装芯片布局。

4. 倒装芯片布局规划

4.1 外围 IO 引脚布局与芯片尺寸设置

在 Innovus 中启动设计后,GUI 初始显示的布局中,芯片 / core 区域内无焊盘(PAD)、hard macro或stand cell。

在设置芯片尺寸前,建议先布局设计中的外围 IO 焊盘 ------ 因为自动焊盘布局会改变芯片尺寸。用户有三种选择:

-

读取 IO 文件(loadIoFile):由布局规划架构师或封装工程师提供。该文件通常基于数字实现的初步研究或原型设计生成;封装工程师提供的 IO 布局则受bump / 焊球布线约束驱动,而焊球位置也可能受 PCB 约束影响。-----可以通过allergo 中摆好bump后转换为IO file 导入innovus;或者可以通过在innovus 中creat bump后保存IO file,继续load IO file 在innovus的文件中;

-

加载布局规划文件(loadFPlan) :由布局规划架构师提供,可通过该命令从文件中加载焊盘与硬核宏。核心功能是从外部布图规划文件(通常是

.fplan格式)中加载预先定义的 IO 焊盘位置、芯片边界、bump阵列布局、电源规划区域等信息,避免手动逐个调整 IO / bump位置,提升布图规划的效率和准确性。 -

自动外围 IO 焊盘布局(placePIO):此时可利用 Innovus 的自动焊盘布局功能生成初始焊盘环。Innovus 支持区域型或外围型 IO 布局,对于外围 IO,还支持多环布局等高级功能(可在该步骤前后定义)。

假设后端工程师的常见场景:数字实现不受架构师或封装工程师的约束,此时用户可执行placePIO命令,该命令会完成初始随机布局,后续可进一步优化。

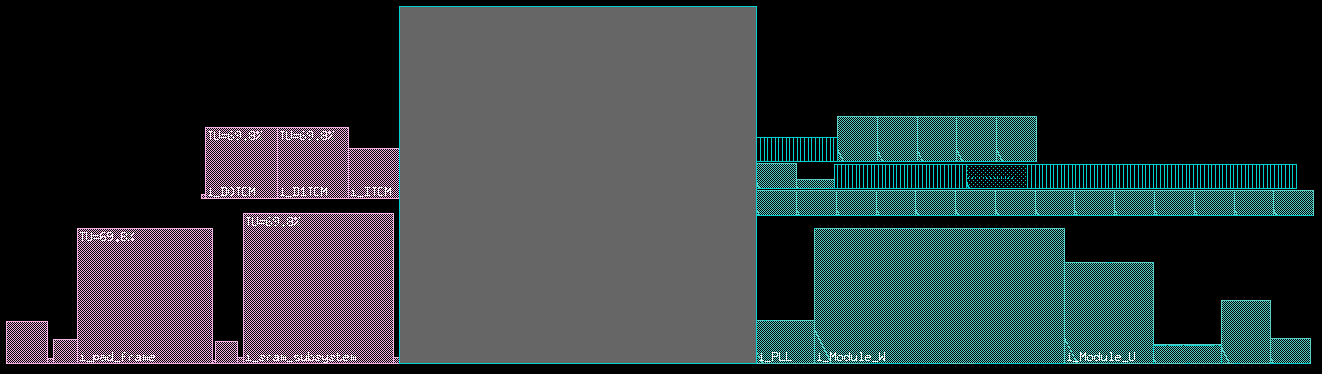

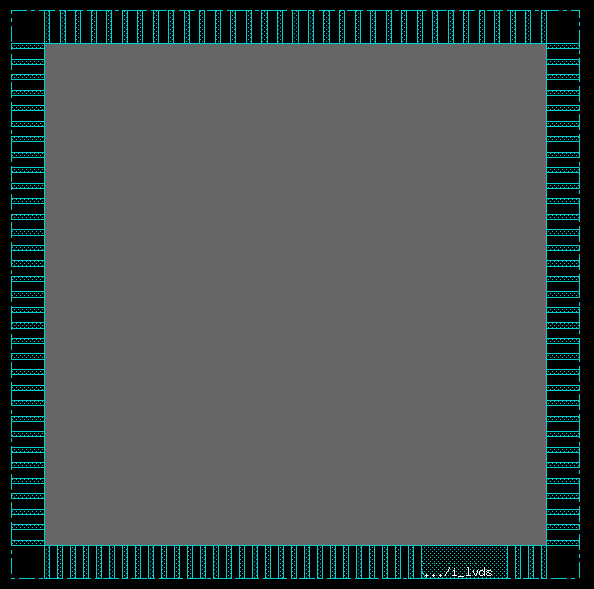

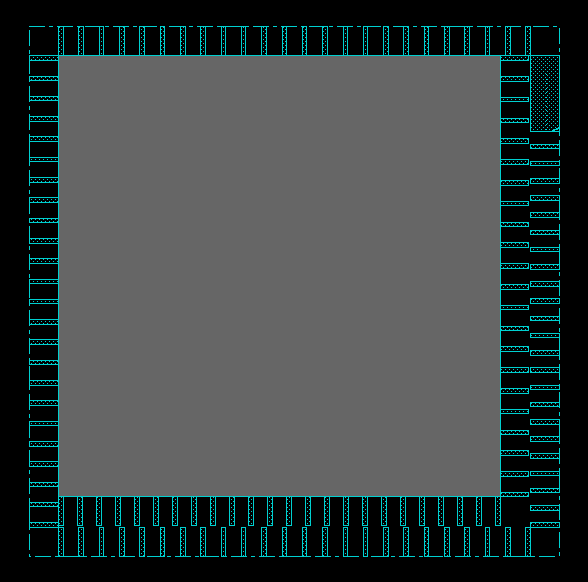

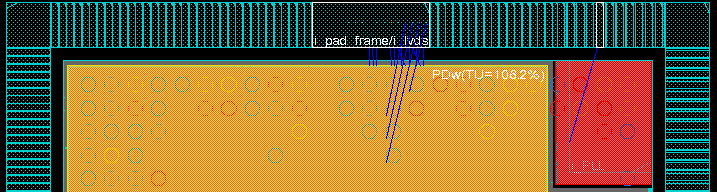

执行placePIO命令后,结果如下所示:

下图展示了高度不同的非对称环与 IO 焊盘。

工具支持创建 IO rows 以放置 IO 焊盘,用户可定义 IO row实现更定制化的焊盘布局。需在执行placePIO前通过**createIoRow** 命令创建 IO 行,placePIO会将 IO 焊盘分配到 IO 行中;用户也可执行snapFPlanIO --toIoRow命令实现自动对齐。

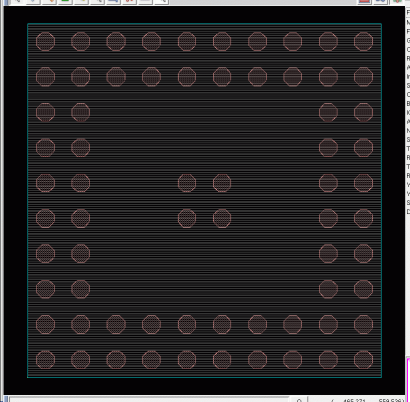

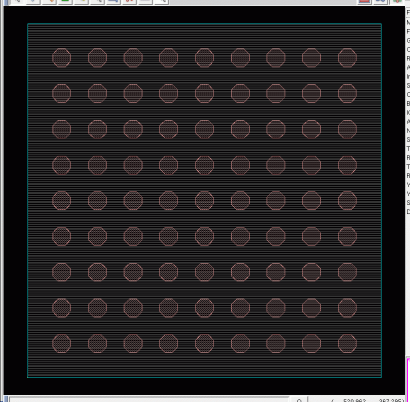

(a)

(b)

图(a)显示 IO 行流程中执行placePIO后的结果,IO 焊盘未对齐到 IO 行位点;执行snapFPlanIO --toIoRow后,IO 焊盘自动对齐,如图(b)所示。

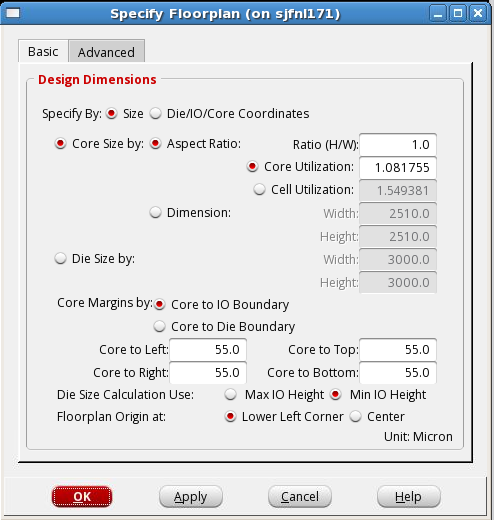

IO 焊盘布局完成后,用户可设置芯片尺寸:

通过下拉菜单 "Floorplan-> Specify Floorplan" 操作。在上述表单中,用户可根据市场或客户需求指定芯片尺寸;工具也可根据预期的最终利用率推导芯片尺寸。设计者可指定核心区域与 IO 边界的间距 ------ 该间距(在多 IO 环场景下为核心区域与内层 IO 焊盘环的间距)可用于在核心布局区域周围布电源线环。

此时工程师可执行以下操作:

-

若初始设计无物理 IO 焊盘(如电源与地 IO 焊盘),可通过

addIoInstance命令添加,电源 / 地 IO 的数量取决于芯片的预估功耗。 -

推荐步骤:通过同一命令

addIoInstance添加角落单元。→ 在此流程阶段,不建议添加 IO 填充单元 ------ 因为 IO 焊盘可能会被移动,其布局还需优化。 已添加的角落单元与电源 / 地焊盘

已添加的角落单元与电源 / 地焊盘 -

根据硬核宏布局调整 IO 焊盘位置:设计可能对模拟模块(如 PLL 或 ADC)有特定布局要求,这最终会影响部分 IO 焊盘的位置。手动布局后,需将这些焊盘与硬核宏(HM)设为固定状态(执行

setInstancePlacementStatus --name <IO名称> -status fixed);其余焊盘仅完成初步布局,后续可基于bump 分配进行自动优化。 硬核宏驱动 IO 焊盘布局的示例

硬核宏驱动 IO 焊盘布局的示例

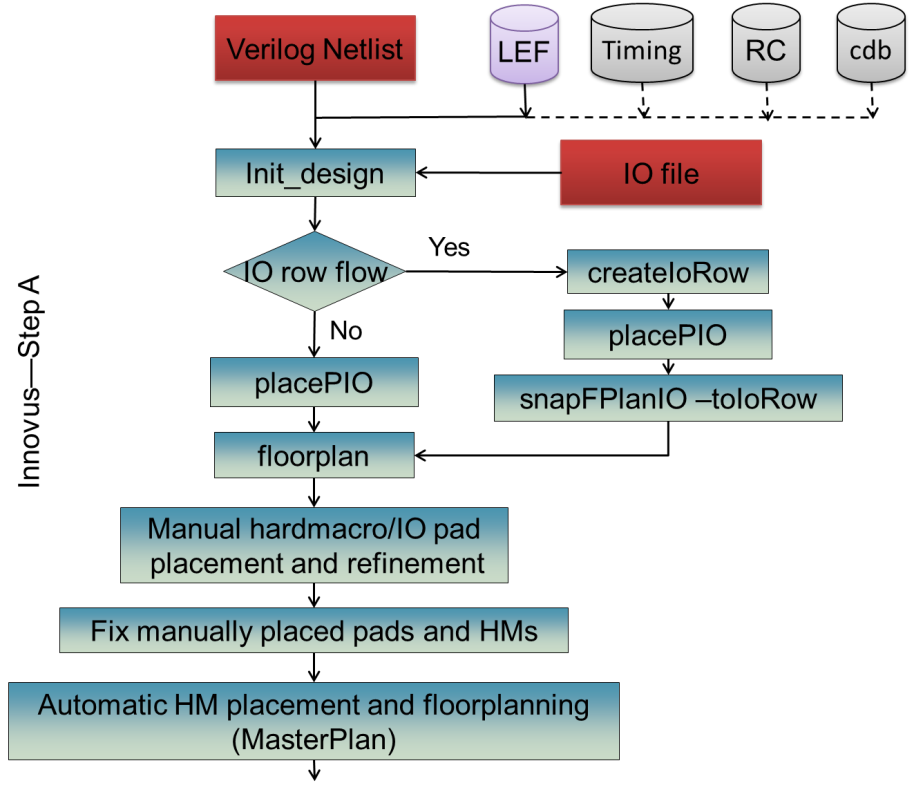

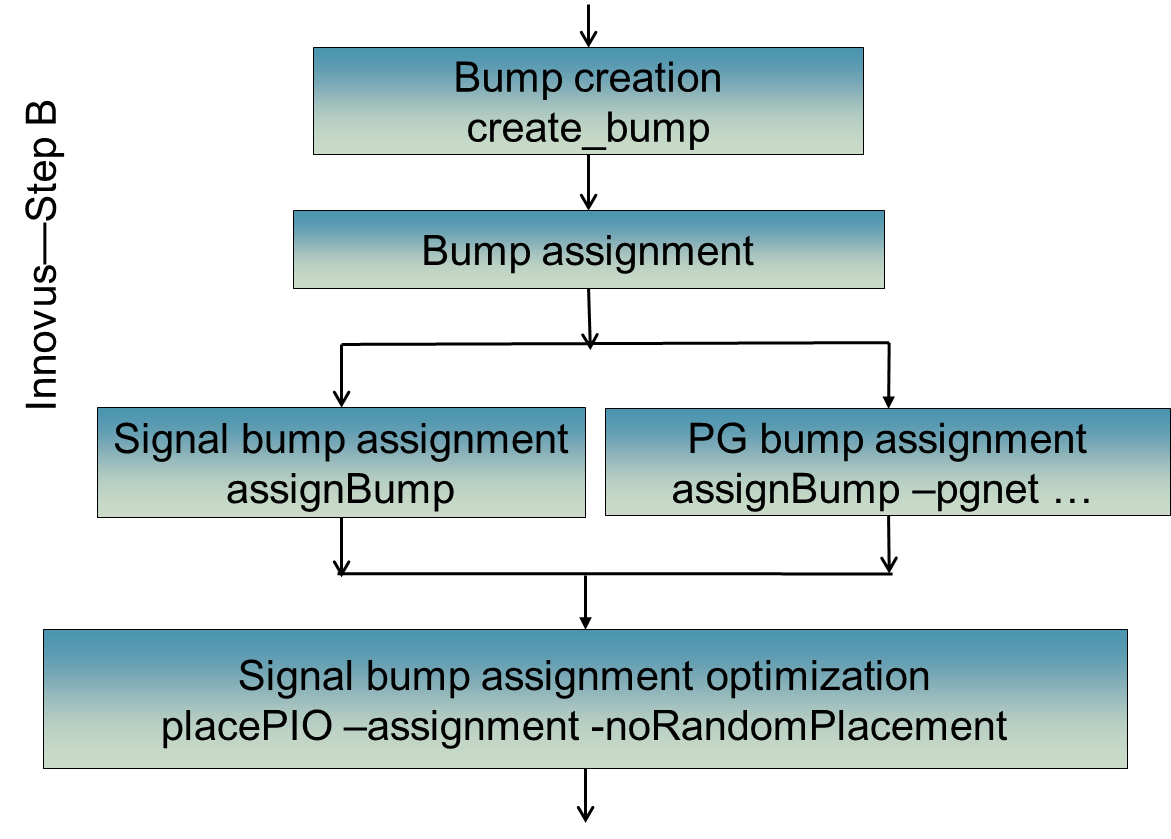

以下是实现的流程:

注意:

-

需将新的电源与地焊盘分配到正确的电源 / 地网络,用户必须创建并应用全局网络连接 ------ 否则倒装芯片路由器无法将这些焊盘的网络布线到指定bump。

-

全局网络连接可通过 GUI(电源(Power)-> 连接全局网络(Connect Global Nets))、命令行(

globalNetConnect)或读取 CPF 文件(load_power_intent -cpf)实现。

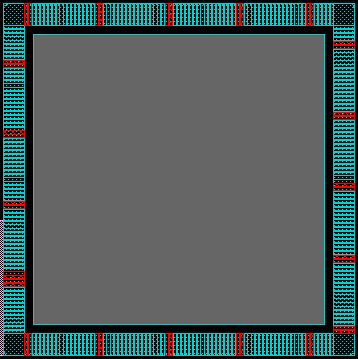

完成以上步骤后,设计中的所有硬核宏均已布局并固定;IO 焊盘大部分固定,但布局仍有一定优化空间。

4.2 bump创建与分配

倒装芯片需要焊料bump以连接到封装基板,bump生成通常分为两步:布局与信号分配。

4.2.1bump创建

在 Cadence 工具中,用户可通过create_bump命令创建单个bump或bump阵列,具体方式包括:

通常bump以固定间距的规则图案创建,create_bump命令支持以下芯片内的bump图案:

-pattern_full_chip(全芯片图案)-pattern_side {side width}(侧边图案)-pattern_array {row column}(阵列图案)-pattern_ring width(环形图案)-pattern_center {row column}(中心图案)

create_bump是一个灵活的命令:前提条件必须将bump cell的lef 文件load 到innovus 数据库里面来;

-

创建单个bump:

create_bump -cell <单元名称> -loc <x y> -

在同一布局中创建多种类型的bump阵列(支持不同形状的bump),仅需确保bump单元名称有效(取自 LEF 文件)。

外围矩阵 + 核心、矩阵与交错bump布局示例

注意:

- 不同bump图案可在同一布局中共存。

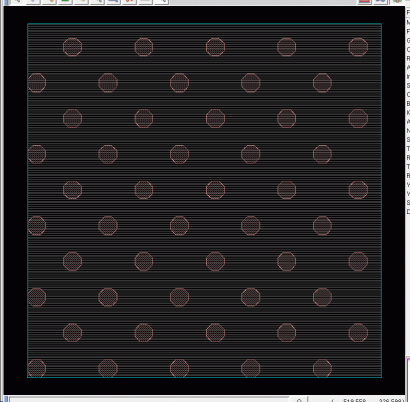

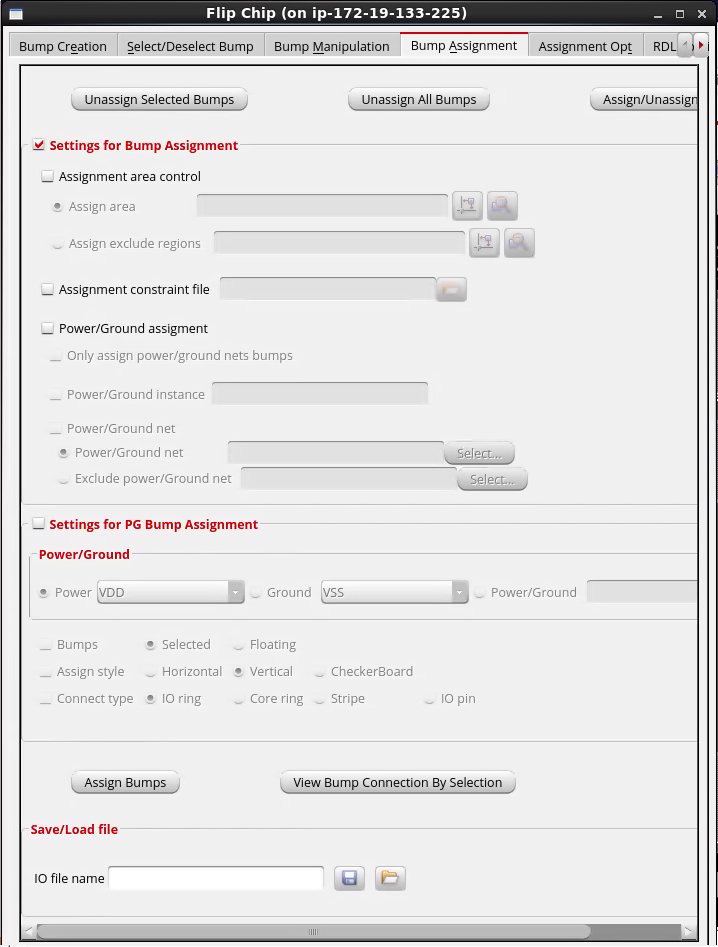

bump创建也可通过 GUI 实现:工具(Tool)-> 倒装芯片工具箱(Flip Chip Toolbox)-> bump创建(Bump Creation),效果与create_bump命令一致。bump创建 GUI 表单如下所示:

创建bump 阵列时,若bump与其他bump(基于bump几何形状)重叠,或bump被放置在芯片区域外,工具会发出警告且不创建该bump;bump阵列不会检测硬核宏 LEF 中的布线阻挡或障碍物。deleteBumps命令的--overlap_blockages与--overlap_macros选项可用于信号分配前 "清理" bump布局。

Bump 的坐标和阵列间距需与封装设计匹配,避免后续封装时出现 Bump 重叠或间距不足的问题。

信号 Bump 必须指定 -type signal,PG Bump 必须指定 -type power/ground,否则后续分配命令无法识别,导致电气连接错误。

创建后可使用以下命令验证:

tcl

list_bumps # 列出所有已创建的 Bump,包含名称、类型、坐标、数量

show_bumps # 可视化显示 Bump 的位置和分布场景 1:创建单个信号 Bump

tcl

# 创建单个信号 Bump,名称 SIG_Bump_01,中心坐标 (100, 200),尺寸 60×60μm,图层 metalRDL

create_bump -type signal -name SIG_Bump_01 -location {100 200} -size {60 60} -layer metalRDL场景 2:创建 PG Bump 阵列(电源 / 地)

tcl

# 创建电源 Bump 阵列,名称 VDD_Bump_Array,起始坐标 (50, 50),间距 100×100μm,x/y 方向各 10 个

create_bump -type power -name VDD_Bump_Array -array {50 50 100 100 10 10} -layer metalRDL

# 创建地 Bump 阵列,名称 VSS_Bump_Array,与电源阵列交错排列

create_bump -type ground -name VSS_Bump_Array -array {100 100 100 100 10 10} -layer metalRDL场景 3:基于 LEF 宏单元创建 Bump

tcl

# 前提:已加载包含 CLASS COVER BUMP 类型宏单元 BUMPCELL 的 LEF 文件

# 创建 Bump 时,自动使用 BUMPCELL 的尺寸和图层,无需手动指定 -size 和 -layer

create_bump -type signal -name SIG_Bump_Array -array {200 200 80 80 8 8}当前verifyGeometry不会高亮bump与布线阻挡的重叠,需先分配(提交)bump,verifyGeometry才会标记短路违规。在倒装芯片设计实现后,删除未分配的bump是常规操作。

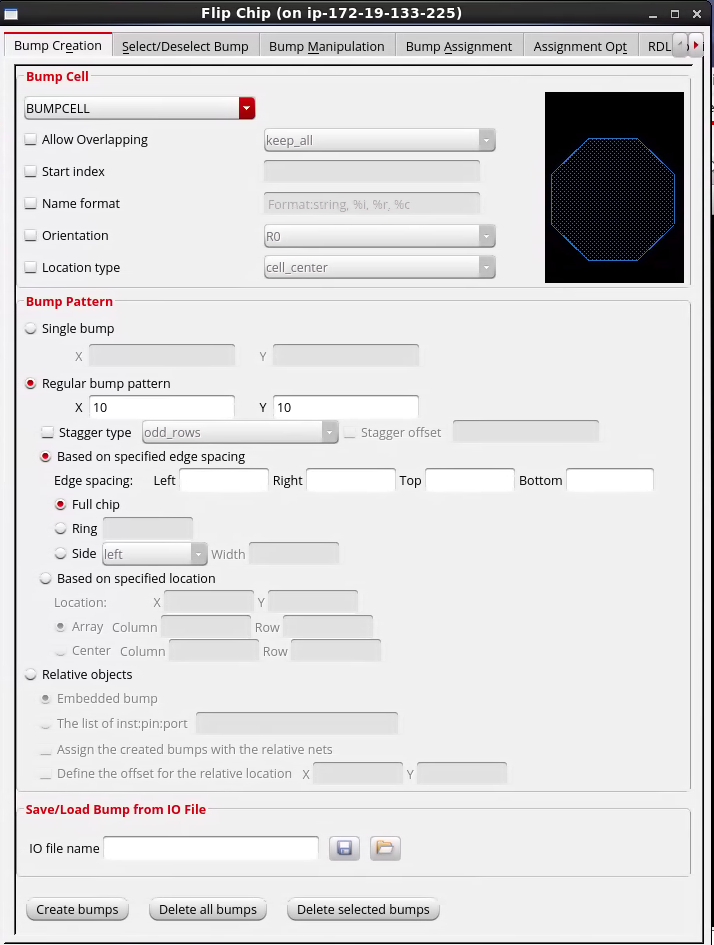

bump有四种位置类型,create_bump命令支持指定创建bump时使用的位置类型:

-

bump单元中心

-

bump单元左下角位置:可通过bump属性编辑器或命令

dbGet [dbGet top.bumps.name $Bump_name -p].pt获取 -

bump几何形状( bounding box)中心:可通过命令

dbGet top.bumps.bump_shape_center获取 -

bump几何形状( bounding box)左下角位置:可通过命令

dbGet top.bumps.bump_shape_bbox获取

从 15.2 版本开始,bump布局支持撤销操作:在bump布局尝试中,执行create_bump后点击撤销按钮(或执行undo命令),bump布局会恢复到create_bump前的状态;点击重做按钮(或执行redo命令),则会重新应用create_bump的修改。

同理,执行deleteBumps后点击撤销,deleteBumps的修改会被取消,且以下bump属性会恢复:

- 名称

- 位置

- 端口号属性

- 固定状态

- 布局状态

点击重做后,bump布局会恢复到撤销前的状态。

4.2.2 bump分配

Bump 分配是倒装焊流程的核心环节 ,分为 信号 Bump 分配 和 PG Bump 分配 两类,对应不同的命令,且必须基于带 CLASS BUMP 属性的有效端口。

bump创建完成后,用户可分配信号bump与电源 / 地(PG)bump。

1. 分配的前提条件

-

已加载 LEF 文件 :包含

CLASS PAD AREAIO(IO 焊盘)、CLASS BLOCK(硬核宏)、CLASS COVER BUMP(Bump 宏),且 IO 焊盘 / 硬核宏的端口已添加CLASS BUMP属性。 -

已加载 网表文件:包含 IO 焊盘(信号 / 电源 / 地)的实例化,且网表与 LEF 名称、引脚匹配。

-

已创建 Bump 实例 :通过

create_bump生成信号 Bump 和 PG Bump。 -

已完成 布图规划 :IO 焊盘已放置(

loadFPlan/loadIoFile/placePIO),Bump 已创建在正确位置。

2. 信号 Bump 的分配(assignBump / assignSigToBump)

适用于 CLASS PAD AREAIO 类型的信号 IO 焊盘 和 CLASS BLOCK 类型的硬核宏信号端口 ,分为自动分配 和手动分配两种方式。

| 分配方式 | 命令 | 适用场景 | 优势 |

|---|---|---|---|

| 自动分配 | assignBump |

信号 IO 数量多,对分配顺序无特殊要求 | 效率高,无需手动干预 |

| 手动分配 | assignSigToBump |

对特定信号的 Bump 分配有严格要求(如高速信号、关键信号) | 精准控制,满 |

对于信号分配,设计者可将信号bump自动分配给最近的 IO 焊盘(该方式通常会得到布线次优的分配结果)。

- 自动信号分配 :用户可通过

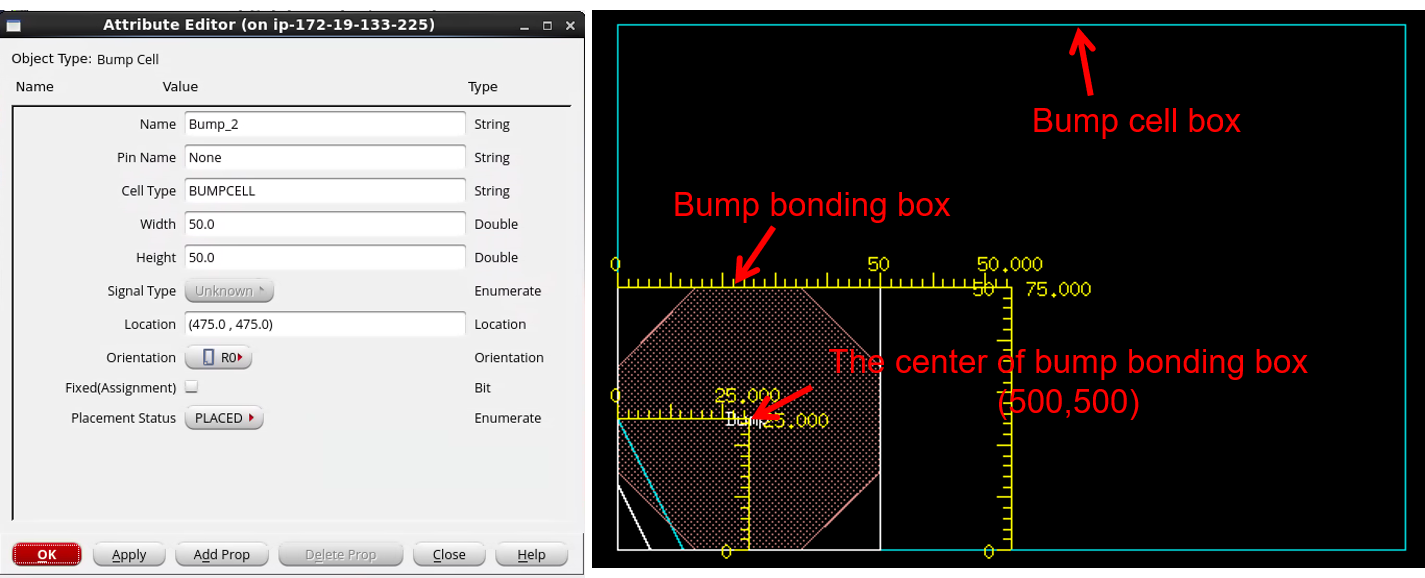

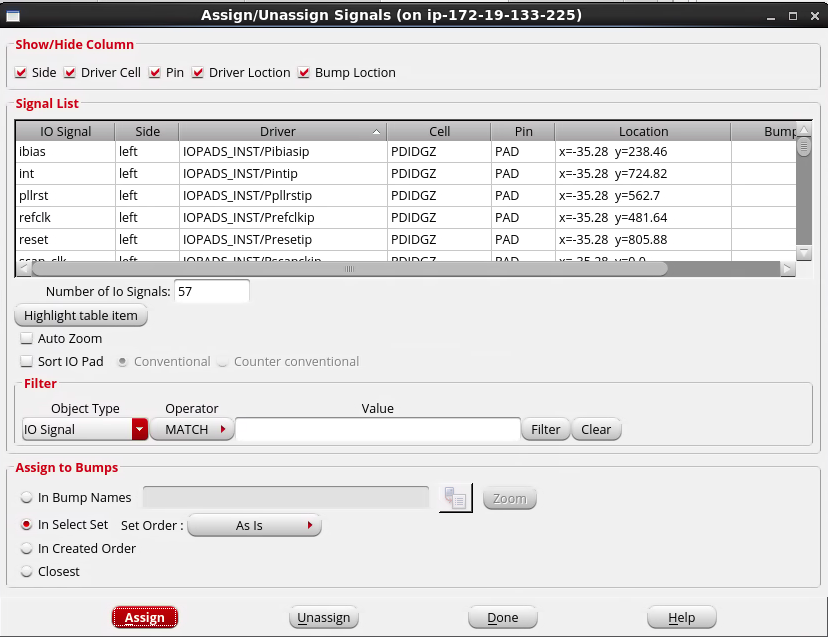

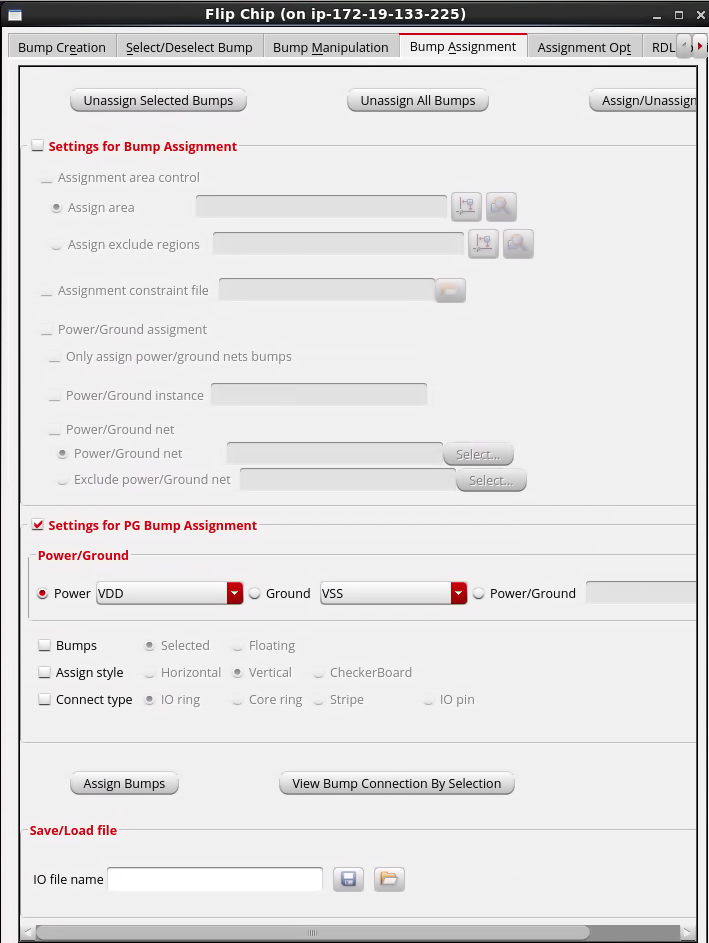

assignBump命令实现自动信号分配,该命令会基于最短距离将所有可用的倒装芯片信号分配到bump;也可通过 GUI 操作:工具(Tools)-> 倒装芯片工具箱(Flip Chip Toolbox)-> bump分配(Bump Assignment)-> bump分配设置(Setting for Bump Assignment),点击 "分配(Assign)" 按钮。GUI 表单如下所示:

自动分配:assignBump

语法:

assignBump <options>常用参数:

-io_type <type>:指定 IO 类型,pio(外围 IO)/aio(区域 IO),与你的CLASS PAD AREAIO匹配。-bump_type signal:指定分配的 Bump 类型为信号 Bump。-verbose:打印详细的分配日志,便于调试。

实操示例:

# 自动将所有 CLASS PAD AREAIO 类型的信号 IO 焊盘分配给信号 Bump,IO 类型为 AIO

assignBump -io_type aio -bump_type signal -verbose- 手动信号分配

上述 GUI 表单也支持凸点的手动分配。若要手动分配,用户可通过 "Tools-> Flip Chip Toolbox-> Bump Assignment-> Assign/Unassign Signals" 操作(默认按 "最近" 规则分配)。用户也可输入bump 名,或从列表中选择信号名,再在布局 GUI 中选择一个bump,或选择 "按创建顺序(In Created Order)",之后点击 "分配(Assign)" 按钮即可。

用户也可输入assignSigToBump命令来手动分配bump。

assignSigToBump

语法:

assignSigToBump <sig_port> <bump_name>参数说明:

<sig_port>:信号端口名称,格式为焊盘实例名/端口名(如iopad_1/PAD、Dummy_HM/A1)。<bump_name>:目标 Bump 名称(如SIG_Bump_01)。

实操示例:

# 手动将信号 IO 焊盘 iopad_1 的 PAD 端口分配给信号 Bump SIG_Bump_01

assignSigToBump iopad_1/PAD SIG_Bump_01

# 手动将硬核宏 Dummy_HM 的 A1 端口分配给信号 Bump SIG_Bump_02

assignSigToBump Dummy_HM/A1 SIG_Bump_023. 电源信号分配

适用于 CLASS PAD AREAIO 类型的电源 / 地 IO 焊盘 ,是专属命令 ,不能使用 assignBump 或 assignSigToBump,否则会导致电源分配网络(PDN)失效。

语法

assignPGBumps <options>核心参数

-power_net <power_net_name>:电源网络名称(如VDD)。-ground_net <ground_net_name>:地网络名称(如VSS)。-power_bump <power_bump_name>:电源 Bump 名称(如VDD_Bump_Array)。-ground_bump <ground_bump_name>:地 Bump 名称(如VSS_Bump_Array)。-power_pad <power_pad_port>:电源焊盘端口名称(如power_pad/VDD)。-ground_pad <ground_pad_port>:地焊盘端口名称(如ground_pad/VSS)。

实操示例

# 手动将电源焊盘 power_pad 的 VDD 端口分配给电源 Bump 阵列 VDD_Bump_Array

# 将地焊盘 ground_pad 的 VSS 端口分配给地 Bump 阵列 VSS_Bump_Array

assignPGBumps -power_net VDD -ground_net VSS -power_bump VDD_Bump_Array -ground_bump VSS_Bump_Array -power_pad4. 信号bump分配示例

对于电源 / 地(PG)分配,工具支持将 PG 焊盘与特定bump 关联,可与信号分配同时进行。用户可选择将 PG 焊盘与信号焊盘一起分配到bump,也可单独分配。

-

将 PG 焊盘与信号焊盘一起分配到bump 可通过命令

assignBump --pgnet {net_name1 net_name2...}自动完成分配,该命令会将 PG 网络与信号网络一并考虑,从全局视角基于最短距离分配合适的bump资源。

-

仅分配 PG 网络 → 工具也允许用户通过命令

assignBump --pgonly --pgnet {net_name1 net_name2...}仅将 PG 网络自动分配到bump 。→ 若设计者希望更精准地控制电源与地网络的分配,工具支持通过assignPGBumps命令或 GUI 表单进行手动分配:用户可通过 "工具(Tools)-> 倒装芯片工具箱(Flip Chip Toolbox)-> Bump Assignment-> PG bump 分配设置(Setting for PG Bump Assignment)" 访问该表单。 → 用户可通过上述表单选择bump,并将其关联到电源或地网络。

→ 用户可通过上述表单选择bump,并将其关联到电源或地网络。

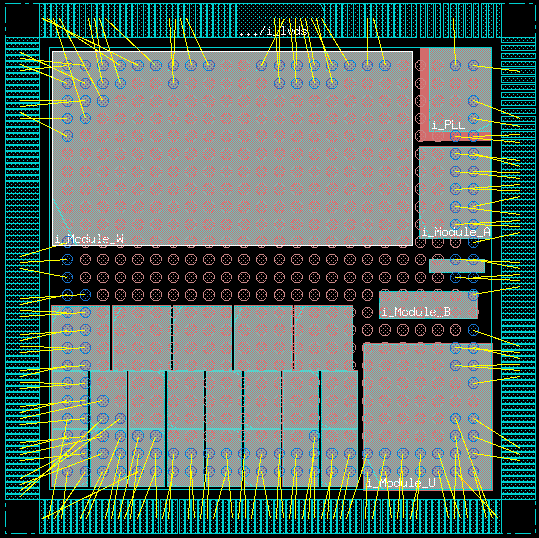

仅 PG bump分配的示例

注意:

-

bump分配后颜色会发生变化:默认情况下,已分配的信号bump为蓝色,电源bump为红色,地bump为黄色。

-

设计者可通过指定网络名与有效颜色来修改分配的颜色,这有助于跟踪特定关键网络的分配情况。读取该文本文件的命令是

ciopLoadBumpColorMapFile,以下是文件示例:Clk green Address* magenta该文件支持通配符以简化使用。

-

分配完成后,用户可使用

viewBumpConnection命令,该命令会以飞线形式显示 IO 焊盘与bump之间的连接。

-

→ 用户可使用

viewBumpConnection --bumpType signal/power命令,仅显示信号或 PG 连接的飞线。 -

→ 用户可使用

viewBumpConnection -multiBumpsToPad或viewBumpConnection -multiPadsToBumps命令开启多连接显示;若不使用这两个选项,该命令仅显示一对一连接。

4.2.3 分配中的端口编号方法

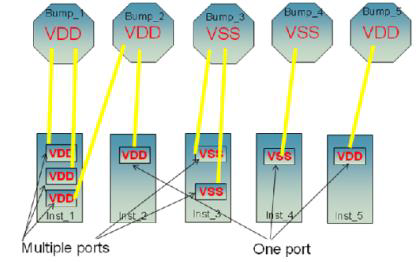

对于信号分配,通常一个网络对应一个bump,倒装芯片路由器可基于网络找到连接;但对于 PG 分配,多个 PG 焊盘会连接到同一个网络,因此用户需明确指定 PG 连接的配对关系 ------ 这意味着对于 "多焊盘对多焊盘" 的定制化模式,fcroute 需要精确知道哪些引脚或端口要路由到哪些bump。

端口编号方法允许用户在分配阶段明确指定焊盘与bump之间的连接:

-

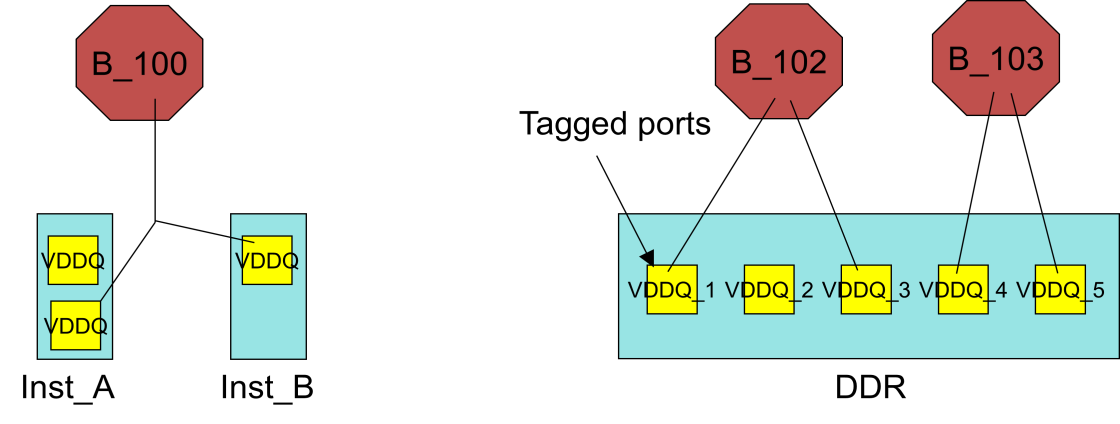

允许用户明确指定bump连接到哪个端口示例:bump B_100 连接到 Inst_A、Inst_B 的端口

-

允许用户在 "多焊盘对多bump" 场景下明确指定哪个焊盘连接到哪个bump示例:bump B_102、B103 连接到 DDR 的焊盘

用户可在 LEF 中为引脚 / 端口添加 "CLASS BUMP" 属性,以明确标识哪些引脚 / 端口用于倒装芯片的分配与route。

在 Innovus 数据库中,每个单元的端口都有唯一编号,以便在分配与route时基于实例引用这些端口:

- 编号是端口的参考标识

- 无论是否有 CLASS BUMP 属性,都会生成编号

- 仅适用于 CLASS PAD AREAIO 和 CLASS BLOCK 类型的实例

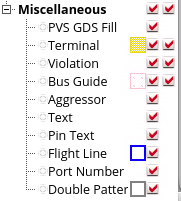

- 用户可通过 "杂项(Miscellaneous)-> 端口编号(Port Number)" 即时查看端口编号,如下所示。

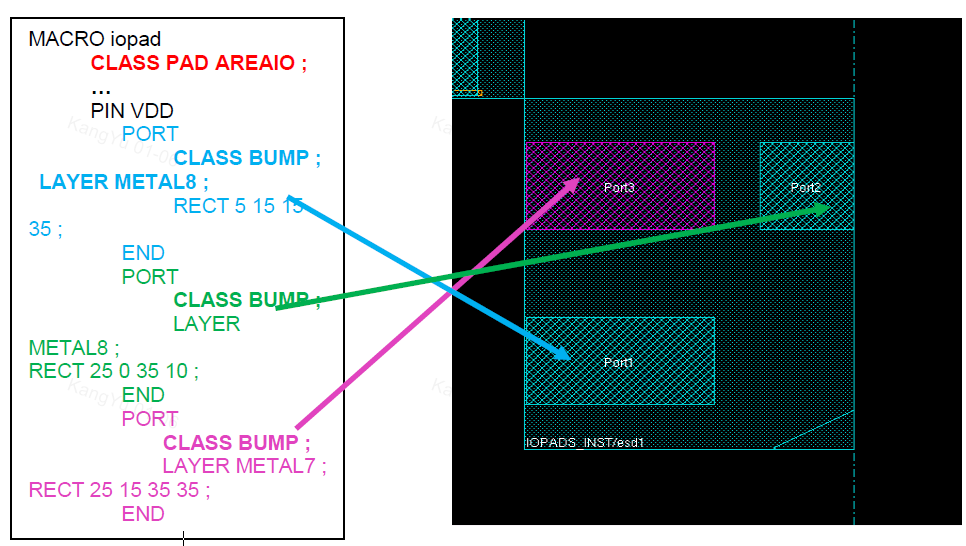

下图展示了工具如何基于 LEF 定义显示端口编号。

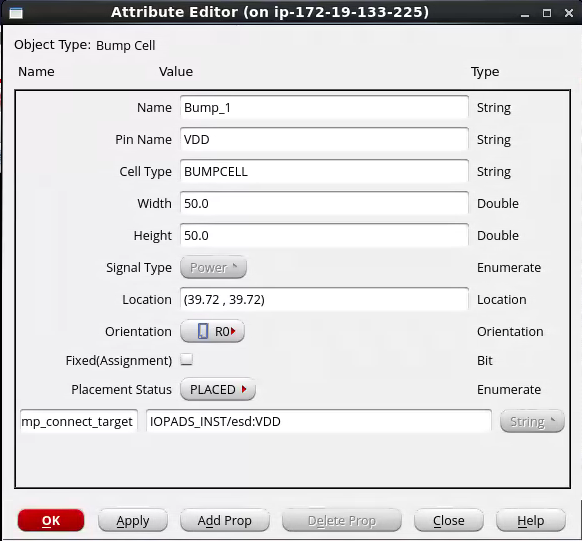

用户可使用addBumpConnectTargetConstraint命令开启自动分配的端口编号功能(适用于信号与 PG 分配),该命令会为bump 添加端口编号属性,分配完成后可打开 "bump 属性编辑器(Bump Attribute Editor)" 查看添加的属性值。属性值格式如下:

-

属性名:bump_connect_target

-

类型:string

-

属性字符串格式:inst_name 或 inst_name:pin_name 或 inst_name:pin_name:port_num。

MACRO iopad

CLASS PAD AREAIO ;

...

PIN VDD

PORT

CLASS BUMP ;

LAYER METAL8 ;

RECT 5 15 15 35 ;

END

PORT

CLASS BUMP ;

LAYER METAL8 ;

RECT 25 0 35 10 ;

END

PORT

CLASS BUMP ;

LAYER METAL7 ;

RECT 25 15 35 35 ;

END

END VDD

...

注意:在使用端口编号相关命令前,必须先开启对应的 GUI 功能;否则端口尚未编号,命令无法运行。

以下是编辑、保存 / 恢复该属性的相关操作:

| 操作类型 | 分配编辑命令 | 属性保存 / 恢复命令 | 路由命令 |

|---|---|---|---|

| 分配 | assignBump | addBumpConnectTargetConstraint | fcroute |

| 取消分配 | unassignBump | editBumpConnectTargetConstraint | - |

| 交换信号 | swapSignal | deleteBumpConnectTargetConstraint | - |

| 查看连接 | viewBumpConnection | readFlipChipProperty | - |

| 查找引脚端口号 | findPinPortNumber | writeFlipChipProperty | - |

注意:

-

需执行

setFlipChipMode -honer_bump_connect_target_constraint true命令,为倒装芯片fcroute开启端口编号功能。 -

可通过

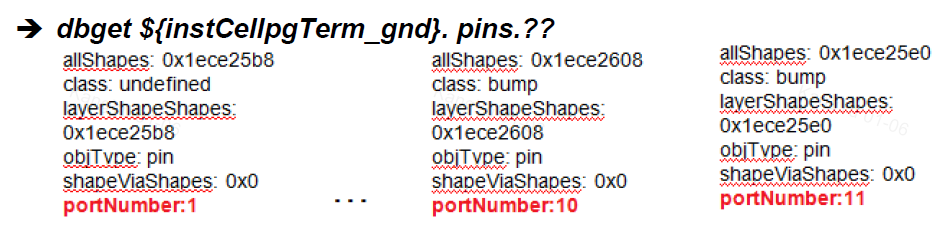

dbGet命令获取引脚端口号:→dbget selected.instTerms.cellTerm.pins.?(返回内容包含:pin、allShapes、class、layerShapeShapes、objType、shapeViaShapes、portNumber)→dbget ${instCellpgTerm_gnd}. pins.portNumber(返回示例:1 2 3 4 ... 10 11)→dbget ${instCellpgTerm_gnd}. pins.??

4.3 bump分配优化

工具提供三种bump分配优化方法:

- 自动优化

- 手动优化

- 使用bump分配约束

4.3.1 自动bump分配优化

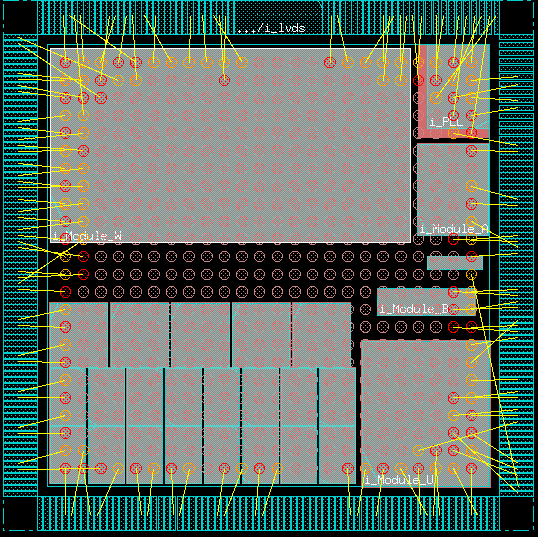

在当前流程阶段,电源与地bump已完成分配,用户可能也已将部分关键信号bump分配到其 IO 焊盘附近。其余焊盘基于最短距离分配到bump,但这种方式在某些情况下并非路由的最优结果。此时 Innovus 可通过命令placePIO --assignBump -noRandomPlacement优化bump分配,该命令会调用全局倒装芯片路由器以获得最优的routing 结果。

上述命令会遵循bump分配的固定属性,可通过setBumpFixed命令指定固定bump ------ 注意该约束会影响设计的整体可route。

如前所述,**bump与 IO 焊盘的布局优化算法会调用全局倒装芯片路由器以获得最优布局;**提前提供约束信息能为工具提供更真实的场景,从而得到更好的结果。影响bump与 IO 焊盘布局算法的约束列表如下:

-

FIXNETPAD语法:

FIXNETPAD net_name_list END FIXNETPAD作用:与指定网络关联的所有焊盘都会被固定。

-

FIXPAD语法:

FIXPAD pad_name_list END FIXPAD作用:列表中的所有焊盘都会被固定。

-

FIXPADSIDE语法:

FIXPADSIDE {EAST WEST SOUTH NORTH} pad_name_list END FIXPADSIDE作用:列表中所有焊盘的侧边会被固定为指定方向。

-

FIXNETPADSIDE语法:

FIXNETPADSIDE {EAST WEST SOUTH NORTH} net_name_list END FIXNETPADSIDE作用:与指定网络关联的所有焊盘的侧边会被固定为指定方向。

-

GROUPNET语法:

GROUPNET net_name_list END GROUPNET作用:工具会尝试将与指定网络关联的分组焊盘放置在一起。

-

GROUP语法:

GROUP pad_name_list END GROUP作用:工具会尝试将分组的焊盘放置在一起。

-

FIXBUMP语法:

FIXBUMP net_name_list END FIXBUMP作用:与指定网络关联的所有bump都会被固定。

-

BUMPREGION语法:

BUMPREGION AREA x1 y1 x2 y2 net_name_list END AREA END BUMPREGION作用:与指定网络关联的所有bump会被限制在指定区域内。

-

PAIR语法:

PAIR net_name pad_name_list bump_name_list END PAIR作用:基于网络指定bump与焊盘之间的连接关系。

这些约束可通过setFlipChipMode --constraintFile命令提供给工具。完成此步骤后,设计的bump分配已优化;若 IO 焊盘不允许移动,则设计可进入 RDL(重分布层)routing 阶段。

以下是实现的流程:

4.3.2 手动bump分配优化

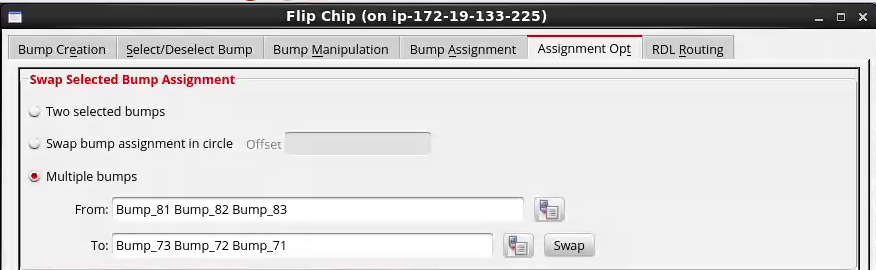

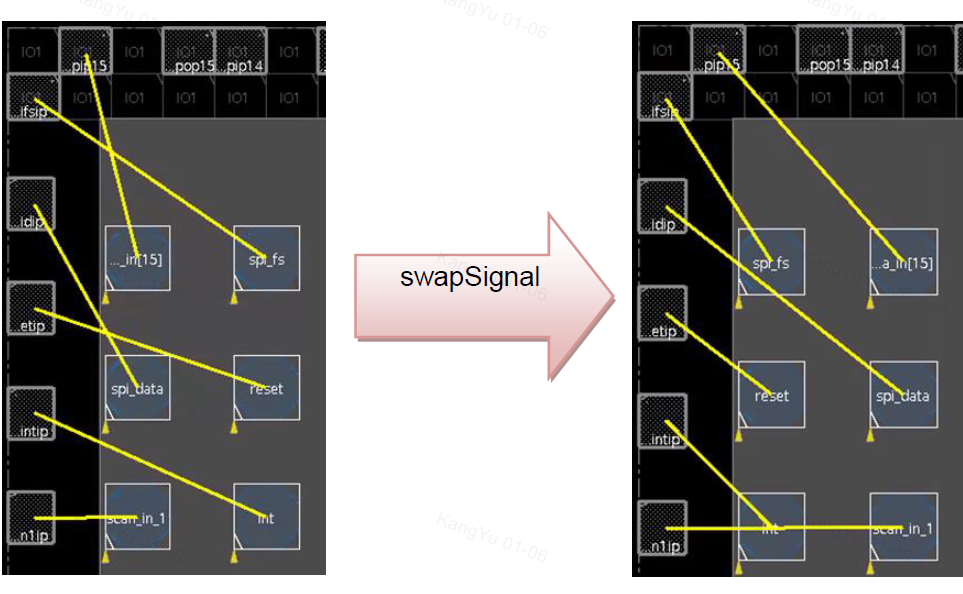

若设计者需要对已分配的bump进行小规模 ECO(工程变更),可使用swapSignal命令,或通过 "工具(Tools)-> 倒装芯片工具箱(Flip Chip Toolbox)-> 分配优化(Assignment Opt.)" 操作。

下图是一个示例:

交换信号

注意:

-

该功能支持多bump之间的交换。

-

若bump已完成route,交换信号操作不会交换其分配关系;设计者需先使用

editDelete命令删除导线。

4.4.3 使用bump分配约束

用户也可使用约束文件对bump分配进行筛选(针对焊盘引脚的端口),可通过assignBump -constraint_file选项加载bump分配约束文件。

目前支持以下类型的bump分配约束:

-

SHARE_FIND_PORT 约束:用于筛选不必要的端口语法:

SHARE_FIND_PORT PIN pin_name_list MACRO macro_name_list LAYERS top_layer[: bottom_layer] GEOMETRY_SHORT_EDGE min_value [:max_value] GEOMETRY_LONG_EDGE min_value [: max_value] net_name_list END SHARE_FIND _PORT该约束可帮助找到特定端口,但 LEF 文件中带有 CLASS BUMP 属性的端口优先级更高 ------ 即 SHARE_FIND_PORT 约束无法筛选 LEF 中带有 CLASS BUMP 的端口。

→ 必须指定网络名,且至少指定 LAYERS、GEOMETRY_SHORT_EDGE、GEOMETRY_LONG_EDGE 中的一个参数,以筛选不必要的引脚端口。

-

→ PIN pin_name_list

-

✓ 指定与目标网络连接的约束引脚列表。

-

✓ 可选;若未指定,指定网络的约束会作用于倒装芯片设计的所有可用引脚端口。

-

✓ 支持通配符匹配。

-

→ MACRO macro_name_list

-

✓ 指定其引脚与目标网络连接的约束宏列表。

-

✓ 可选;若未指定,指定网络的约束会作用于倒装芯片设计的所有可用宏。✓ 支持通配符匹配。

-

→ LAYERS top_layer[: bottom_layer]

-

✓ 指定与目标网络连接的引脚所在的层或层区域。

-

✓ 层名需支持 LEF 中的层 ID 与层名。

-

→ GEOMETRY_SHORT_EDGE min_value [:max_value]

-

✓ 指定与目标网络连接的引脚几何形状的短边长度值或范围;若仅指定一个值,表示短边长度等于该值;否则表示短边长度在 min_value 与 max_value 之间。

-

✓ 单位为微米。

-

✓ CGEOMETRY_SHORT_EDGE 表示短边长度。

-

✓ assignBump会忽略短边长度不符合规则的几何形状。

-

✓ 示例:若 VDD 引脚有以下不同端口:

- port1:5x25

- port2:15x10

- port3:5x5

- port4:10x20

- port5:15x25

若约束文件指定GEOMETRY_SHORT_EDGE 10:20,则 port2、port4、port5 可作为分配候选;若指定 GEOMETRY_SHORT_EDGE 5,则 port1、port3 可作为分配候选。

→ GEOMETRY_LONG_EDGE min_value [: max_value ]

✓ 指定与目标网络连接的引脚几何形状的长边长度值或范围;若仅指定一个值,表示长边长度等于该值;否则表示长边长度在 min_value 与 max_value 之间。

✓ 单位为微米。

✓ GEOMETRY_LONG_EDGE 表示长边长度。

✓ assignBump 会忽略长边长度不符合规则的几何形状。

→ net_name_list

✓ 指定网络列表,为必填参数。

✓ 支持通配符匹配,也支持 @signal、@power、@ground。

以下是 SHARE_FIND_PORT 约束的示例:

SHARE_FIND_PORT

PIN VDD

MACRO VDD_PAD DDR_VDD_PAD

LAYERS metalALP

GEOMETRY_SHORT_EDGE 20:25

GEOMETRY_LONG_EDGE 15

@power

END SHARE_FIND _PORT若该约束在 assignBump 的约束文件中指定,则仅满足以下条件的引脚可用于bump分配,assignBump 会忽略所有不符合条件的bump:→ 连接到设计中的电源网络→ LEF 中的名称为 VDD→ 属于宏 VDD_PAD 或 DDR_VDD_PAD→ 位于 metalALP 层→ 短边长度在 20 到 25 微米之间,且长边长度等于 15 微米。

-

ASSIGN_ANALOG_PG_NETS 约束 :指定哪些信号网络是模拟 PG 网络语法:

ASSIGN_ANALOG_PG_NETS net_name_list END ASSIGN_ANALOG_PG_NETS→ net_name_list✓ 指定在 LEF 或网表中被定义为信号网络、但实际是模拟 PG 网络的列表。✓ 支持通配符匹配。

注意:✓ 通过 ASSIGN_ANALOG_PG_NETS 约束指定的网络仍属于信号网络,但会用于自动电源 / 地分配;assignBump 会将这些网络视为普通电源 / 地网络。a. 这些网络可作为 assignBump 命令的 - pgnet {net_list} 或 - exclude_pgnet {net_list} 选项的参数。b. 使用 assignBump -pginst {instance_list} 时会考虑这些网络。c. 这些网络会被排除在 assignBump 的信号分配之外。✓ assignBump 不会修改 ASSIGN_ANALOG_PG_NETS 中指定网络的属性;因此分配后,与这些网络关联的凸点仍为信号凸点,而非电源 / 地凸点。

-

**SHARE_IGNORE_*和 ASSIGN_IGNORE_约束*:排除特定实例、宏、引脚或网络的分配这些约束可用于排除实例、宏、引脚或网络的分配,语法因排除对象而异:

-

→ 排除实例语法:

SHARE_IGNORE_INSTANCE instance_name_list END SHARE_IGNORE_INSTANCE其中 instance_name_list 指定分配时要排除的实例列表,支持通配符。

→ 排除宏语法:

SHARE_IGNORE_MACRO macro_name_list END SHARE_IGNORE_MACRO其中 macro_name_list 指定分配时要排除的宏列表,支持通配符。

→ 排除实例引脚语法:

ASSIGN_IGNORE_INSTANCE_PIN instance_name:pin_name ... END ASSIGN_IGNORE_INSTANCE_PIN其中 instance_name:pin_name:✓ 指定要排除分配的实例引脚。✓ 支持多个参数。✓ 支持通配符。✓ ":" 前后不允许有空格。

→ 排除宏引脚语法:

ASSIGN_IGNORE_MACRO_PIN macro_name:pin_name ... END ASSIGN_IGNORE_MACRO_PIN其中 macro_name:pin_name:✓ 指定要排除分配的宏引脚。✓ 支持多个参数。✓ 支持通配符。✓ ":" 前后不允许有空格。

→ 排除网络语法:

ASSIGN_IGNORE_NET net_name_list END ASSIGN_IGNORE_NET其中 net_name_list 指定分配时要排除的网络列表,支持通配符。

-

ASSIGN_PAD2BUMP_RATIO 约束:指定每个网络、宏或实例的焊盘与凸点比例语法:

ASSIGN_PAD2BUMP_RATIO TOLERANCE net_name integer PGNET net_name ratio PGMACRO macro:pin ratio PGINST inst:pin ratio END ASSIGN_PAD2BUMP_RATIO该约束用于指定每个网络、宏或实例的焊盘与凸点比例。

→ 比例大于 1 的参数以下参数适用于焊盘与凸点比例大于 1 的场景:

-

✓ TOLERANCE net_name integer

-

✓ PGNET net_name ratio

当比例大于 1 时,assignBump 会基于每个网络的指定比例,计算 "多 PG 端口对多凸点" 的分组数,以及每个分组的最大端口数。

假设端口总数为 total_port,比例为 port_num:bump_num:

-

✓ 若 total_port 是该比例的整数倍:分组数 = total_port÷(port_num/bump_num) + 容差(TOLERANCE)

-

✓ 否则:分组数 = [total_port÷(port_num/bump_num)] + 1 + 容差

-

✓ 若 port_num 是 bump_num 的整数倍:每个分组的最大端口数 = port_num ÷ bump_num✓ 否则:每个分组的最大端口数 = [port_num ÷ bump_num] + 1

示例:若有 5 个带 VDD 的焊盘,每个焊盘的 VDD 引脚只有 1 个端口,且焊盘与bump比例为 3:2,则:分组数 = 取整 {5÷(3/2) + 0} = 4每个分组的最大端口数 = 取整 {3/2} = 2

该功能会在以下条件下尝试提供最优分配结果:

-

✓ 分组数保持不变。

-

✓ 每个分组的端口数不超过最大端口数。

比例大于 1 的参数说明:

-

✓ TOLERANCE net_name integero 指定特定网络的容差值,仅支持正整数;通过该选项,焊盘 / 端口分组数会按容差值统计。o 默认值为 0。o 仅对 PGNET net_name ratio 生效。o net_name 支持通配符匹配。

-

✓ PGNET net_name ratioo 指定特定网络的比例。o net_name 支持通配符匹配。o 比例必须大于 1;若指定比例小于 1,assignBump 会发出错误信息并忽略该比例。o 若比例不是最简形式,工具会简化并发出警告。o 不同 PG 网络需单独定义比例;若为同一网络指定多个比例,assignBump 会发出警告并选择最后一个指定的比例。

示例 1:若 VDD 和 VDD0 的比例为 2:1,VSS 的比例为 3:2,语法如下:

PGNET VDD 2:1 #VDD的比例为2:1 PGNET VDDO 2:1 #VDDO的比例为2:1 PGNET VSS 3:2 #VSS的比例为3:2 PGNET VSS 3:2 #这是VSS的第二个(最后一个)比例,assignBump会发出警告并使用该比例 PGNET VSSO 1:2 #VSSO的比例小于1,assignBump会发出错误信息并忽略示例 2:

PGNET * 2:1 #assignBump命令中指定的所有PG网络的比例为2:1示例 3:在 ratio.const 约束文件中指定:

PGNET VDD 4:2 PGNET VSS 4:2执行命令:

assignBump -constraint_file ratio.const -pgnet {VDD VSS}a. 工具会先将比例简化为 2:1。b. 工具计算焊盘 / 端口分组数与每个分组的最大端口数:o 对于 VDD,端口总数(5)不是 port_num(2)的整数倍,因此:分组数 = [5÷(2/1)] + 1 + 0 = [2.5] + 1 = 2 + 1 = 3o 对于 VSS,端口总数(3)不是 port_num(2)的整数倍,因此:分组数 = [3÷(2/1)] + 1 + 0 = [1.5] + 1 = 1 + 1 = 2o VDD 和 VSS 的比例均为 2:1,且 port_num(2)是 bump_num(1)的整数倍,因此:每个分组的最大端口数 = 2÷1 = 2

多 PG 焊盘对bump的分配如下图所示。

→ 比例小于 1 的参数以下参数适用于焊盘与bump比例小于 1 的场景:

-

✓ PGMACRO macro:pin ratio

-

o 指定特定宏单元的比例。

-

o macro:pin 支持通配符。

-

o 比例必须小于 1;否则 assignBump 会发出错误信息并忽略。o 若为同一引脚指定多个比例,assignBump 会发出警告并选择最后一个指定的比例。o 选择最外层的几何形状作为目标,并将端口编号记录到 bump_connect_target 中。

示例 1:

PGMACRO DDR1:VDD 1:2 #DDR1中VDD引脚的比例为1:2 PGMACRO DDR2:VDD 1:2 #DDR2中VDD引脚的比例为1:2 PGMACRO DDR2:VDD 1:3 #这是DDR2中VDD引脚的第二个(最后一个)比例,assignBump会发出警告并使用该比例 PGMACRO DDR3:VSS 2:1 #比例大于1,assignBump会发出错误信息并忽略示例 2:

PGMACRO * 1:2 #assignBump命令中指定的所有宏的所有pg引脚比例为1:2 PGMACRO DDR1:* 1:2 #DDR1中所有pg引脚的比例为1:2 PGMACRO *:VDD 1:2 #assignBump命令中指定的所有宏的VDD引脚比例为1:2✓ PGINST inst:pin ratioo 指定特定实例的比例。

-

o inst:pin 支持通配符。

-

o 比例必须小于 1;否则 assignBump 会发出错误信息并忽略。o 若为同一引脚指定多个比例,assignBump 会发出警告并选择最后一个指定的比例。o 选择最外层的几何形状作为目标,并将端口编号记录到 bump_connect_target 中。

示例 1:

PGINST inst1:VDD 1:2 #inst1中VDD引脚的比例为1:2 PGINST inst2:VDD 1:2 #inst2中VDD引脚的比例为1:2 PGINST inst2:VDD 1:3 #这是inst2中VDD引脚的第二个(最后一个)比例,assignBump会发出警告并使用该比例 PGINST inst3:VSS 2:1 #比例大于1,assignBump会发出错误信息并忽略示例 2:

PGINST * 1:2 #assignBump命令中指定的所有实例的所有pg引脚比例为1:2 PGINST inst1:* 1:2 #inst1中所有pg引脚的比例为1:2 PGINST *:VDD 1:2 #assignBump命令中指定的所有实例的VDD引脚比例为1:2

若比例存在冲突,优先级顺序为 PGINST > PGMACRO > PGNET,示例如下:

ASSIGN_PAD2BUMP_RATIO

PGNET VDD 2:1 #VDD的比例为2:1

PGMACRO DDR:VDD 1:2 #若DDR中的VDD引脚连接到VDD,由于PGMACRO优先级高于PGNET,因此该引脚的比例为1:2

PGINST inst:VDD 1:3 #inst的宏单元是DDR,由于PGINST优先级高于PGMACRO,因此inst中VDD引脚的比例为1:3

PGNET VSS 3:1

PGINST inst1:VSS 1:3 #若inst1中的VSS引脚连接到VSS,由于PGINST优先级高于PGNET,因此该引脚的比例为1:3

END ASSIGN_PAD2BUMP_RATIOASSIGN_PAD2BUMP_RATIO 的使用说明:

o 该约束会开启 "按比例分配焊盘到bump" 的功能。

o 若与 - pgnet 一起使用,ASSIGN_PAD2BUMP_RATIO 仅对指定的 PG 网络生效。

o 若与 - exclude_pgnet 一起使用,ASSIGN_PAD2BUMP_RATIO 会忽略指定排除 PG 网络的约束。

o 若与 - pginst 一起使用,ASSIGN_PAD2BUMP_RATIO 仅对 PGMACRO 和 PGINST 指定的实例生效。

o 若与 - pgnet 和 - pginst 一起使用,ASSIGN_PAD2BUMP_RATIO 仅对 PGMACRO 和 PGINST 指定实例的指定 PG 网络生效。

o 若与 - exclude_pgnet 和 - pginst 一起使用,ASSIGN_PAD2BUMP_RATIO 对 PGMACRO 和 PGINST 指定实例的 PG 网络生效(排除指定的 PG 网络)。

o 若 - pgnet、-exclude_pgnet、-pginst 指定的对象未包含在 ASSIGN_PAD2BUMP_RATIO 中,assignBump 会发出警告并使用 1 作为比例值。

o 若未与 - pgnet、-exclude_pgnet 或 - pginst 一起使用,ASSIGN_PAD2BUMP_RATIO 会忽略所有已定义的约束。

五、Innovus 中电源 / 地焊盘的实操步骤

-

加载基础文件

read_lef ./io_pads.lef # 包含 power_pad/ground_pad(CLASS PAD AREAIO + CLASS BUMP) read_netlist ./top.v # 加载包含电源/地焊盘的网表 link_design # 链接设计,检查无"引脚不匹配""宏单元未找到"报错 -

创建 PG Bump

create_bump -type power -name VDD_Bump -array {100 200 50 50} # 创建电源凸块阵列 create_bump -type ground -name VSS_Bump -array {150 200 50 50} # 创建地凸块阵列 -

绑定电源 / 地焊盘到 PG Bump

assignPGBumps -power_net VDD -bump VDD_Bump -pad power_pad/VDD # 电源焊盘 ↔ 电源凸块 assignPGBumps -ground_net VSS -bump VSS_Bump -pad ground_pad/VSS # 地焊盘 ↔ 地凸块 -

生成 RDL 层电源条带(关键)

# 在 PG Bump 上方生成电源条带(适配倒装焊规则) addStripe -net VDD -layer metalRDL -width 10 -spacing 5 -over_bumps # 在 PG Bump 之间生成地条带 addStripe -net VSS -layer metalRDL -width 10 -spacing 5 -between_bumps -

电源 / 地 RDL 布线

fcroute -type power -designStyle pio -area {0 0 1000 1000} -incremental