目录

[四、在 Calibre 3DSTACK 规则文件中编写验证检查](#四、在 Calibre 3DSTACK 规则文件中编写验证检查)

[4.1 连通性检查(LVS)](#4.1 连通性检查(LVS))

[4.2 层间距检查(DRC)](#4.2 层间距检查(DRC))

[4.3 焊盘充分重叠检查(DRC)](#4.3 焊盘充分重叠检查(DRC))

[五、 示例:系统网表生成器流程](#五、 示例:系统网表生成器流程)

[5.1 创建新项目](#5.1 创建新项目)

[5.2 将芯片导入数据库](#5.2 将芯片导入数据库)

[5.3 将芯片导入数据库](#5.3 将芯片导入数据库)

[示例(Tcl 命令)](#示例(Tcl 命令))

[5.4 修改并添加芯片引脚](#5.4 修改并添加芯片引脚)

[示例(Tcl 命令)](#示例(Tcl 命令))

[5.5 为芯片创建布局实例](#5.5 为芯片创建布局实例)

[示例(Tcl 命令)](#示例(Tcl 命令))

[5.6 定义网连通性](#5.6 定义网连通性)

[5.7 导出完整设计](#5.7 导出完整设计)

[示例(生成的 SPICE 网表)](#示例(生成的 SPICE 网表))

[6.1 Calibre 3DSTACK+ 扩展语法示例](#6.1 Calibre 3DSTACK+ 扩展语法示例)

[6.2 开头语句](#6.2 开头语句)

[6.3 Calibre 3DSTACK 设置](#6.3 Calibre 3DSTACK 设置)

[6.4 芯片和层定义](#6.4 芯片和层定义)

[6.5 装配操作](#6.5 装配操作)

[6.6 验证规则](#6.6 验证规则)

[6.7 标准(传统)语法示例 1](#6.7 标准(传统)语法示例 1)

[6.8 标准(传统)语法示例 2](#6.8 标准(传统)语法示例 2)

[7.1 报告头](#7.1 报告头)

[7.2 绘制层、布局实例和文本层摘要](#7.2 绘制层、布局实例和文本层摘要)

[1. 重命名规则](#1. 重命名规则)

[2. 层](#2. 层)

[3. 堆叠中芯片和层布局实例的报告](#3. 堆叠中芯片和层布局实例的报告)

[4. 堆叠中定义的文本层的详细信息](#4. 堆叠中定义的文本层的详细信息)

[5. net映射](#5. net映射)

[7.3 验证结果](#7.3 验证结果)

摘要

本文详细介绍了Calibre3DSTACK工具在3D-IC设计验证中的应用。主要内容包括:

1)连通性检查(LVS)规则编写,重点说明connected命令的使用方法和多文本标签处理;

2)设计规则检查(DRC)实现,涵盖层间距检查和焊盘重叠检查;

3)系统网表生成器操作流程,从芯片导入到网连通性定义;

4)两种规则文件语法(扩展语法和传统语法)的编写示例;

5)验证报告文件格式解析。

通过具体案例演示了如何建立完整的3D-IC验证流程,包括芯片定义、装配操作、电气连接验证和物理规则检查等关键步骤,为3D-IC设计验证提供了实用指导。

四、在 Calibre 3DSTACK 规则文件中编写验证检查

LVS(版图与原理图一致性检查)和 DRC(设计规则检查)规则通过 Calibre 3DSTACK 规则文件命令编写。

4.1 连通性检查(LVS)

3D-IC 的连通性检查基于布局信息、源网表连通性、装配连接语句及附加文本执行。要验证芯片布局间的连通性,需使用 connected 规则文件命令。在 Calibre 3DSTACK 验证运行过程中,装配体中布局实例间的网连通性,会根据你通过 connect 语句指定的层堆叠设计生成。所有文本也会附加到布局引脚,并追溯到每个布局的引脚名称。若指定了源网表,工具会将原始连通性与提取的网表进行对比。。

注意

若布局中多个文本标签与一个焊盘重叠,工具会生成多文本错误 ,并选择其中一个附加到焊盘的文本标签用于连通性分析。由于所选标签可能与你的设计意图不符,因此必须检查并解决所有多文本错误,以确保布局正确。若未解决此类错误,连通性分析结果可能不准确。

前提条件

- 已完成定义层连通性。

操作步骤

-

打开

3dstack.rules规则文件。 -

在装配语句后添加以下

connected语句:connected -check_name CONNECT_PADS_TO_BUMPS \ -layer_type1 pad \ -layer_type2 bump \ -detailed -black_box \ -net_mismatch ALL \ -comment "CONNECT::INTERPOSER TO DIES CONNECTIVITY"每个规则检查必须具有唯一名称。

示例说明

-

-layer_type1和-layer_type2命令用于指定需要连接的层类型,这些类型在各个芯片的定义中声明。 -

-detailed选项会向报告文件中写入额外信息。

补充说明

也可以通过 connected ... -die1 <芯片名> 和 -die2 <芯片名> 选项指定芯片名称,来检查两个芯片之间的连通性。

-

保存规则文件。

-

继续执行《层间距检查(DRC)》。

结果

连通性规则已建立。Calibre 3DSTACK 会利用层连通性和端口形状(引脚)上的文本,确定芯片间的网连通性。若指定了源网表,工具会将从布局中提取的连通性与源连通性进行对比;若未指定源网表(不推荐 ),则必须为装配体中的芯片指定文本层,此时工具仅通过文本匹配进行对比(布局上的端口文本需保持一致)。

4.2 层间距检查(DRC)

Calibre 3DSTACK 包含多项物理检查,其工作方式与 SVRF(标准验证规则格式)间距检查类似。建议使用 Calibre 3DSTACK 内置命令 来检查间距违规。enclosure、external 和 internal 命令可提供基础的间距检查功能。

前提条件

- 已完成《在 Calibre 3DSTACK 规则文件中编写装配操作》。

操作步骤

-

打开

3dstack.rules规则文件。 -

要检查芯片间的间距,添加以下

external语句:external -check_name PAD_SPACE -layer_type1 pad \ -constraint "< 65 REGION" -comment "ERR:Placement within 65um!" external -check_name BUMP_SPACE -layer_type1 bump \ -constraint "< 65 REGION" -comment "ERR:Placement within 65um!"每个规则检查必须具有唯一名称。

-

要检查其他层(如中介层上的金属互连)的间距,指定以下命令:

external -check_name RDL_M1.1 -layer_type1 rdl \ -constraint "< 1 REGION" -comment "ERR: Spacing < 0.1um on rdl!" ... -

为每个层酌情添加

enclosure、external和internal命令。 -

保存规则文件。

-

继续执行《焊盘充分重叠检查(DRC)》。

4.3 焊盘充分重叠检查(DRC)

若芯片布局略有偏移,或芯片间焊盘的几何形状不完全匹配,焊盘可能仍保持电气连接,但可能不符合制造要求。必须检查重叠容差,以避免产生错误的连通性检查报告。

前提条件

- 已完成在 Calibre 3DSTACK 规则文件中编写装配操作》。

操作步骤

-

打开

3dstack.rules规则文件。 -

要按重叠百分比检查焊盘是否充分重叠,在装配操作后添加以下

overlap命令:overlap -check_name "OVERLAP_PAD_TO_BUMP" \ -layer_type1 pad \ -layer_type2 bump \ -constraint " < 99" -intersection \ -comment "Pad overlap must be greater than 90%!"在此示例中,若控制器与中介层焊盘的重叠率未超过 90%,则规则检查失败。

-

要按重叠面积检查焊盘是否充分重叠,使用

-by_area命令,如下所示:overlap -check_name "OVERLAP_PAD_TO_BUMP_AREA" \ -layer_type1 pad \ -layer_type2 bump \ -constraint " < 13" -intersection \ -comment "Pad overlap must be greater than 13 um^2!"在此示例中,若控制器与中介层焊盘的重叠面积未超过 13 平方微米,则规则检查失败。

-

保存并关闭规则文件。

-

继续执行《从命令行运行 Calibre 3DSTACK 验证》。

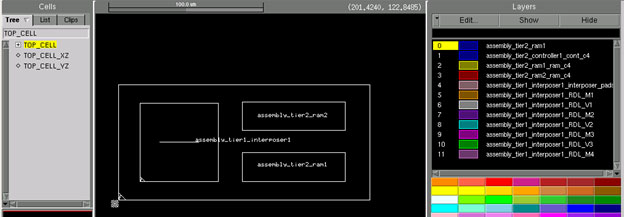

五、 示例:系统网表生成器流程

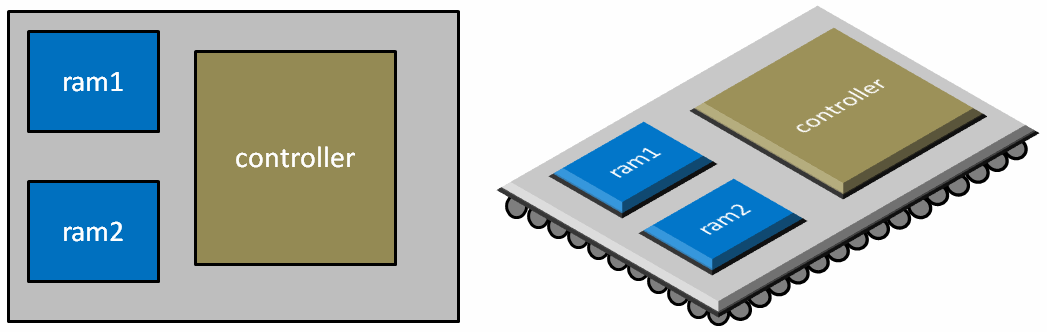

利用系统网表生成器(System Netlist Generator)图形用户界面(GUI),为中介层设计创建源网表。本示例包含相关设计数据。如图 A-5 所示,两个相同的 RAM 存储芯片和一个控制器芯片堆叠在一个中介层上。为简化说明,本示例省略了中介层网表。

图 A-5. 系统网表生成器中介层设计

存储器和控制器的 SPICE 网表定义于table A-3。芯片在中介层设计中的期望网连通性定义于图 A-

table A-3 本示例中的网表信息

| SPICE 文件名 | SPICE 网表内容 |

|---|---|

myram_netlist.spi |

.SUBCKT myram mode enable adr[0] adr[1] adr[2] w_data[0] w_data[1] w_data[2] w_data[3] w_data[4] w_data[5] w_data[6] w_data[7] r_data[0] r_data[1] r_data[2] r_data[3] r_data[4] r_data[5] r_data[6] r_data[7] .ENDS myram |

controller_netlist.spi |

.SUBCKT controller reset mode $--Chip enable bus-- ENABLE<0> ENABLE<1> $--Address bus-- ADDR<0> ADDR<1> ADDR<2> $--Port A+B-- GPIO_A<0> GPIO_A<1> GPIO_A<2> GPIO_A<3> GPIO_A<4> GPIO_A<5> GPIO_A<6> GPIO_A<7> GPIO_B<0> GPIO_B<1> GPIO_B<2> GPIO_B<3> GPIO_B<4> GPIO_B<5> GPIO_B<6> GPIO_B<7> $--Port C+D-- GPIO_C<0> GPIO_C<1> GPIO_C<2> GPIO_C<3> GPIO_C<4> GPIO_C<5> GPIO_C<6> GPIO_C<7> GPIO_D<0> GPIO_D<1> GPIO_D<2> GPIO_D<3> GPIO_D<4> GPIO_D<5> GPIO_D<6> GPIO_D<7> .ENDS controller |

5.1 创建新项目

启动系统网表生成器 GUI 并创建新项目。

table A-4. 中介层设计的网连通性

| 芯片布局实例 | 布局实例端口 | 网 |

|---|---|---|

| ram1 | mode | mode |

| enable | enable_1 | |

| adr(3 位) | address | |

| w_data(8 位) | write_data1 | |

| r_data(8 位) | read_data1 | |

| ram2 | mode | mode |

| enable | enable_2 | |

| adr(2 位) | address | |

| w_data(8 位) | write_data2 | |

| r_data(8 位) | read_data2 | |

| controller | reset | reset |

| mode | mode | |

| ENABLE<0> | enable_1 | |

| ENABLE<1> | enable_2 | |

| ADDR(2 位) | address | |

| GPIO_A(8 位) | write_data1 | |

| GPIO_B(8 位) | read_data1 | |

| GPIO_C(8 位) | write_data2 | |

| GPIO_D(8 位) | read_data2 |

5.2 将芯片导入数据库

前提条件

- 已具备必要许可证和软件。

操作步骤

-

在命令行中输入以下命令,调用系统网表生成器:

$CALIBRE_HOME/bin/sng -gui -

选择 File > New。此前禁用的菜单图标(\(\square\))现已启用,表明活动数据库已加载并可进行修改。

-

选择 File > Save ,并为项目输入新名称(例如

TOP_3D_sng)。主窗口底部的控制台可用于输入受支持的 Tcl 命令,以及《系统网表生成器图形用户界面》中列出的所有命令。同时,控制台还会报告工具生成的信息、警告和错误。

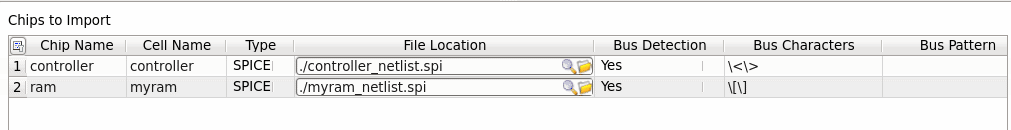

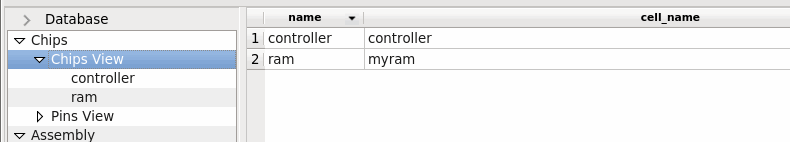

5.3 将芯片导入数据库

导入 SPICE 网表并为设计创建芯片。将芯片网表导入活动的系统网表生成器项目时,会为该芯片定义一个 SPICE 子电路。你可在 Chips 树中查看芯片的引脚和属性。

注意

若导入大型网表,需将环境变量 MGC_SNG_SPICE_IMPORT_TEMP_DIR 设置为临时目录的路径。

前提条件

- 有待导入的网表,或已将附录 A-3 中的

myram_netlist.spi和controller_netlist.spi网表保存至两个独立文件。

操作步骤

-

选择 File > Import Chips ,将 SPICE 网表加载到活动数据库中。Import Chips 窗格会在主窗口底部的控制台区域以标签页形式打开。

-

点击 Add Row 按钮。

-

按如下所示输入网表的芯片名称(Chip Name) 、单元名称(Cell Name) 、类型(Type) 、文件位置(File Location)和总线字符(Bus Characters) :注意,控制器和 RAM 芯片使用不同的字符表示总线。总线列的说明见第 259 页的

sng::import_chip。

-

点击 Import chips 按钮。源网表中的任何语法错误都会立即在控制台中报告。若操作失误并需要重新导入源文件,可选择 Edit > Remove Chips,并从项目中选择要删除的项。删除芯片后,可再次执行步骤 1 至 4。

-

操作完成后,保存数据库。

结果

导入的芯片现已显示在 Chips 树中,如下所示:

示例(Tcl 命令)

以下语句通过 Tcl 控制台提示符实现相同步骤:

tcl

sng::import_chip {sng::database} -chip_name {controller} \

-cell_name {controller} -type {SPICE} -path {./controller_netlist.spi} \

-bus_detection {Yes} -bus_chars {\<\>}

sng::import_chip {sng::database} -chip_name {ram} -cell_name {myram} \

-type {SPICE} -path {./myram_netlist.spi} -bus_detection {Yes} \

-bus_chars {\[\]}5.4 修改并添加芯片引脚

修改芯片定义中的引脚。

前提条件

- 已按《将芯片导入数据库》的说明,导入至少一个芯片定义。

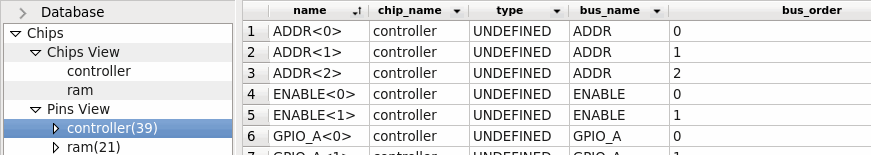

操作步骤

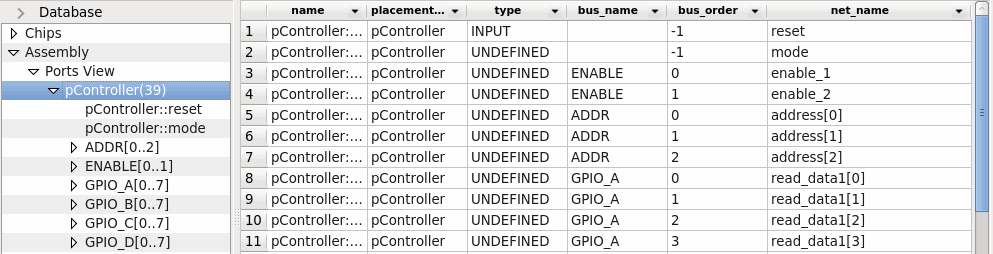

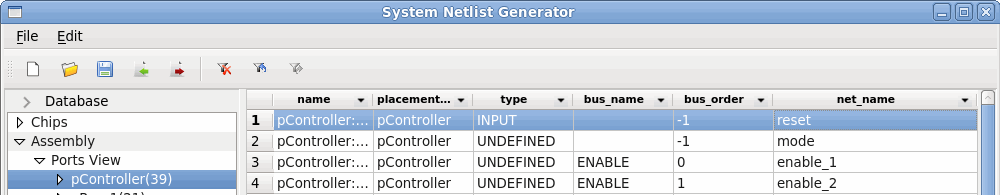

-

展开 Chips 树和 Pins View 树。

-

在 Pins View 下点击要修改的芯片。本示例中,点击

controller芯片。所有引脚的属性会列在 Chips 树右侧的表格中。你可直接编辑表格中的列,以修改引脚属性。

-

本示例中,将

reset引脚的类型修改为INPUT。 -

选择 Edit > Add Pins ,为芯片添加引脚。或者,在 Pins View 中右键点击,选择 Add Pins 。Add Pins 窗格会在主窗口底部以标签页形式打开。

-

点击 Add Row ,输入引脚名称和芯片名称,然后点击 Add Pins,在芯片上插入新引脚。

-

操作完成后,保存数据库。

结果

你已在芯片上添加或修改了引脚。这使你无需手动修改和重新导入 SPICE 网表,即可修改源芯片的网表。

示例(Tcl 命令)

列出芯片上所有引脚的控制台等效命令:

tcl

set my_db [sng::open_db -path ./TOP_3D_sng]

set controller_pins [sng::get_pins my_db -chip_name controller]

sng::get_property $controller_pins -property "pin_name"5.5 为芯片创建布局实例

在系统网表生成器项目中,为芯片创建布局实例(即实例化)。这与装配命令 place_chip 的网表等效操作。

前提条件

- 已按《将芯片导入数据库》的说明,导入至少一个芯片定义。

操作步骤

-

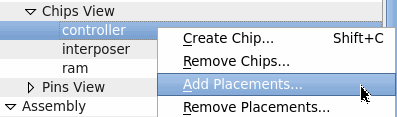

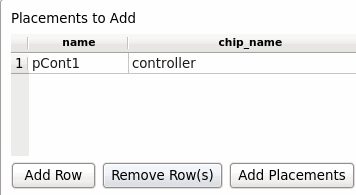

在 Chips 树中右键点击

controller,选择 Add Placement ,实例化控制器芯片。Add Placement 对话框会在主窗口底部以标签页形式打开。

-

点击 Add Row,开始创建新的布局实例。

-

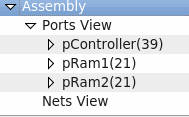

为控制器输入布局实例名称(每个实例必须具有唯一名称),然后点击 Add Placements 。布局实例

pController现已作为实例化芯片显示在 Assembly 树中。芯片上的引脚会转换为布局实例的端口。

-

使用相同方法,为两个存储芯片创建布局实例。

-

若出现错误,可选择 Edit > Remove Placements,删除不需要的布局实例。

-

保存数据库。

结果

项目中现已定义中介层上的三个布局实例。通过在 Assembly 树中选择布局实例,可查看其端口属性。

示例(Tcl 命令)

tcl

sng::create_placement my_db -placement_name {pController} -chip_name {controller}

sng::create_placement my_db -placement_name {pRam2} -chip_name {ram}

sng::create_placement my_db -placement_name {pRam1} -chip_name {ram}5.6 定义网连通性

通过在数据库中定义并分配网,将设计中的布局实例进行电气连接。

前提条件

-

已按《将芯片导入数据库》的说明,导入至少一个芯片定义。

-

已按《为芯片创建布局实例》的说明,在设计中创建至少一个布局实例。

操作步骤

-

选择 Edit > Add Nets。

-

点击 Add Row。

-

在

net_name字段中输入reset,在ports_list字段中输入pController::reset。 -

点击 Add Nets。

-

选择

pController布局实例,注意属性表格中的端口现已在net_name列中连接到reset网。对于引脚数量较多的布局实例,建议使用 Tcl 控制台界面定义连通性。

-

保存数据库并退出工具。

-

在 shell 脚本中输入以下 Tcl 命令,将控制器的四个 8 位通用数据端口和地址端口,连接到两个 RAM 布局实例的 8 位读、写和地址端口:

tcl

#set db_instance to current project set my_db [sng::open_db -path ./TOP_3D_sng] #Connect read data from controller to pRam1 sng::connect my_db -net_name read_data1 \ -buses {pController::GPIO_A pRam1::r_data} #Connect write data from controller to pRam1 sng::connect my_db -net_name write_data1 \ -buses {pController::GPIO_B pRam1::w_data} #Connect read data from controller to pRam2 sng::connect my_db -net_name read_data2 \ -buses {pController::GPIO_C pRam2::r_data} #Connect write data from controller to pRam1 sng::connect my_db -net_name write_data2 \ -buses {pController::GPIO_D pRam2::w_data} #Connect address bus to all three chips sng::connect my_db -net_name address \ -buses {pController::ADDR pRam1::adr pRam2::adr} sng::save_db my_db -path ./TOP_3D_sng -

将脚本保存为

connect.tcl并关闭。 -

使用以下命令执行 Tcl 脚本:

sng -batch -script connect.tcl -

调用系统网表生成器并加载

TOP_3D_sng数据库。Assembly 树现在会显示三个芯片上所有新的已连接网和总线。 -

手动完成剩余连接。

-

保存数据库。

结果

Assembly 树和布局实例中已填充所有总线网连接。mode 和 enable 连接尚未建立,可通过 GUI 或批处理脚本进行连接。

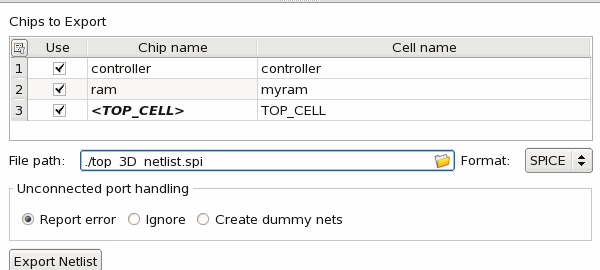

5.7 导出完整设计

从系统网表生成器中导出已完成的源网表。

前提条件

- 已完成的系统网表生成器数据库,该数据库定义了 3D-IC 的所有芯片、布局实例和网连通性。

操作步骤

-

保存当前数据库或打开现有数据库。

-

选择 File > Export Netlist ,或点击主窗口顶部的(\(\square\))图标。Export Netlist 对话框会在主窗口底部打开。

-

启用所有要导出的芯片,并指定 SPICE 文件的路径。

-

点击 Export Netlist。

结果

已利用系统网表生成器,为附录 A-5 所示的 3D-IC 创建了源网表。你可通过 source_netlist 命令,在 Calibre 3DSTACK 运行中使用此 3D-IC 的理想电气表示,从而验证提取的布局是否符合设计意图。

示例(批处理命令)

本操作的批处理命令等效形式如下:

tcl

sng::export_netlist my_db --chip_name_list "myram1 controller" \

-path ./top_3d_netlist.spi示例(生成的 SPICE 网表)

以下是本设计的完整装配网表:

spice

.SUBCKT controller reset mode ENABLE<0> ENABLE<1> ADDR<0> ADDR<1> ADDR<2>

+ GPIO_A<0> GPIO_A<1> GPIO_A<2> GPIO_A<3> GPIO_A<4> GPIO_A<5> GPIO_A<6>

+ GPIO_A<7> GPIO_B<0> GPIO_B<1> GPIO_B<2> GPIO_B<3> GPIO_B<4> GPIO_B<5>

+ GPIO_B<6> GPIO_B<7> GPIO_C<0> GPIO_C<1> GPIO_C<2> GPIO_C<3> GPIO_C<4>

+ GPIO_C<5> GPIO_C<6> GPIO_C<7> GPIO_D<0> GPIO_D<1> GPIO_D<2> GPIO_D<3>

+ GPIO_D<4> GPIO_D<5> GPIO_D<6> GPIO_D<7>

.ENDS controller

.SUBCKT myram mode enable adr[0] adr[1] adr[2] w_data[0] w_data[1] w_data[2]

+ w_data[3] w_data[4] w_data[5] w_data[6] w_data[7] r_data[0] r_data[1]

+ r_data[2] r_data[3] r_data[4] r_data[5] r_data[6] r_data[7]

.ENDS myram

.SUBCKT TOP_CELL

XpController reset mode enable_1 enable_2 address[0] address[1] address[2]

+ read_data1[0] read_data1[1] read_data1[2] read_data1[3] read_data1[4]

+ read_data1[5] read_data1[6] read_data1[7] write_data1[0] write_data1[1]

+ write_data1[2] write_data1[3] write_data1[4] write_data1[5] write_data1[6]

+ write_data1[7] read_data2[0] read_data2[1] read_data2[2] read_data2[3]

+ read_data2[4] read_data2[5] read_data2[6] read_data2[7] write_data2[0]

+ write_data2[1] write_data2[2] write_data2[3] write_data2[4] write_data2[5]

+ write_data2[6] write_data2[7] controller

XpRam1 mode enable_1 address[0] address[1] address[2] write_data1[0]

+ write_data1[1] write_data1[2] write_data1[3] write_data1[4] write_data1[5]

+ write_data1[6] write_data1[7] read_data1[0] read_data1[1] read_data1[2]

+ read_data1[3] read_data1[4] read_data1[5] read_data1[6] read_data1[7] myram

XpRam2 mode enable_2 address[0] address[1] address[2] write_data2[0]

+ write_data2[1] write_data2[2] write_data2[3] write_data2[4] write_data2[5]

+ write_data2[6] write_data2[7] read_data2[0] read_data2[1] read_data2[2]

+ read_data2[3] read_data2[4] read_data2[5] read_data2[6] read_data2[7] myram

.ENDS TOP_CELL六、示例:规则文件

6.1 Calibre 3DSTACK+ 扩展语法示例

扩展语法规则文件比传统 Calibre 3DSTACK 规则文件更灵活,因为装配操作可与规则分离。以下示例创建一个简单的 2.5D IC,包含一个控制器芯片和两个存储芯片,堆叠在一个无源中介层上。

6.2 开头语句

扩展语法规则必须以以下行开头:

#!3dstack+下一条语句必须是 set_version 命令,用于设置规则文件的语法版本。唯一受支持的版本为 1.0。

#!3dstack+

######################################################################

#

# 用于 2.5D 中介层的 CALIBRE 3DSTACK+ 规则文件

#

######################################################################

set_version -version 1.06.3 Calibre 3DSTACK 设置

应用配置命令,设置布局、连通性和输出选项。本示例中,规则文件为生成的堆叠装配体提供名称,为完整装配体指定源网表(强烈建议),指定输出详细报告,并将生成的装配网表导出为 Verilog 文件。

###########################

# 配置运行参数

###########################

config \

-layout_primary TOP_CELL \

-netlist {-file ./design/top_cell.spi -format SPICE -case YES }\

-report {-file output/3dstack.report} \

-export_connectivity {-file output/3dstack.v -format verilog }6.4 芯片和层定义

下一部分定义堆叠中使用的每个芯片。芯片定义必须包含布局文件的路径,以及堆叠中用于连通性的所有层。第一个芯片定义是中介层,包含多个用于连接芯片的金属层。为使 Calibre 3DSTACK 理解这些层的交互方式,必须通过 die -wb_connect 参数定义层间交互。这被称为白盒连通性 ,因为你定义的是芯片内部的层连通性,而非仅定义外部接口。要指示某一层是芯片外部连通性堆叠的一部分(用于芯片间的连通性追踪),需应用 -layer_info ... -ext_connect 选项。注意,本节仅定义堆叠中使用的芯片。这些芯片在装配体中的物理布局方式,通过 stack 命令实现。

###########################

# 定义堆叠中的芯片

###########################

die -die_name interposer \

-layout { \

-path ./design/interposer.gds \

-type gdsii \

-primary interposer \

-depth all \

} \

-layer_info { \

-type pad \

-name interposer_pads \

-ext_connect \

-layer { \

255 \

-depth all \

} \

-text { 255 } \

-bottom \

} \

-layer_info { \

-type RDL_M1 \

-name RDL_M1 \

-ext_connect \

-layer { \

11 \

-depth all \

} \

-bottom \

} \

-layer_info { \

-type RDL_V1 \

-name RDL_V1 \

-layer { \

12 \

-depth all \

} \

-bottom \

} \

-layer_info { \

-type RDL_M2 \

-name RDL_M2 \

-layer { \

13 \

-depth all \

} \

-bottom \

} \

-layer_info { \

-type RDL_V2 \

-name RDL_V2 \

-layer { \

14 \

-depth all \

} \

-bottom \

} \

-layer_info { \

-type RDL_M3 \

-name RDL_M3 \

-layer { \

15 \

-depth all \

} \

-bottom \

} \

-layer_info { \

-type RDL_V3 \

-name RDL_V3 \

-layer { \

16 \

-depth all \

} \

-bottom \

} \

-layer_info { \

-type RDL_M4 \

-name RDL_M4 \

-layer { \

17 \

-depth all \

} \

-bottom \

} \

-interposer \

-wb_connect RDL_M1 RDL_M2 BY RDL_V1 \

-wb_connect RDL_M2 RDL_M3 BY RDL_V2 \

-wb_connect RDL_M3 RDL_M4 BY RDL_V3 \

-wb_connect interposer_pads RDL_M1

die -die_name controller \

-layout { \

-path ./design/controller.gds \

-type gdsii \

-primary controller \

-depth top-only \

} \

-layer_info { \

-type bump \

-name cont_c4 \

-ext_connect \

-layer { \

255 \

-depth top-only \

} \

-text { 255 } \

-bottom \

}

die -die_name ram \

-layout { \

-path ./design/ram.gds \

-type gdsii \

-primary ram \

-depth top-only \

} \

-layer_info { \

-type bump \

-name ram_c4 \

-ext_connect \

-layer { \

255 \

-depth top-only \

} \

-text { 255 } \

-bottom \

}6.5 装配操作

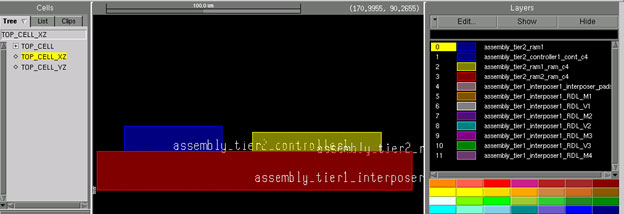

到目前为止,规则文件中已定义所有芯片和层。下一步是通过 stack 命令,定义这些芯片的布局方式(装配)。本示例中,首先通过 -die 参数布局底层芯片。-placement 参数确定中介层的水平 x 和 y 布局位置。控制器和两个 RAM 芯片位于同一垂直平面(其初始 z 坐标相同),这被称为一个层(tier) 。该层堆叠在中介层顶部,其初始 z 坐标由中介层的厚度和指定的 -z_origin 隐式确定。图 A-6 和图 A-7 显示了本示例中语句生成的装配体。

Figure A-6. Overhead View of the Example Assembly

Figure A-7. Side View of the Example Assembly

###############################

# 在 3DSTACK 中排列芯片

###############################

stack -stack_name assembly \

-die { \

-name interposer \

-source pInterp \

-placement 0 0 \

-invert \

} \

-z_origin 0 \

-tier { \

-die {-name controller -placement 14 12 -source pCont}\

-die {-name ram -placement 80 12 -source pRam1}\

-die {-name ram -placement 80 45 -source pRam2}\

}6.6 验证规则

3DSTACK+ 扩展语法中的验证规则基于层,而非特定于某个设计。这使你能够编写可用于任何装配体的规则。本节示例仅展示了部分可用的验证检查。

###############################

# LVS 检查

###############################

connected -check_name CONNECT_IO \

-layer_type1 pad \

-layer_type2 bump \

-detailed -black_box \

-comment "CONNECT::Controller to Interposer check"

###############################

# DRC 检查

###############################

external -check_name PAD_SPACE -layer_type1 pad \

-constraint "< 65 REGION" -comment "ERR:Placement within 65um!"

external -check_name RDL_M1.1 -layer_type1 RDL_M1 \

-constraint "< 1 REGION" -comment "ERR: Spacing < 0.1um on RDL_M1!"

external -check_name RDL_M2.1 -layer_type RDL_M2 \

-constraint "< 0.07 REGION" -comment "ERR: Spacing < 0.5um on RDL_M2!"

overlap -check_name "OVERLAP_PAD_BUMP" \

-layer_type1 pad \

-layer_type2 bump \

-constraint " < 99" -intersection \

-comment "Pad overlap must be greater than 90%!"

select_checks -check_names {OVERLAP_PAD_BUMP PAD_SPACE CONNECT_IO}6.7 标准(传统)语法示例 1

使用传统 Calibre 3DSTACK 规则文件语法的典型示例。

# This file includes a 3D-IC Description Language ("3DIC_DL")

# used within/by Mentor Graphics' products supporting 2.5D/3D-IC IC

# applications. You shall not use this 3DIC_DL # unless you are a Mentor

# Graphics customer. The exact terms of your obligations and rights are

# governed by your respective license.

# You shall not use this 3DIC_DL except:

# (a) for your internal business purposes and

# (b) for use with Mentor Graphics' Calibre(r) tools.

# The 3DIC_DL may constitute or contain trade secrets and confidential

# information of Mentor Graphics or its licensors. You shall not make the

# 3DIC_DL available in any form to any person other than your employees

# and on-site contractors, excluding Mentor Graphics competitors, whose

# job performance requires access and who are under obligations of

# confidentiality.

set_version -version 1.0

# Ensure layouts are LVS/DRC clean by running Calibre

# declare layouts

layout -chip_name c1 -primary TOPCELL -path ./chip1.gds -system GDS \

-original_extent

layout -chip_name c2 -primary TOPCELL -path ./chip2.gds -system GDS \

-original_extent

layout -chip_name ip -primary TOPCELL -path ./interposer.gds -system GDS

# declare layers

layer -layer m11 -chip c1 -layer_number 0

layer -layer m21 -chip c1 -layer_number 1

layer -layer m12 -chip c2 -layer_number 0

layer -layer m22 -chip c2 -layer_number 1

layer -layer m13 -chip ip -layer_number 0

layer -layer m23 -chip ip -layer_number 1

# declare additional layers

# Note that TVF code inside the tvf_block check is stand-alone and is

# outside the scope of the chip stack rule file.

tvf_block additional_layers {

tvf::SETLAYER m11_m21 = c1p_m11 AND c1p_m21;

tvf::SETLAYER m12_m22 = c2p_m12 AND c2p_m22;

} -export_layers [list m11_m21 m12_m22]

# export connectivity

export_connectivity -file spice_output.spi -format SPICE

# import connectivity

source_netlist -file spice_input.spi -format SPICE

# place chip2 and the interposer

place_chip -placement c2p -chip c2 -x_origin 1.85 -y_origin 0

place_chip -placement ipp -chip ip -x_origin 0 -y_origin 0

# create a 2x3 array of chip1 placements

for { set x 1 } { $x < 3 } { incr x } {

for { set y 1 } { $y < 4 } { incr y } {

place_chip -placement c1p_$x\_$y -chip c1 -x_origin [expr $x+1] \

-y_origin [expr $y+1] -flip y

}

}

# dimensional checks

#results highlighted in Calibre RVE only show layers used in checks:

set_auto_rve_show_layers YES

enclosure -check_name enc_check -placement1 ipp_m13 \

-placement2 c2p_m12 -constraint "<= 0.03 REGION" \

-comment "enclosure check" -set_rve_highlight_color blue

external -check_name ext_check -placement1 ipp_m13 \

-constraint "<= 0.05 REGION" \

-comment "external check" -set_rve_highlight_color yellow

internal -check_name int_check -placement1 ipp_m13 \

-constraint "<= 0.17 REGION" \

-comment "internal check"

# connectivity check

attach_text -placement c2p_m12 -text_placement c2p_m12

attach_text -placement ipp_m13 -text_placement ipp_m13

connected -check_name con_check -placement1 c2p_m12 \

-placement2 ipp_m13 -comment "connectivity check" \

-set_rve_priority 1

# output report

report -file report.txt6.8 标准(传统)语法示例 2

使用传统 Calibre 3DSTACK 规则文件语法,创建规则装配体和连通性检查的简化方法。

# This file includes a 3D-IC Description Language ("3DIC_DL")

# used within/by Mentor Graphics' products supporting 2.5D/3D-IC IC

# applications. You shall not use this 3DIC_DL # unless you are a Mentor

# Graphics customer. The exact terms of your obligations and rights are

# governed by your respective license.

# You shall not use this 3DIC_DL except:

# (a) for your internal business purposes and

# (b) for use with Mentor Graphics' Calibre(r) tools.

# The 3DIC_DL may constitute or contain trade secrets and confidential

# information of Mentor Graphics or its licensors. You shall not make the

# 3DIC_DL available in any form to any person other than your employees

# and on-site contractors, excluding Mentor Graphics competitors, whose

# job performance requires access and who are under obligations of

# confidentiality.

set_version -version 1.0

layout_primary TOPCELL_3DIC

# stack three chips together (chip1.gds through chip3.gds)

for { set i 1 } { $i <= 3 } { incr i } {

layout -chip_name c$i -primary TOPCELL -path ./chip$i\.gds \

-system GDS

layer -layer m$i -chip c$i -layer_number 0

place_chip -placement c$i\p -chip c$i -x_origin [expr $i-1] \

-y_origin 0

attach_text -placement c$i\p_m$i -text_placement c$i\p_m$i

}

# perform verification checks

for { set i 1 } { $i <= 2 } { incr i } {

connect c$i\p_m$i c[expr $i+1]p_m[expr $i+1]

connected -check_name con_check$i -placement1 c$i\p_m$i \

-placement2 c[expr $i+1]p_m[expr $i+1]

internal -check_name int_check$i -placement1 c$i\p_m$i \

-placement2 c[expr $i+1]p_m[expr $i+1] -constraint "<= 0.5" \

-comment "internal check$i\, c$i\p_m$i to c[expr $i+1]p_m[expr $i+1]"\

-set_rve_show_layers AUTO

}

# output report

report -file report.txt七、报告文件格式

Calibre 3DSTACK 报告文件通过 report 命令生成。报告的各部分按生成顺序排列。

7.1 报告头

报告开头包含输入、输出、用户和设计信息的摘要。

##################################################

## C A L I B R E S Y S T E M ##

## 3 D S T A C K R E P O R T ##

##################################################

## # # ~ ~ ##

## # # x x ##

## # @ ##

## # # ___ ##

## # # / \ ##

##################################################

REPORT FILE NAME: /home/userDir/3dstack_report.rpt

MAXIMUM RESULTS: 50

LAYOUT CHIP NAME: controller - ./designs/controller.gds ('controller')

LAYOUT CHIP NAME: myram - ./designs/fullchip_clean_myram.gds ('myram')

LAYOUT CHIP NAME: interposer - ./designs/interposer.gds ('interposer')

SOURCE NETLIST: /home/userDir/designs/system_netlist.spi ('TOP_3D')

3DSTACK ASSEMBLY: /home/userDir/3dstack_assembly.gds.gz ('TOP_3D')

RULE FILE: /home/userDir/3dstack.rules

CREATION TIME: 07/17/13 16:28:59

CURRENT DIRECTORY: /home/userDir

USERNAME: user

CALIBRE VERSION: Calibre v2013.3_x.xxxx Tue Jul 16 13:25:32 PDT 2013

RENAMING: NO7.2 绘制层、布局实例和文本层摘要

报告总结了规则文件中指定的层、布局实例和文本。

1. 重命名规则

RENAMING RULES:2. 层

LAYERS:

Layer Name: INTERP_FRONT_if

Chip: interposer

Layer Number: 100

Layer Name: bmet1

Chip: interposer

Layer Number: 51

Layer Name: bmet2

Chip: interposer

Layer Number: 53

Layer Name: tsv

Chip: interposer

Layer Number: 50

Layer Name: INTERP_BACK_if

Chip: interposer

Layer Number: 200

Layer Name: CONTROLLER_if

Chip: controller

Layer Number: 100

Layer Name: via_rdl1

Chip: interposer

Layer Number: 20

Layer Name: bvia1

Chip: interposer

Layer Number: 52

Layer Name: metal_rdl1

Chip: interposer

Layer Number: 19

Layer Name: RAM_if

Chip: myram

Layer Number: 100

Layer Name: metal_rdl2

Chip: interposer

Layer Number: 213. 堆叠中芯片和层布局实例的报告

所有层和布局实例都会写入报告,这对验证装配体非常有用。

ANCHOR PLACEMENT(S):

PLACEMENT(S):

Chip Placement: pCont

Layout: controller

x-origin: 0.000

y-origin: 0.000

Magnification: 1.0

Rotation: 0

Flip Axis: y

Chip Placement: pRAM_stack3

Layout: myram

x-origin: -780.000

y-origin: 520.000

Magnification: 1.0

Rotation: 180

Flip Axis: y

Chip Placement: pRAM_stack4

Layout: myram

x-origin: -740.000

y-origin: 80.000

Magnification: 1.0

Rotation: 270

Flip Axis: y

Chip Placement: pRAM_stack5

Layout: myram

x-origin: -740.000

y-origin: 80.000

Magnification: 1.0

Rotation: 270

Flip Axis: y

Chip Placement: pRAM_stack1

Layout: myram

x-origin: 280.000

y-origin: 65.000

Magnification: 1.0

Rotation: 0

Flip Axis: y

Chip Placement: pInterp

Layout: interposer

x-origin: 0.000

y-origin: 0.000

Magnification: 1.0

Rotation: 0.0

Flip Axis: NONE

Chip Placement: pRAM_stack2

Layout: myram

x-origin: 230.000

y-origin: 505.000

Magnification: 1.0

Rotation: 90

Flip Axis: y4. 堆叠中定义的文本层的详细信息

每个定义的层都会单独列出。

TEXT LAYER(S):

Layer: pRAM_stack2_RAM_if (pRAM_stack2_RAM_if)

Layer: pCont_CONTROLLER_if (pCont_CONTROLLER_if)

Layer: pRAM_stack3_RAM_if (pRAM_stack3_RAM_if)

Layer: pRAM_stack4_RAM_if (pRAM_stack4_RAM_if)

Layer: pRAM_stack1_RAM_if (pRAM_stack1_RAM_if)5. net映射

本节总结了 net_map 或 config -net_map 命令的net映射操作:

NET MAPPING:

FROM: TO:

---------------------------------------

PWR VDD7.3 验证结果

验证检查结果在 RULECHECK SUMMARY 部分报告。

总体验证结果

*************************************************************************

RULECHECK SUMMARY

*************************************************************************

Status Result Count Rule

-------------------------------------------------------------------------

COMPLETED 0 Floating_Text ( Selecting text labels from

pCont_CONTROLLER_if not having overlap with any of the pads. Selecting

text labels from pRAM_stack1_RAM_if not having overlap with any of the

pads (the same as for pRAM_stack2_RAM_if, pRAM_stack3_RAM_if,

pRAM_stack4_RAM_if). )

COMPLETED 5 No_Text ( Selecting pads from pCont_CONTROLLER_if

not having text-labels attached. Selecting pads from pRAM_stack1_RAM_if

not having text-labels attached (the same as for pRAM_stack2_RAM_if,

pRAM_stack3_RAM_if, pRAM_stack4_RAM_if). )

COMPLETED 0 Multi_Text ( Shapes from placement

pCont_CONTROLLER_if overlap multiple text labels from text placement

pCont_CONTROLLER_if. Shapes from placement pRAM_stack1_RAM_if overlap

multiple text labels from text placement pRAM_stack1_RAM_if (the same as

for pRAM_stack2_RAM_if, pRAM_stack3_RAM_if, pRAM_stack4_RAM_if). )

COMPLETED 0 ExtraPorts

Physical Verification Results

COMPLETED 1 PLACEMENT_check

( RAM should be more than 70 um from controller. )

COMPLETED 50 (of 56) offgrid1

COMPLETED 1 centers_interposer

( Pad centers must be within exactly 80 um )

Connected Check Verification Results

COMPLETED 2 CONNECT_RAM2_to_CONTROLLER

( CONNECTION CHECK between LAYER:pRAM_stack2_RAM_if and

LAYER:pCont_CONTROLLER_if )

COMPLETED 0 CONNECT_RAM3_to_CONTROLLER

( CONNECTION CHECK between LAYER:pRAM_stack3_RAM_if and

LAYER:pCont_CONTROLLER_if )

COMPLETED 0 CONNECT_RAM4_to_CONTROLLER

( CONNECTION CHECK between LAYER:pRAM_stack4_RAM_if and

LAYER:pCont_CONTROLLER_if )

COMPLETED 0 CONNECT_RAM1_to_CONTROLLER

( CONNECTION CHECK between LAYER:pRAM_stack1_RAM_if and

LAYER:pCont_CONTROLLER_if )源和布局中缺失的布局实例

*************************************************************************

MISSING PLACEMENTS

*************************************************************************

LAYOUT NAME SOURCE NAME

NONE布局中缺失的端口

*************************************************************************

SOURCE PORTS MISSING LAYOUT PORTS

*************************************************************************

RuleCheck: CONNECT_RAM1_to_CONTROLLER ( CONNECTION CHECK between

LAYER:pRAM_stack1_RAM_if and LAYER:pCont_CONTROLLER_if )

-------------------------------------------------------------------------

NONE

RuleCheck: CONNECT_RAM2_to_CONTROLLER ( CONNECTION CHECK between

LAYER:pRAM_stack2_RAM_if and LAYER:pCont_CONTROLLER_if )

-------------------------------------------------------------------------

NONE

RuleCheck: CONNECT_RAM3_to_CONTROLLER ( CONNECTION CHECK between

LAYER:pRAM_stack3_RAM_if and LAYER:pCont_CONTROLLER_if )

-------------------------------------------------------------------------

NONE

RuleCheck: CONNECT_RAM4_to_CONTROLLER ( CONNECTION CHECK between

LAYER:pRAM_stack4_RAM_if and LAYER:pCont_CONTROLLER_if )

-------------------------------------------------------------------------

NONE源中缺失的端口

*************************************************************************

LAYOUT PADS MISSING SOURCE PORTS

*************************************************************************

RuleCheck: CONNECT_RAM1_to_CONTROLLER ( CONNECTION CHECK between

LAYER:pRAM_stack1_RAM_if and LAYER:pCont_CONTROLLER_if )

-------------------------------------------------------------------------

NONE

RuleCheck: CONNECT_RAM2_to_CONTROLLER ( CONNECTION CHECK between

LAYER:pRAM_stack2_RAM_if and LAYER:pCont_CONTROLLER_if )

-------------------------------------------------------------------------

NONE

RuleCheck: CONNECT_RAM3_to_CONTROLLER ( CONNECTION CHECK between

LAYER:pRAM_stack3_RAM_if and LAYER:pCont_CONTROLLER_if )

-------------------------------------------------------------------------

NONE

RuleCheck: CONNECT_RAM4_to_CONTROLLER ( CONNECTION CHECK between

LAYER:pRAM_stack4_RAM_if and LAYER:pCont_CONTROLLER_if )

-------------------------------------------------------------------------

NONE源和布局之间的网差异

*************************************************************************

INCORRECT NETS

*************************************************************************

LAYOUT NAME SOURCE NAME

RuleCheck: CONNECT_RAM1_to_CONTROLLER ( CONNECTION CHECK between

LAYER:pRAM_stack1_RAM_if and LAYER:pCont_CONTROLLER_if )

-------------------------------------------------------------------------

NONE

RuleCheck: CONNECT_RAM2_to_CONTROLLER ( CONNECTION CHECK between

LAYER:pRAM_stack2_RAM_if and LAYER:pCont_CONTROLLER_if )

-------------------------------------------------------------------------

Net 105 ADR<0>

** missing connection ** pCont:ADR<0>

Net 61 ADR<0>

** missing connection ** pRAM_stack2:ADR<0>

RuleCheck: CONNECT_RAM3_to_CONTROLLER ( CONNECTION CHECK between

LAYER:pRAM_stack3_RAM_if and LAYER:pCont_CONTROLLER_if )

-------------------------------------------------------------------------

NONE

RuleCheck: CONNECT_RAM4_to_CONTROLLER ( CONNECTION CHECK between

LAYER:pRAM_stack4_RAM_if and LAYER:pCont_CONTROLLER_if )

-------------------------------------------------------------------------

NONE