在复杂的SoC设计中,如何实现高效、低侵入性的调试和性能分析一直是个挑战。ARM CoreSight架构应运而生,为芯片设计者提供了一套完整的调试和追踪解决方案。本文将深入解析CoreSight IP的架构组成、功能特点及其在实际芯片设计中的应用。

一、CoreSight架构概述

ARM CoreSight是ARM公司于2004年推出的调试体系结构,旨在对复杂SoC实现全面的debug和trace功能。该架构包含众多组件,共同构成了一个完整的调试系统。

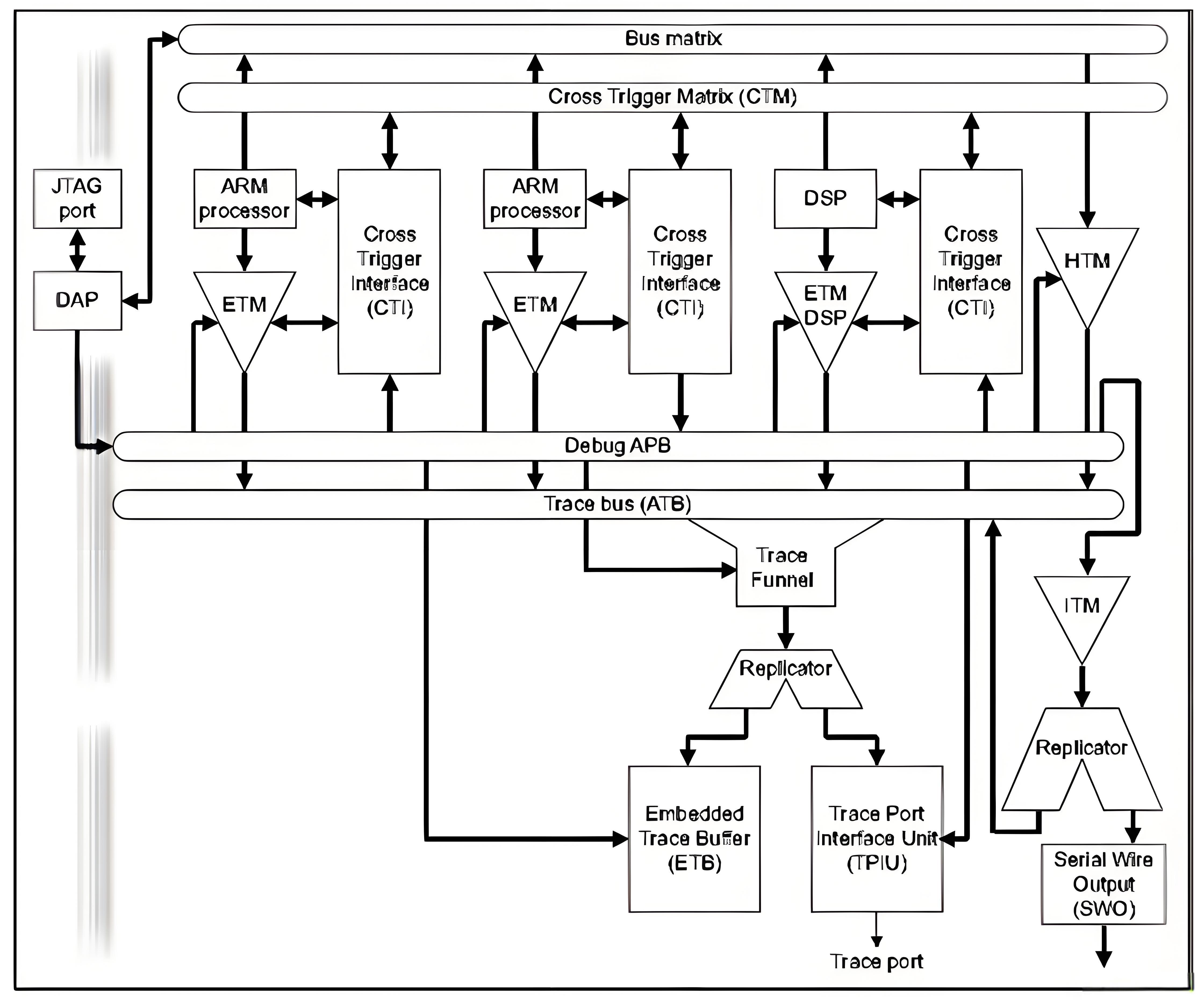

在一个典型的CoreSight环境中,包含三个核心通路:

Trace通路:负责将处理器和DSP的内部信息实时输出到外部

Debug通路:实现外部调试器对处理器的在线调试功能

Trigger通路:实现不同处理器之间的调试事件传递

二、CoreSight组件详解

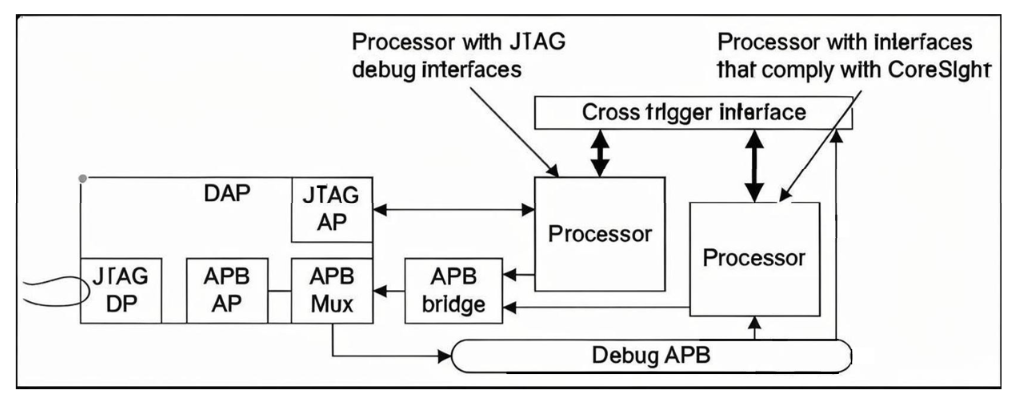

2.1 调试访问端口(DAP)

DAP是连接外部调试工具与芯片内部资源的桥梁,虽然不属于CoreSight组件,但却是访问CoreSight组件的重要入口。DAP由DP(Debug Port)和AP(Access Port)组成。

DP负责接收外部的JTAG或SW数据,转化为对内部AP的访问。AP再将访问转化为memory-mapped总线访问,实现对内部资源的操作。一个DAP可以包含1-256个AP,支持多种总线协议:

APB access port(APB-AP)

AHB access port(AHB-AP)

AXI access port(AXI-AP)

JTAG access port(JTAG-AP)

2.2 追踪源组件

追踪源是产生跟踪信息的核心组件,主要包括:

ETM(嵌入式追踪宏单元):连接到处理器,支持指令追踪和数据追踪

PTM(程序流追踪宏单元):监控处理器运行状况,压缩传输指令执行信息

STM(系统追踪宏单元):追踪总线互联上的trace信息

HTM(AMBA AHB追踪宏单元):专用于AMBA总线追踪

2.3 追踪链路与汇聚组件

在trace信息传递过程中,需要中间组件进行数据处理:

Trace Funnel:将多个ATB总线数据合并成单一数据流

Replicator:将单个ATB数据分发到多个输出

ATB Bridge:在不同ATB域之间传输数据

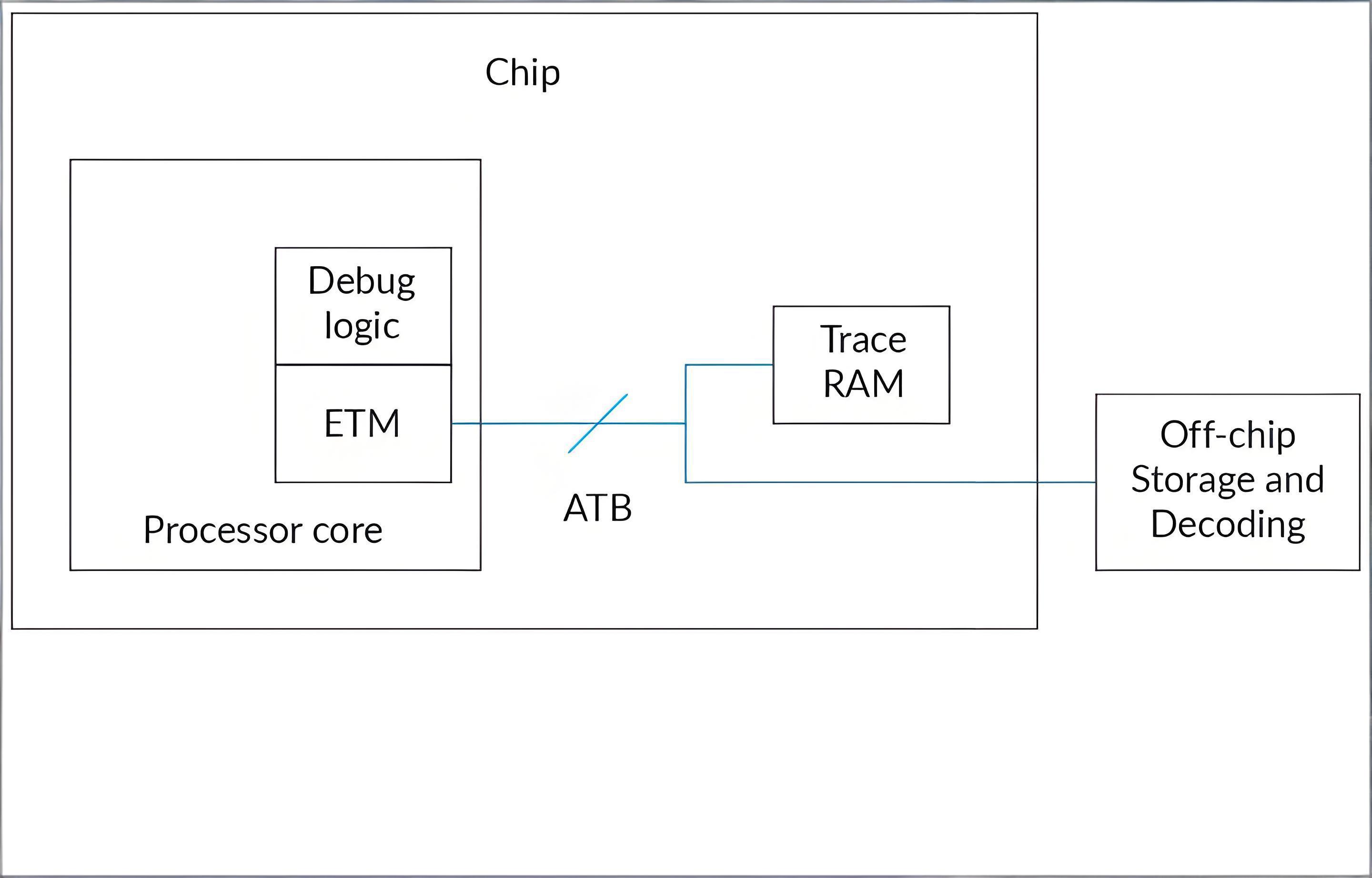

2.4 追踪接收组件

最终接收trace信息的组件包括:

TPIU(Trace Port接口单元):将ATB数据通过trace port发送到外部

ETB(嵌入式追踪缓冲区):芯片内RAM,存储捕捉到的跟踪信息

TMC(追踪内存控制器):可配置为ETB、ETR或ETF模式

ETR(嵌入式追踪路由器):将trace数据通过AXI接口传输到系统内存

三、CoreSight在实际应用中的优势

3.1 低侵入性调试

与传统JTAG调试相比,CoreSight通过总线控制传输数据,不影响CPU正常运行。这种非侵入式调试对系统性能影响极小,特别适合实时性要求高的应用场景。

3.2 高性能追踪能力

CoreSight支持高速追踪,SWO接口速度可达100M以上,远高于传统UART接口。以Cortex-M系列为例,ITM模块可以实现:

字符串调试消息输出

中断进入/退出监控

函数调用跟踪

程序计数器周期性采样

数据观察点功能

3.3 电源管理支持

CoreSight支持debug over powerdown功能,通过独立的debug电源域,在处理器下电时仍能保持调试连接。这种机制确保了调试过程的连续性,极大方便了低功耗场景下的调试工作。

四、CoreSight产品系列演进

ARM提供了两个主要版本的CoreSight SoC IP:

SoC-400系列:实现CoreSight v2和ADI v5.2架构

SoC-600系列:实现CoreSight v3和ADI v6.0架构,支持更先进的拓扑结构

SoC-600系列引入了革命性的改进,支持不依赖传统JTAG/SWD接口的调试方式,可以通过PCIe、USB等功能端口进行调试,大大提高了调试的灵活性。

五、安全调试机制

在现代芯片设计中,调试功能的安全性至关重要。CoreSight提供了完整的authentication机制:

DBGEN:侵入式调试使能

SPIDEN:安全侵入式调试使能

NIDEN:非侵入式调试使能

SPNIDEN:安全非侵入式调试使能

通过secure enclave和challenge-response机制,确保只有授权用户才能访问调试功能,有效防止恶意调试行为。

六、实际应用案例

6.1 SWO离线输出实现

在Cortex-M芯片上,可以通过配置ITM和TPIU寄存器实现SWO离线输出:

void SWO_Init(uint32_t cpuCoreFreqHz, uint32_t SWOSpeed)

{

volatile uint32_t SWOPrescaler = (cpuCoreFreqHz / SWOSpeed) - 1;

// 启用trace和debug模块

(*(volatile unsigned int*)0xE000EDFC) |= (1 << 24);

// 配置TPIU

(*(volatile unsigned int*)0xE00400F0) = 0x00000004; // 选择NRZ模式

(*(volatile unsigned int*)0xE0040010) = SWOPrescaler; // 设置预分频器

// 配置ITM

(*(volatile unsigned int*)0xE0000E80) = 0x0001040B; // 启用ITM模块

(*(volatile unsigned int*)0xE0000E00) = 0x00000001; // 启用stimulus端口

}这种实现方式支持非debug模式下的高速printf功能,速度可达24M以上,远超过传统串口输出。

6.2 多核调试支持

对于异构多核系统(如ARM big.LITTLE架构),CoreSight通过CTI(交叉触发接口)和CTM(交叉触发矩阵)实现核间调试事件传递,大大简化了复杂系统的调试难度。

七、总结

ARM CoreSight IP为现代SoC设计提供了一套完整、高效的调试解决方案。其模块化架构允许芯片设计者根据具体需求灵活配置调试功能,从简单的单核调试到复杂的多核异构系统调试,CoreSight都能提供良好的支持。

随着芯片复杂度不断提升,调试和性能分析的重要性日益凸显。CoreSight架构不仅提供了强大的调试能力,还通过标准化接口降低了工具链开发难度,使得芯片设计者能够更专注于功能开发而非调试基础设施的构建。

对于追求高性能、低功耗的现代芯片设计而言,合理利用CoreSight IP的各项功能,将显著提升开发效率和最终产品的质量。