目录

1.前言

本课题为之前博客中写的文章的硬件调试:

基于FPGA的图像形态学腐蚀算法实现,包括tb测试文件和MATLAB辅助验证

在仿真版本的基础上,我们增加了图像存储模块,HDMI接口模块,图像时序处理模块,rgb转dvi模块等。

2.算法硬件测试效果图预览

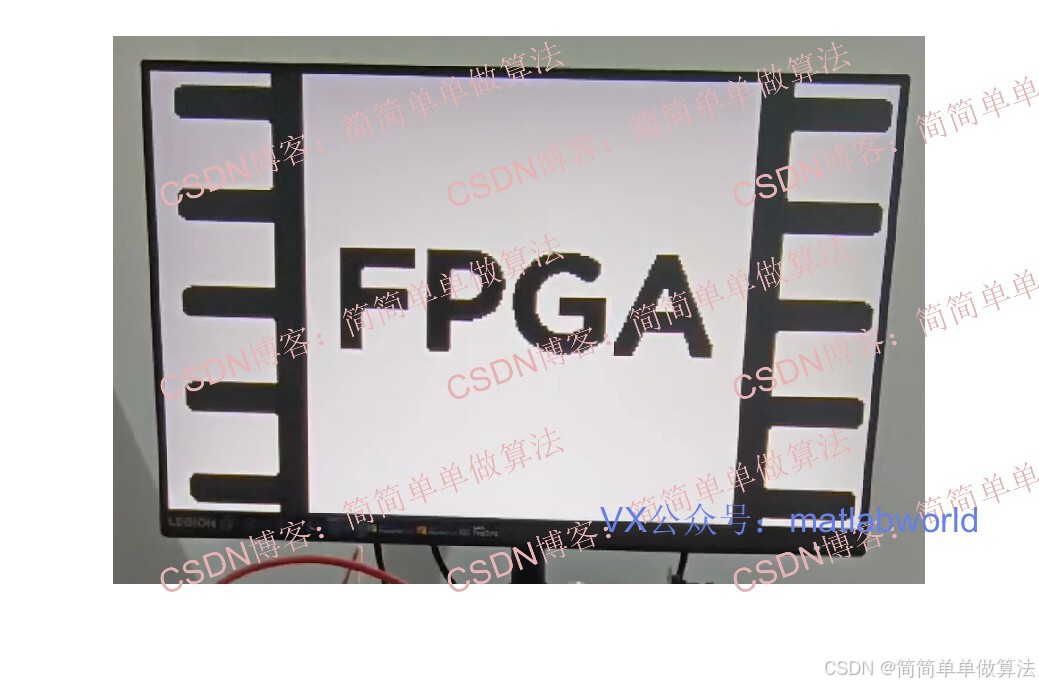

用显示器显示原二值图:

原图像二值图:

腐蚀后的图像二值图:

3.算法运行软件版本

vivado2022.2

4.部分核心程序

(完整版代码包含中文注释和操作步骤视频)

................................................................

wire[7:0] rgb_r_reg; //video red data register

wire[7:0] rgb_g_reg; //video green data register

wire[7:0] rgb_b_reg; //video blue data register

wire[7:0]doutR;

blk_mem_gen_R blk_mem_gen_0u1 (

.clka(clk), // input wire clka

.rsta(rst), // input wire [0 : 0] wea

.addra(addra), // input wire [17 : 0] addra

.douta(doutR), // output wire [7 : 0] douta

.rsta_busy()

);

wire[7:0]doutG;

blk_mem_gen_G blk_mem_gen_0u2 (

.clka(clk), // input wire clka

.rsta(rst), // input wire [0 : 0] wea

.addra(addra), // input wire [17 : 0] addra

.douta(doutG), // output wire [7 : 0] douta

.rsta_busy()

);

wire[7:0]doutB;

blk_mem_gen_B blk_mem_gen_0u3 (

.clka(clk), // input wire clka

.rsta(rst), // input wire [0 : 0] wea

.addra(addra), // input wire [17 : 0] addra

.douta(doutB), // output wire [7 : 0] douta

.rsta_busy()

);

wire[7:0]o_gray;

main_gray main_gray_u(

.i_clk (clk),

.i_rst (rst),

.i_image_R (doutR),

.i_image_G (doutG),

.i_image_B (doutB),

.o_gray (o_gray)

);

wire[7:0]o_binary_image;

wire[7:0]o_expansion;

fushi fushi_u(

.i_clk (clk),

.i_rst (rst),

.i_I0 (o_gray),

.o_binary_image (o_binary_image),

.o_expansion (o_expansion)

);

assign rgb_r_reg=(key==1'b0)?o_expansion:o_binary_image;

assign rgb_g_reg=(key==1'b0)?o_expansion:o_binary_image;

assign rgb_b_reg=(key==1'b0)?o_expansion:o_binary_image;

0X2_008m

endmodule 5.算法测试参数

parameter H_ACTIVE = 16'd1280; //horizontal active time (pixels)

parameter H_FP = 16'd110; //horizontal front porch (pixels)

parameter H_SYNC = 16'd40; //horizontal sync time(pixels)

parameter H_BP = 16'd220; //horizontal back porch (pixels)

parameter V_ACTIVE = 16'd720; //vertical active Time (lines)

parameter V_FP = 16'd5; //vertical front porch (lines)

parameter V_SYNC = 16'd5; //vertical sync time (lines)

parameter V_BP = 16'd20; //vertical back porch (lines)

parameter HS_POL = 1'b1; //horizontal sync polarity, 1 : POSITIVE,0 : NEGATIVE;

parameter VS_POL = 1'b1; //vertical sync polarity, 1 : POSITIVE,0 : NEGATIVE;6.硬件测试说明

具体的硬件操作步骤,可以参考作品中提供的视频步骤

如果不同开发板,系统的移植可以参考如下文章

7.算法理论概述

基于FPGA的图像形态学腐蚀算法实现主要依赖于图像处理的基本原理和数学形态学的基础知识。在图像处理中,形态学操作被广泛应用于各种图像处理任务,包括噪声消除、对象检测和识别、图像分割等。其中,腐蚀操作是形态学操作的一种基本形式,它有助于减小图像中明亮区域的大小。

首先,让我们了解一下图像形态学的基础知识。形态学操作通常在二值图像上进行,但是也可以扩展到灰度图像和彩色图像。在二值图像中,形态学腐蚀操作被定义为将一个结构元素(通常是一个小的矩形或圆形)在图像上移动,并将每个像素值替换为该像素值和结构元素覆盖区域的最小值。这样,在经过腐蚀操作后,图像中的明亮区域(或高像素值区域)会得到缩小。 具体来说,腐蚀操作的数学表达式可以表示为:

Erosion(f,I)=min{f(x+s),I(s)}(x)f(x+s)−I(s)min{f(x+s), I(s)}

其中,f是原始图像,I是结构元素,s是结构元素的位移。这个公式表示的是,对于每一个像素位置x,将结构元素中心对齐到位置x,并取结构元素覆盖区域的最小值作为输出图像在该位置的值。

在FPGA上实现图像形态学腐蚀算法时,可以采用硬件并行处理的方式,以提高处理速度。首先,将输入的图像数据存储在FPGA的内部RAM中。然后,通过一个并行处理器,将结构元素在图像上移动,并计算每个像素位置的输出值。最后,将计算出的输出数据存储在外部RAM中,或者直接用于后续的图像处理任务。

需要注意的是,在实现形态学腐蚀算法时,需要选择合适的结构元素形状和大小。不同的结构元素可能会导致不同的腐蚀效果。此外,由于形态学操作涉及到大量的数据运算,因此需要合理优化算法和硬件设计,以提高处理速度和效率。

总的来说,基于FPGA的图像形态学腐蚀算法实现需要结合图像处理的基本原理和数学形态学的基础知识,同时考虑硬件并行处理的特点和实际应用的需求。通过合理选择结构元素、优化算法和硬件设计等手段,可以实现高效的图像腐蚀操作。

8.算法完整程序工程

OOOOO

OOO

O

关注GZH后输入自动回复码:0025

或输入自动回复码:FPGA腐蚀