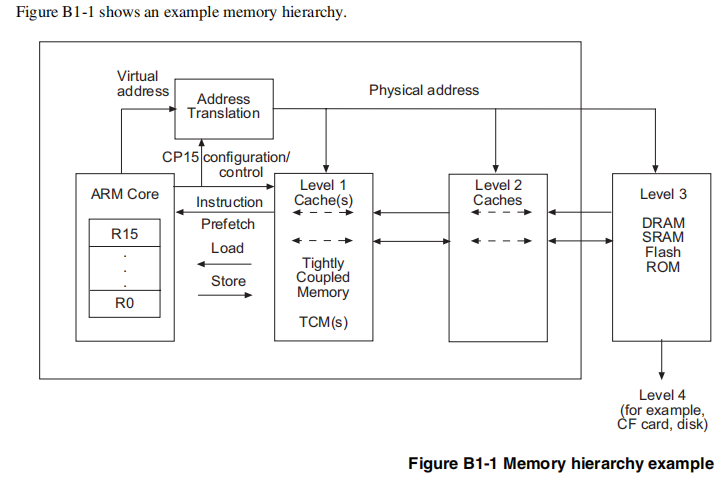

ARM系列处理器内存架构示意图:

在ARM多核处理器中,高速缓存一致性通过硬件一致性协议(MESI) 、系统级协调单元(SCU) 、缓存控制器(PL310) 以及 访存执行单元(LSU) 协同实现。以下是各组件的作用详解:

各组件作用对比表

| 组件 | 角色定位 | 核心功能 |

|---|---|---|

| MESI | 缓存一致性协议 | 定义缓存行四种状态(Modified/Exclusive/Shared/Invalid),通过状态转换和总线监听机制确保多核数据一致性 |

| SCU(Snoop Control Unit) | 系统级一致性协调器 | 位于多核互联总线上,仲裁各核心的监听请求,管理跨核一致性事务(L1-L1、L1-L2间),降低总线冲突 |

| PL310 | L2缓存控制器 | 实现共享L2缓存与各核心L1缓存的一致性管理,处理缓存行填充、回写、失效等操作 |

| LSU(Load-Store Unit) | 访存执行单元 | 执行load/store指令,负责地址转换、缓存访问、内存读写等实际数据搬运操作 |

MESI通过总线监听(Snooping)和状态机转换实现一致性:

- Modified(M):当前核心独占且已修改,其他缓存无效

- Exclusive(E):当前核心独占但未修改,其他缓存无效

- Shared(S):多个核心共享该数据,均为只读副本

- Invalid(I):缓存行无效,需重新加载

关键补充:LSU与LSQ的关系及作用

LSU(Load-Store Unit) 是处理器执行单元的一部分,负责所有访存指令的实际执行,包括:

- 地址计算和虚拟地址到物理地址的转换(通过MMU)

- 访问L1数据缓存(命中时直接读取/写入)

- 处理缓存缺失(触发缓存行填充)

- 执行内存屏障指令

- 与SCU交互完成一致性操作

LSQ(Load-Store Queue) 是LSU内部的一个关键子模块,专门负责:

- 访存指令重排序管理:在乱序执行中,跟踪load/store指令的依赖关系,确保程序顺序语义

- 写缓冲区管理:store指令先暂存在LSQ的写缓冲区,待提交时再更新缓存(避免过早暴露写操作)

- 内存屏障处理:执行DMB/DSB等屏障指令时,清空LSQ确保屏障前的所有访存完成

- 数据转发:检测store-load转发机会,避免不必要的缓存访问

关系说明:LSQ是LSU的组成部分,LSU是执行访存指令的完整功能单元,而LSQ专门处理访存指令的调度和顺序问题。在一致性机制中,LSU负责执行具体的缓存访问操作(如发起监听请求、更新缓存行状态),而LSQ确保这些操作的执行顺序符合内存模型要求。

完整一致性工作流程(以写操作为例)

- Core0执行store指令:LSU计算地址,检查L1缓存状态

- LSQ管理顺序:若存在依赖关系,LSQ会hold该store指令,等待前序访存完成

- 发起一致性请求:若缓存行处于Shared状态,LSU通过SCU向总线广播"读-修改所有权"请求

- SCU协调:SCU仲裁请求,向其他核心发送监听消息

- 其他核心响应:其他核心的LSU监听到请求,将对应缓存行标记为Invalid,通过SCU返回响应

- 状态转换:Core0获得独占权,缓存行状态变为Modified

- 数据写入:LSU将数据写入L1缓存(或LSQ的写缓冲区,待提交时更新)

- PL310参与:若涉及L2缓存,PL310会跟踪L2缓存行的状态,必要时进行回写或失效操作

重要说明

- SCU的定位:SCU(Snoop Control Unit)不是专门针对L1缓存进行一致性管理的单元,而是系统级的跨核一致性协调器,负责管理所有缓存层次(包括L1、L2甚至L3)之间的全局一致性事务。

- LSU与LSQ的层级关系:LSQ是LSU内部的子模块,两者共同完成访存指令的执行和顺序管理

- PL310的作用范围:PL310主要管理共享L2缓存的一致性,与各核心的L1缓存控制器(实现MESI)协同工作

- MESI协议的基础性:MESI定义了缓存行的状态规则,所有其他组件(SCU、PL310、LSU)都需要遵循该协议进行状态转换

总结:MESI协议提供状态机规则,SCU协调跨核一致性事务,PL310管理L2缓存一致性,LSU执行实际访存操作,LSQ(作为LSU的一部分)保障访存顺序。五者协同工作,在保证数据一致性的同时最大化多核性能。

注:不同ARM处理器型号的具体实现可能有所差异,但上述组件的基本功能定位和协作关系是通用的设计原则。