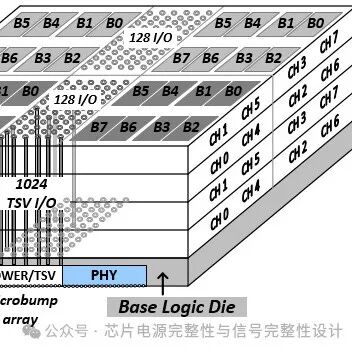

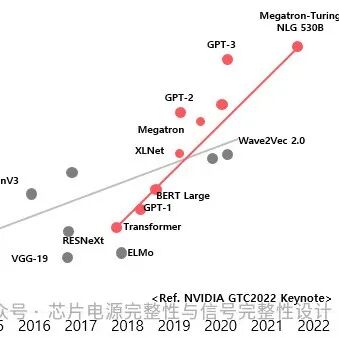

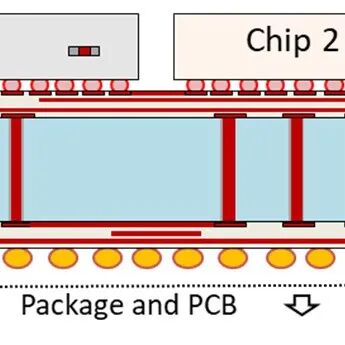

人工智能、机器学习、汽车电子和5G等前沿应用均需高带宽、高性能、低功耗和低延迟,同时需保持或降低成本。由于设计、原型制作和工艺的高昂成本,采用单片系统级芯片(SoC)方案实现这些产品已不经济,且复杂SoC解决方案的设计周期较长。异构集成[1]成为更快速且低成本的替代方案。通过硅中介层、硅桥或有机基板上的高密度扇出技术,封装级异构集成可满足扩展需求并缩短设计周期。尽管异构集成优势显著,但因小芯片和I/O接口的多样性,其实际应用仍具挑战。标准化芯片间接口的努力将加速模块化系统的设计周期。

HBM2/3和AIB是当前最流行的接口。HBM用于连接CPU/GPU/ASIC与DRAM存储器,适用于高性能计算、图形和网络应用;AIB则用于逻辑芯片间的互连(如ASIC/FPGA与加速器芯片或光电收发器芯片)。

HBM2标准包含8个通道,每通道128位宽度,引脚数据速率为2Gbps。最新HBM标准支持3.2Gbps/引脚,总带宽可达409.6GB/s,需在约6mm的芯片边缘区域内路由约1700条线。

AIB标准支持24个通道,每通道包含80个发送(Tx)和80个接收(Rx)信号,数据速率2Gbps/信号,总带宽达3.84Tbps,需在8mm边缘区域内路由超过3900条线。

HBM和AIB可通过硅中介层、EMIB或高密度有机基板实现。下面将探讨基于聚合物HD-FOWLP RDL实现这些接口的电气设计挑战。

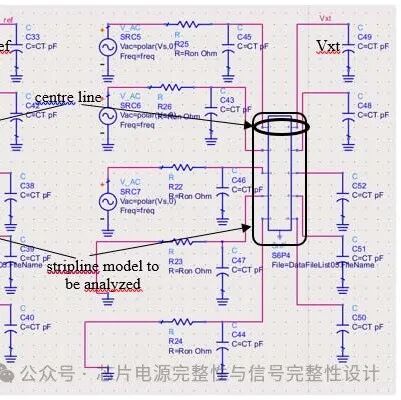

HD-FOWLP堆叠最多支持6层金属,结合精细线宽可实现高密度宽总线结构。例如,2um×2um线宽与2um间距的双层金属即可在6mm边缘内路由HBM接口。若采用1um×1um线宽与1um间距,密度可翻倍,但需考虑电气性能。这儿分析两种堆叠拓扑:

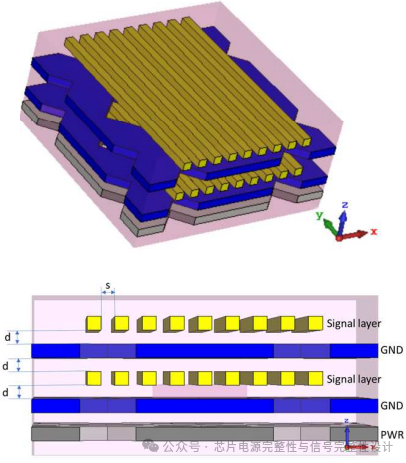

-拓扑一(图1):顶层和第三层用于信号布线,第二层和第四层为地平面,第五层为电源层。

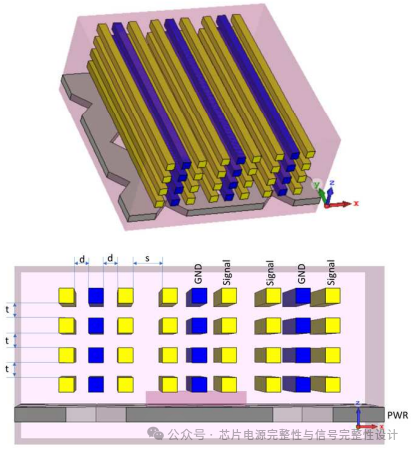

-拓扑二(图2):前四层采用地-信号-信号(GSS)模式交替布线,第五层为电源层。

图1:第一种拓扑结构------5层HDFOLWP堆叠的三维视图和横截面视图;s为相邻信号线之间的距离;d为信号层与地之间的距离。

图2:第二种拓扑结构------5层HDFOLWP堆叠的三维视图和横截面视图;s为相邻信号线间距;d为信号与地间距;顶层四层采用GSS模式,第五层为电源。

减少金属层数可降低成本。以HBM为例,2um线宽与2um间距下,拓扑一需5层(2信号、2地、1电源);1um线宽与1um间距下,仅需3层(1信号、1地、1电源)。拓扑二在1um线宽下可进一步减少至2层。但需通过信号完整性分析选择最优方案。

信号线的频域分析

A.信号线的性能区域

细截面互连的直流电阻极高(如2um×2um铜线电阻约4.31Ω/mm,1um×1um线电阻增至四倍)。需通过衰减曲线和频率变化分析其特性。

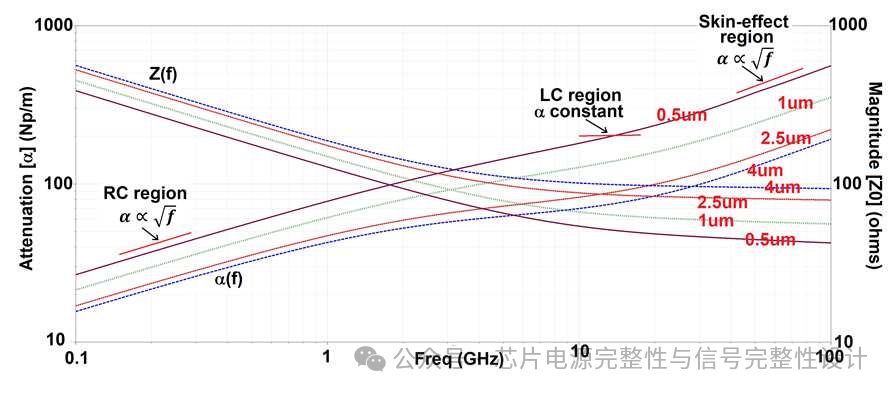

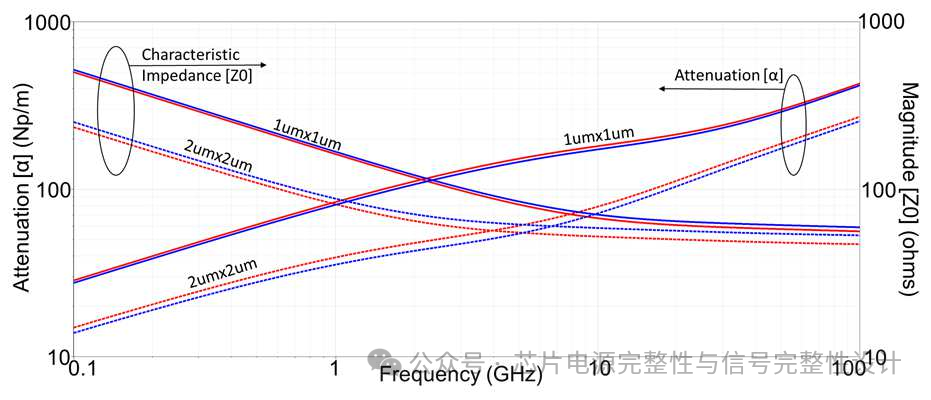

图3显示了1um×1um线在拓扑一顶层的衰减曲线(左轴)和特性阻抗(右轴),介电层厚度d分别为0.5、1、2.5和4um。结果显示,薄介电层因邻近效应增强导致衰减更大,且RC(电阻-电容)与LC(电感-电容)区域的边界频率更高。仿真假设聚合物介电材料介电常数为3.2,损耗角正切为0.02。在1GHz(HBM2和AIB的奈奎斯特频率),特性阻抗范围从d=0.5um的120Ω到d=4um的190Ω。

图3:1um×1um导线在第一种拓扑结构顶层布线时的衰减曲线(左轴)和特性阻抗(右轴)随频率的变化;d=0.5、1、2.5和4um。

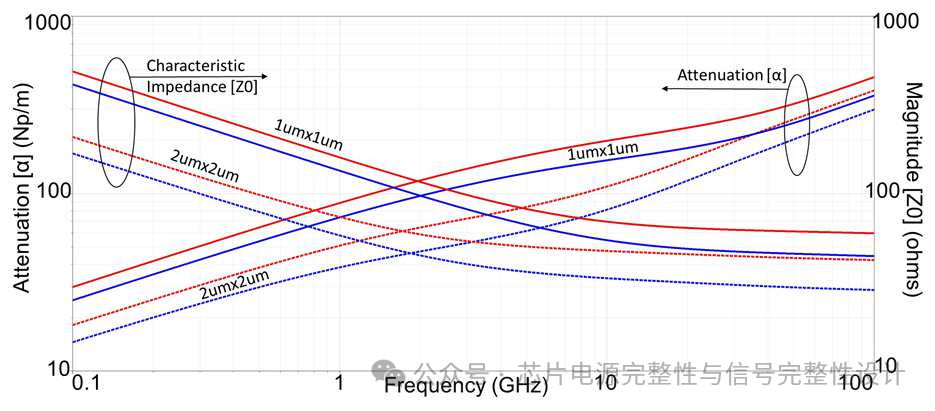

图4对比了1um和2um线在拓扑一中的衰减(α)和特性阻抗(|Z0|)。增大线宽可降低衰减和阻抗,因电阻减小且电容增加。顶层(微带线)的衰减较低但阻抗较高,第三层(带状线)则相反。

图4:1um×1um(实线)和2um×2um(虚线)导线在拓扑一中随频率的衰减(α)和特性阻抗(|Z0|)变化。

图5展示了拓扑二的类似分析。由于接地层分布均匀,不同层的性能差异较小。2um线在1GHz时特性阻抗为82Ω,但需频率超过6GHz才能稳定。

图5:1um×1um(实线)和2um×2um(虚线)导线在拓扑二中随频率的衰减和特性阻抗变化。

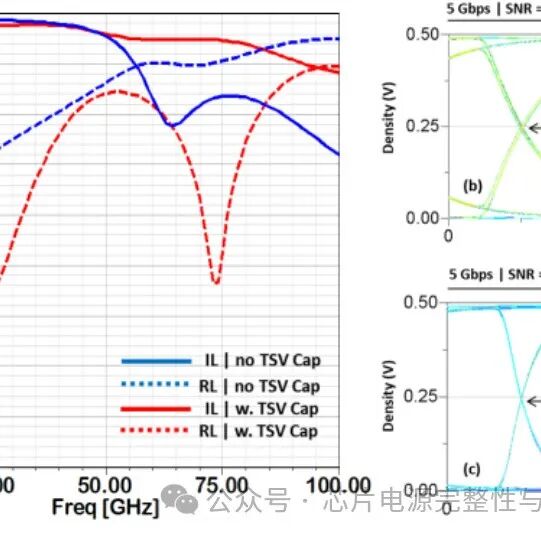

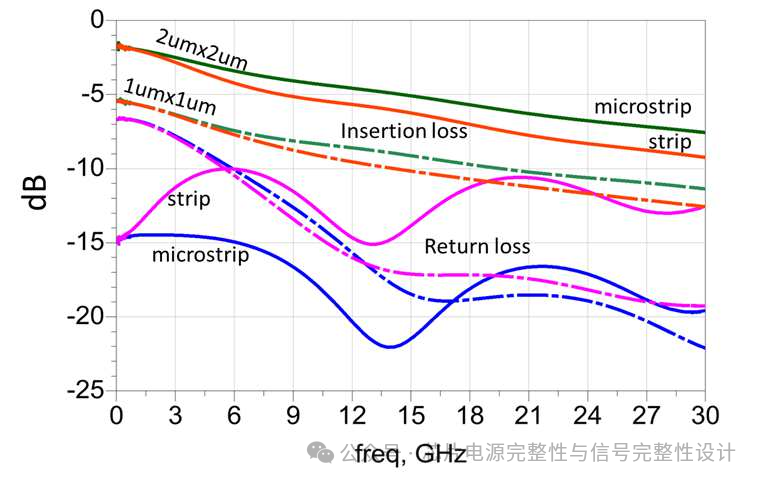

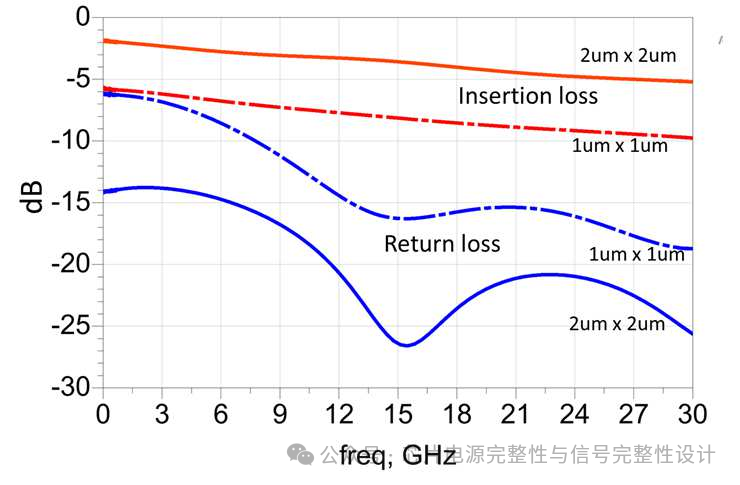

B.信号线的S参数响应

图6和图7分别展示了拓扑一和拓扑二中5mm长线的插入损耗与回波损耗。1um线因阻抗失配更严重,插入损耗和回波损耗均高于2um线。

图6:拓扑一中2um×2um和1um×1um导线的回波损耗与插入损耗。

图7:拓扑二中2um×2um和1um×1um导线的回波损耗与插入损耗。

四层RDL层的数据

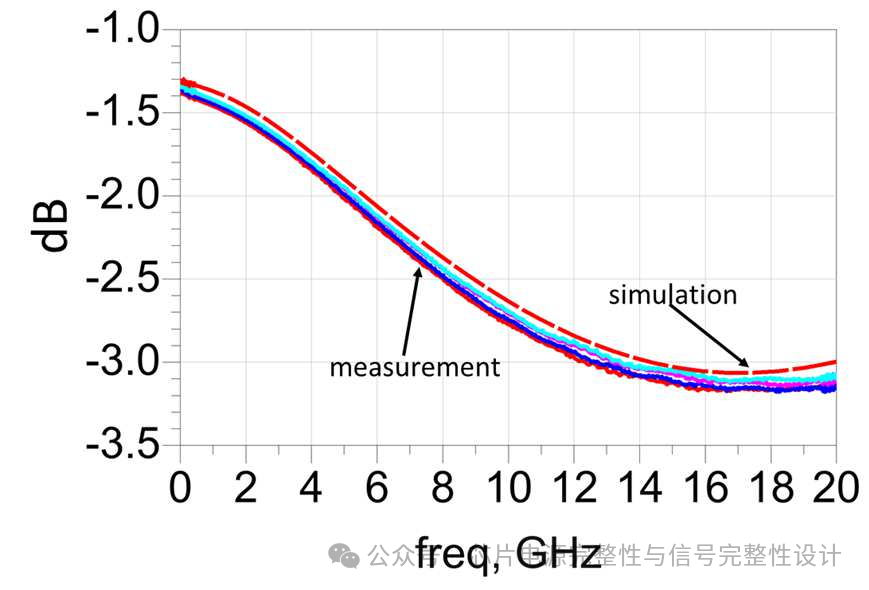

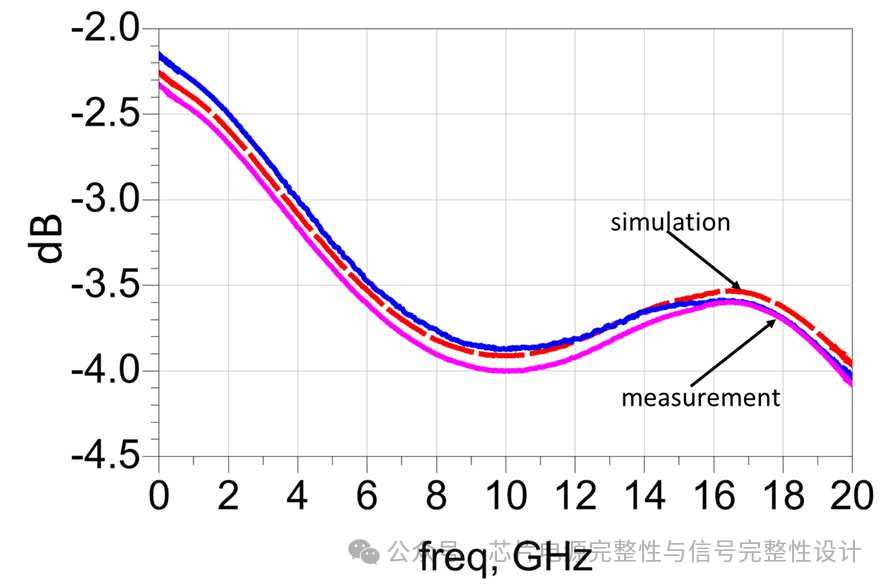

基于拓扑一的四层测试载体通过高频测量验证。2um×2um截面线的仿真与实测数据(图8、图9)吻合良好,验证了模型的可靠性。

图8:3mm长2um×2um导线的插入损耗------仿真与实测对比。

图9:5mm长2um×2um导线的插入损耗------仿真与实测对比。

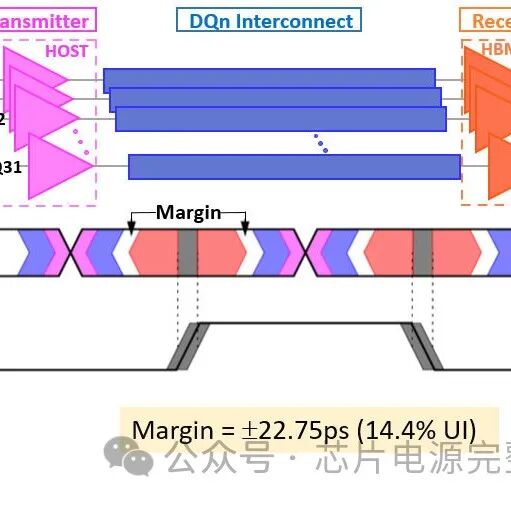

HD-FOWLP上的HBM与AIB总线实现

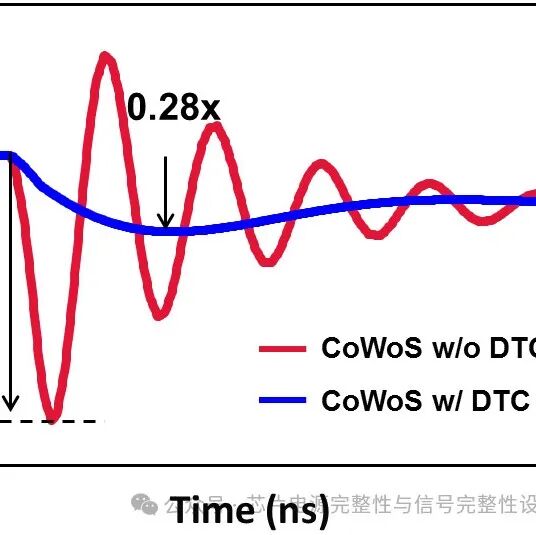

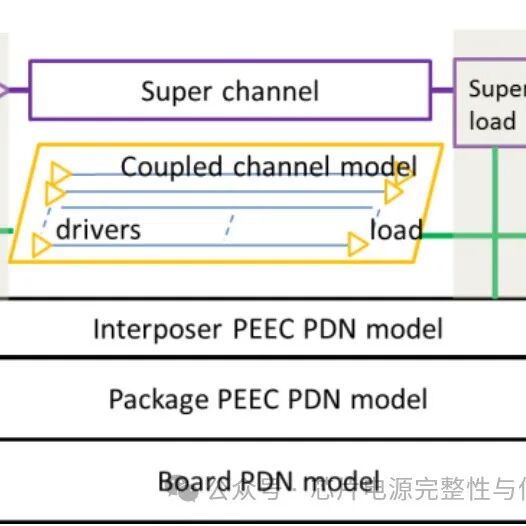

HD-FOWLP互连工作在RC区域或RC-LC过渡区,特性阻抗随频率大幅变化,难以实现宽带匹配。需结合瞬态时域仿真评估实际驱动器和负载下的性能。

A.HBM接口

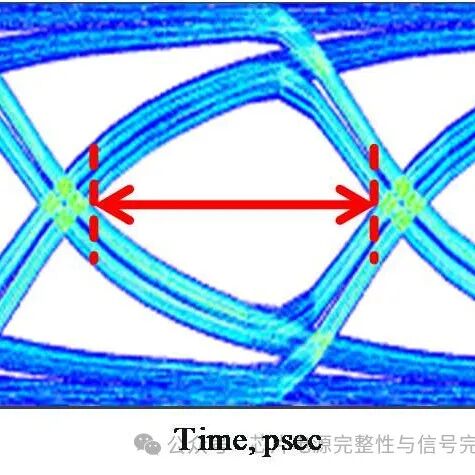

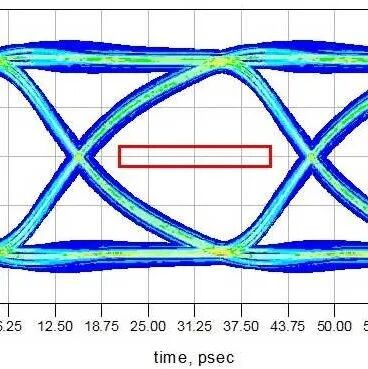

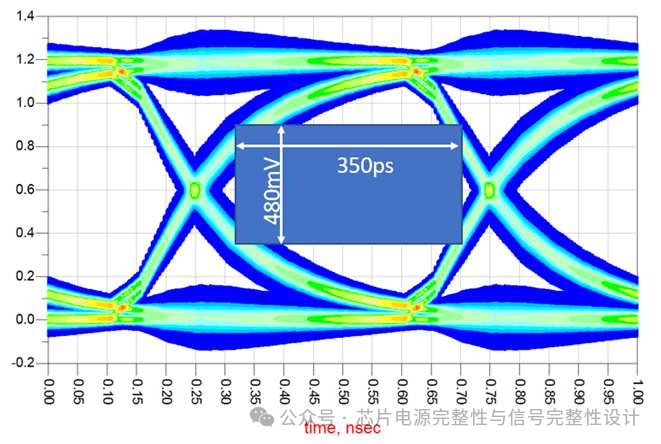

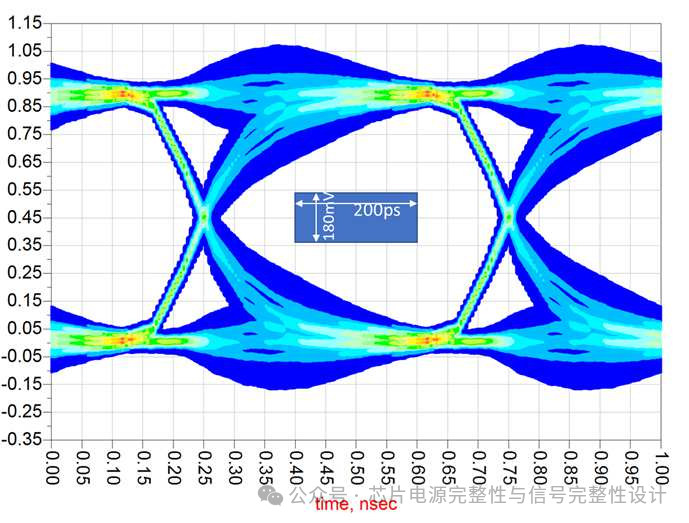

拓扑二采用1um线宽时,仅需2层即可实现HBM接口,但5mm长线的眼图(图10)未满足HBM2的0.7UI宽度和480mV高度要求。

图10:拓扑二采用1um×1um导线的HBM接口眼图。

B.AIB接口

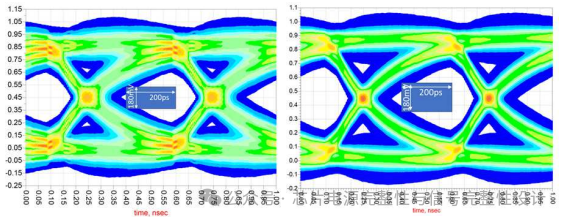

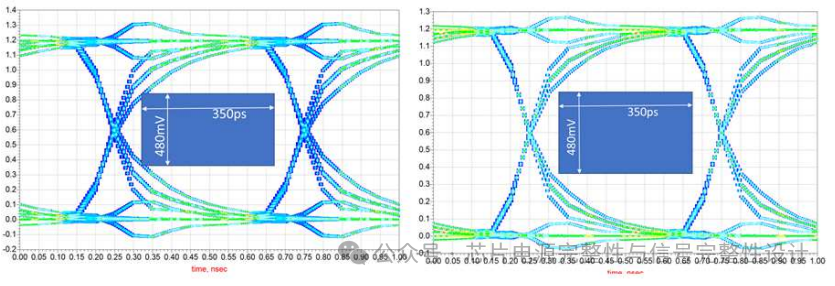

1um线宽需3层金属,10mm长线的眼图(图11)不符合AIB的0.4UI和180mV要求,但缩短至7mm可满足。

图11:拓扑一(左)和拓扑二(右)采用1um×1um导线的AIB接口眼图。

C.优化设计

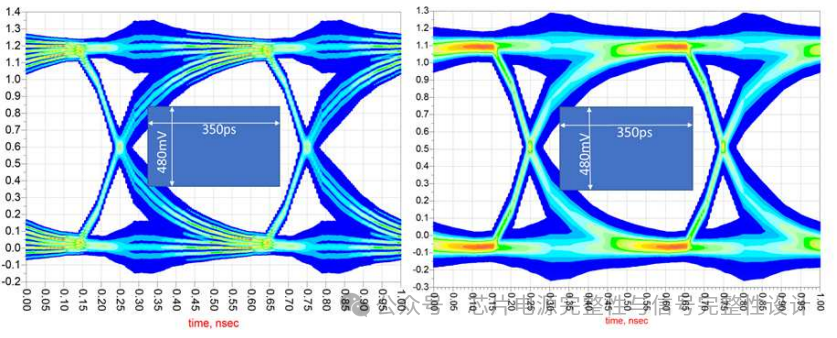

增大线宽至2um可改善性能。拓扑一需5层金属,HBM眼图(图12)仍不达标,但AIB接口(图13)可满足时序要求。

图12:拓扑一(左)和拓扑二(右)采用2um×2um导线的HBM接口眼图。

图13:拓扑一采用2um×2um导线的AIB接口眼图。

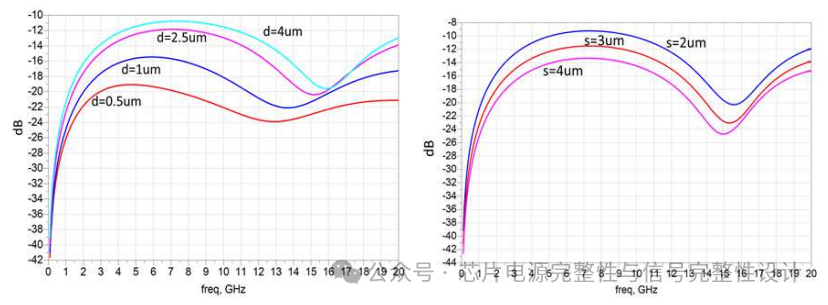

调整线间距是降低串扰的有效方法。图14显示,2um线间距增至4um后,5mm长HBM总线的眼图(图15)符合规范,且仍可在2层金属内完成布线。

图14:2um×2um导线在拓扑一顶层的耦合变化:左(仿真)------固定线距s=2um,调整地间距d;右(实测)------固定d,调整s。

图15:2um×2um导线在s=2um(左)和s=4um(右)时的HBM接口眼图。

结论

上面分析了基于HD-FOWLP实现HBM和AIB接口的电气挑战。两种拓扑结构均适用,但需权衡层数、线宽和间距。通过时域仿真和实测验证,优化设计可满足规范要求。

历史文章精选

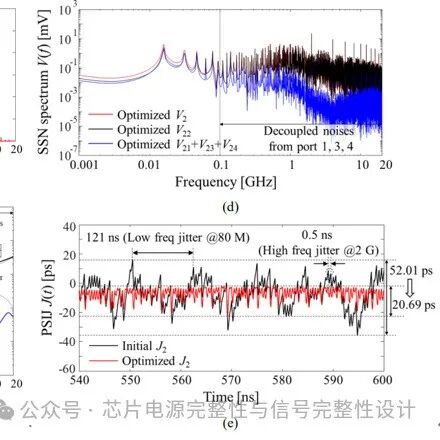

HBM I/O接口中电源供应引起的抖动(PSIJ)分析与优化

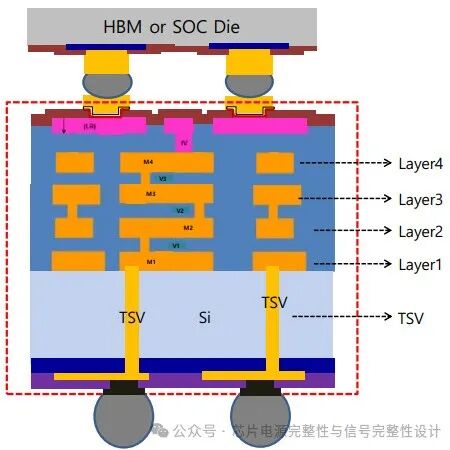

面向HPC平台应用的HBM电源完整性/信号完整性分析与设计方法

HBM2E 信号完整性SI及timing budget的分析

基于2.5D Si interposer设计的HBM3-SOC D2D SIPI设计