Chapter 2 Linear Regulators

2.1 INTRODUCTION

voltage reference没法带载, 即拉电流, 输出就垮. voltage regulator可以带负载电流.

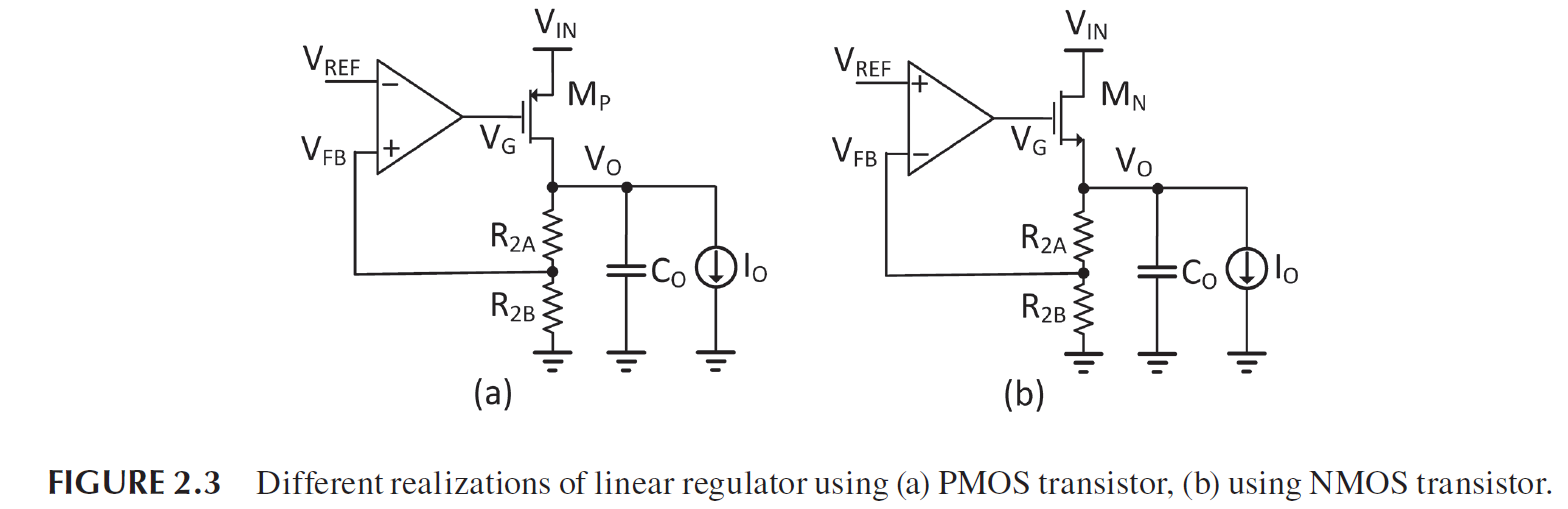

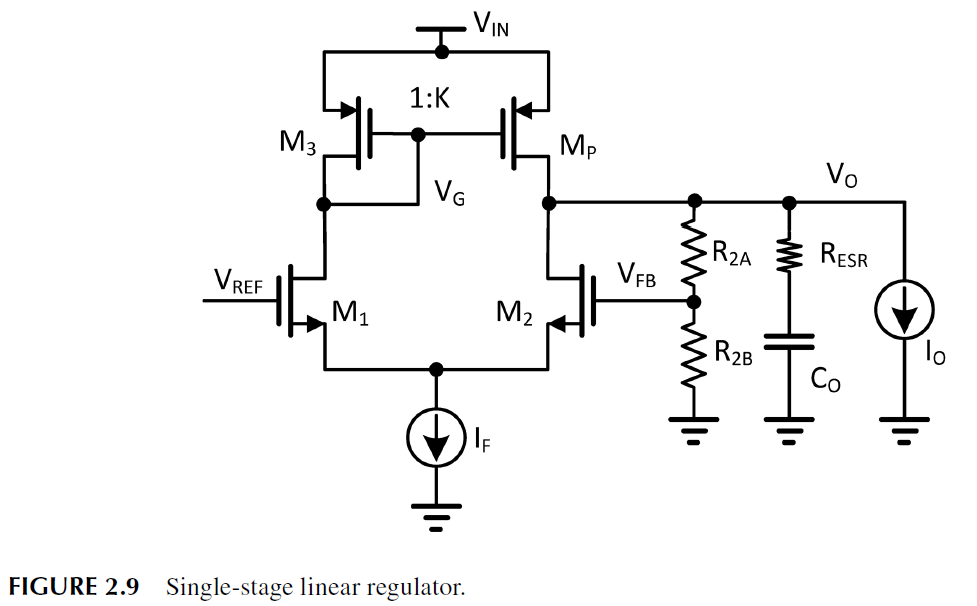

典型用MOS管做开关的linear regulator如下图所示.

2.2 CLASSIFICATIONS OF THE LINEAR REGULATORS

2.2.1 BASED ON THE DROPOUT VOLTAGE

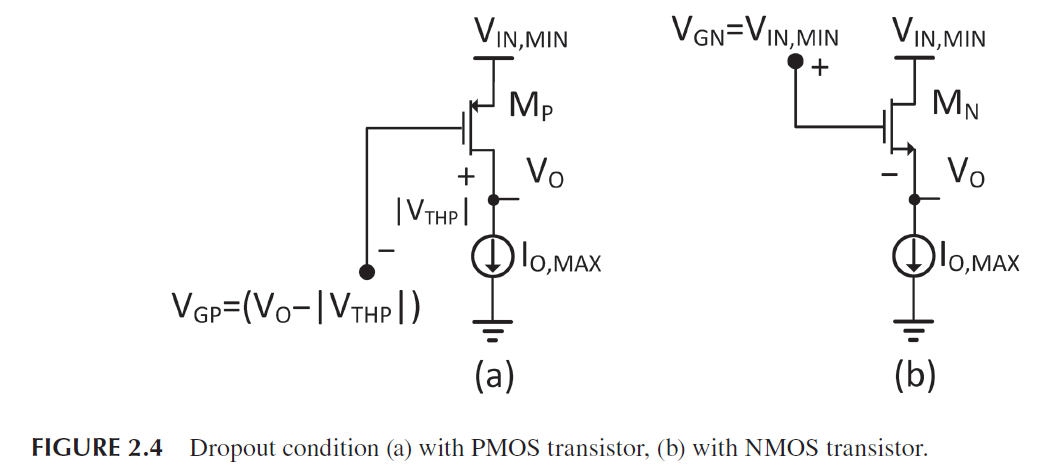

根据Vin和Vout压差, linear regulator 可分为 low dropout (LDO) (典型200mV以内) regulator和high dropout (500 mV) regulator.

以PMOS为例, overdrive电压 Vov = |Vgs| - |Vth|. 为保持PMOS处于饱和区, Vgp可比Vout最多低Vth, 和dropout电压类似.

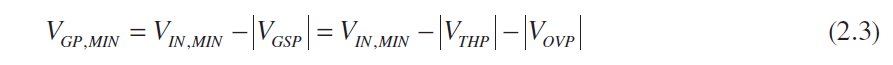

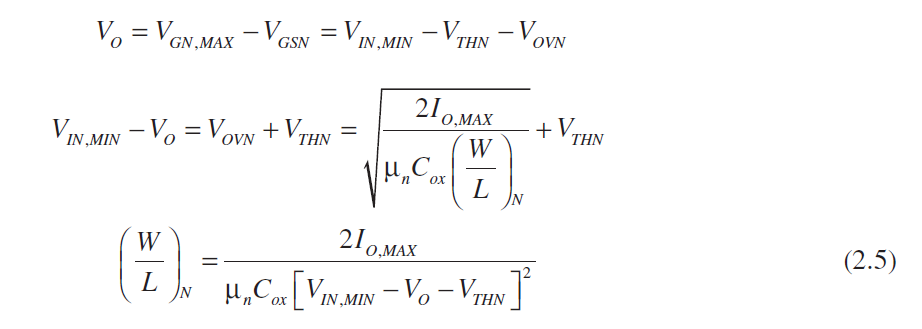

因此可得电流电压公式, 和功率管宽长比.

因此 PMOS LDO的dropout 电压 Vin-Vout 等于overdrive电压,即Vov = |Vgs| - |Vth|.

对于NMOS LDO, 假设Vgn最多达到Vin,min. dropout电压为VIN,MIN − VO.

NMOS的dropout电压比PMOS多Vth, 因此不适应于low dropout应用.

从面积考虑让MOS处于饱和区-线性区边界, 节省面积. 如果处于深饱和区, size和成本太高.

2.2.2 Based on Output Capacitor

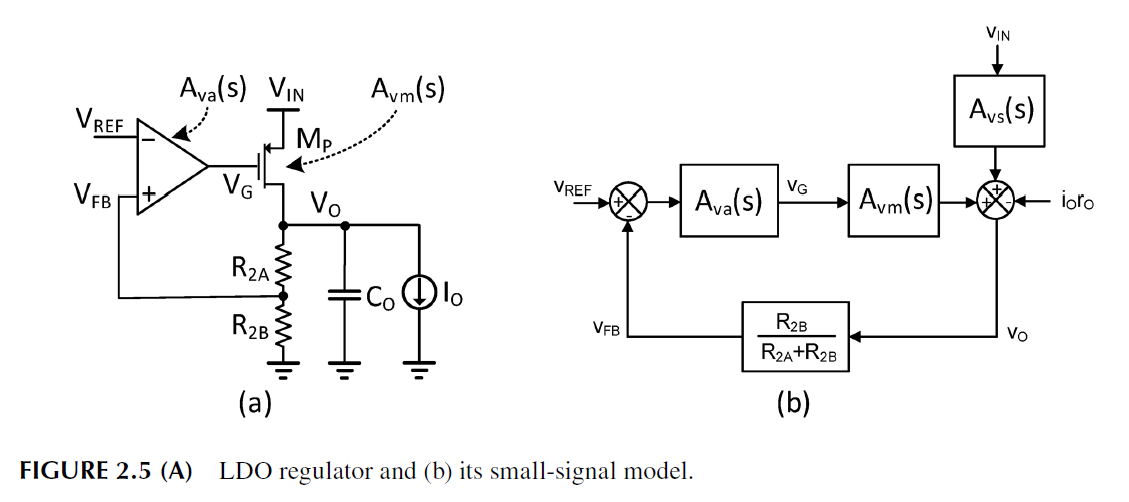

LDO分为有片外电容和无片外电容-Capless. 环路小信号图为Fig 2.5

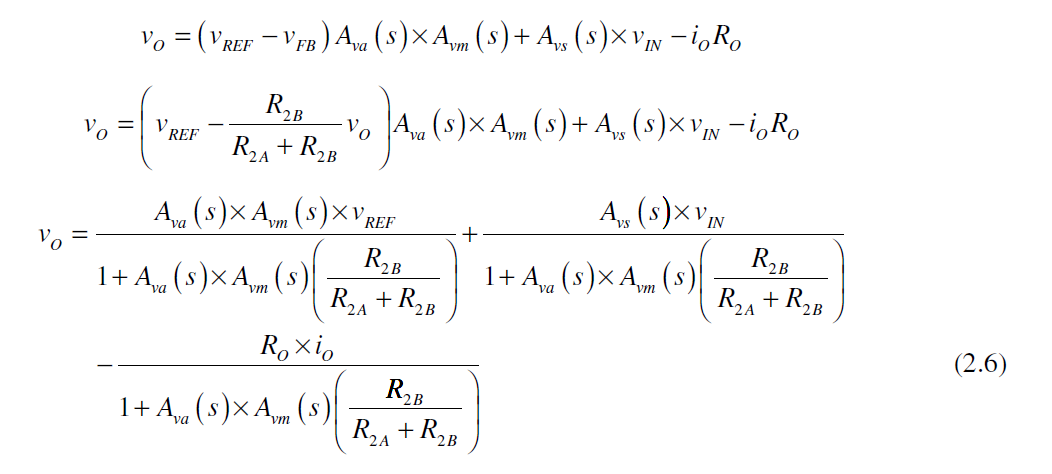

输出Vo表达式为

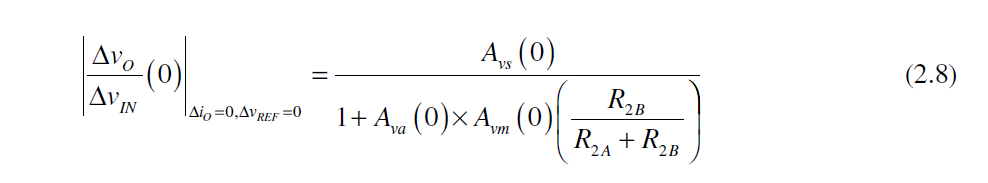

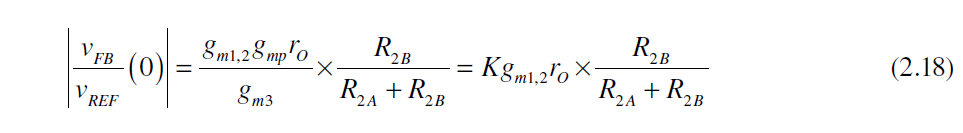

forward DC gain为Ava(0)Avm(0). feedback系数为R2B/(R2A+R2B), Loo Gain为Ava(0)Avm(0) R2B/(R2A+R2B). Loop gain越大, Vref和Vfb的差值越小, Vout随Vin和io的变化越小.

2.4 SPECIFICATIONS OF THE LINEAR REGULATOR

2.4.1 Load Regulation

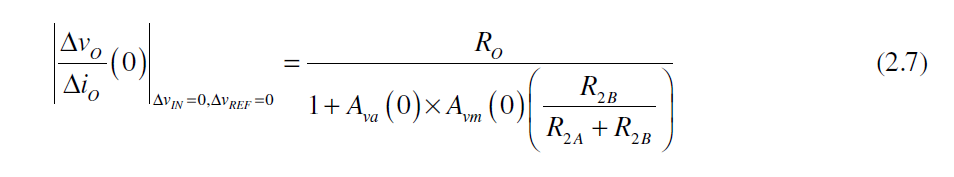

load regulation定义为Vo随着io的变化率. 为了减小vo随着load变化, 需要提高loop DC-gain.

2.4.2 Line Regulation

line regulation定义为Vo随着Vin的变化率. 为了减小vo随着vin变化, 需要提高loop DC-gain.

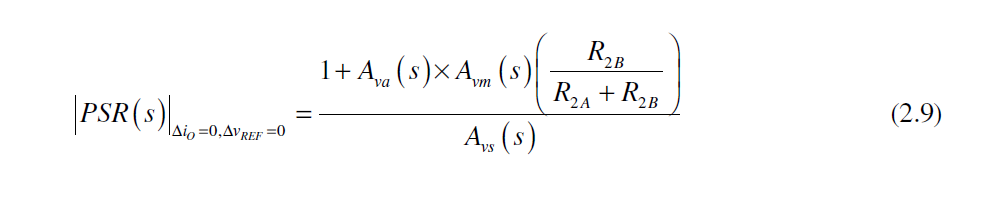

2.4.3 Power Supply Rejection

PSR统计Vout在特定频率范围随着Vin的变化. 例如 60dB at 10KHz.

2.4.4 Settling Time, Overshoot and Undershoot

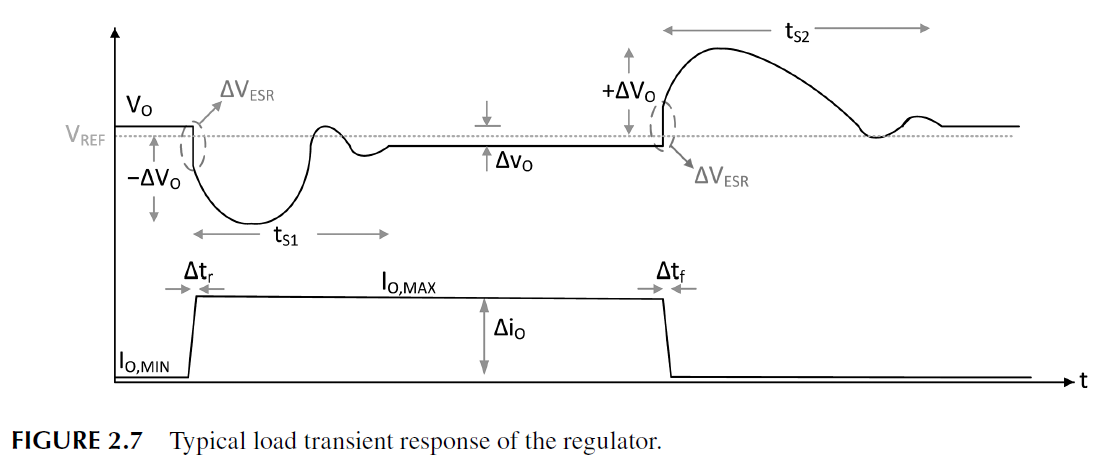

当负载变化较小时, settling time由小信号环路带宽bandwidth决定. 当发生大负载变换时, 由于Vfb和Vref差异大, 控制环路进入大信号领域, 环路的slew rate纠正error , 当error 电压减小后, 环路小信号带宽决定setting time. 因此大负载变化时, settling time是环路slew rate+小信号带宽决定.

如下图所示, 上冲和下冲 time由于电路设计不同, 常会有区别. 发生瞬态跳变时, undershoot和overshoot电压一开始由ΔVESR = ΔIO∙RESR 决定, 根据环路响应速度, Vout继续恶化. 一般undershoot和overshoot目标为稳态电压的2~5%.

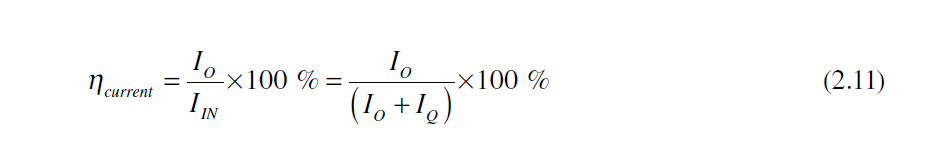

2.4.5 Power Efficiency and Current Efficiency

对于LDO, 其效率约等于输出电压/输入电压.

2.5 Evolution Of The Linear Regulator Topologies And Their Small-Signal Modeling

2.5.1 Single-stage topology

2.5.1.1 With PMOS Power Transistor

最简单的PMOS单级LDO如下图所示.

M3和MP的比例为1:K, 也因此输出能提供最大K*IF的电流. 上面结构只在IM1=IM2=0.5IF时没有系统误差电压, 此时Iout=0.5 * K *IF.

2.5.1.1.1 Fixing the DC Operating Point

为了减小input offset, M1和M2要有相同电流. M1电流为Io/K, M2电流为IF-Io/K. M1和M2的gm越大, 其offset越小.

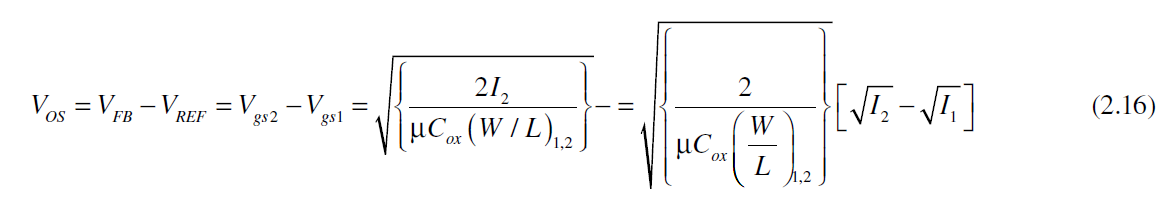

Vos为输入对管Vgs之差.

2.5.1.1.3 AC or Small-signal Analysis and Compensation Strategy

Case-1: With-capacitor Single-stage Regulator

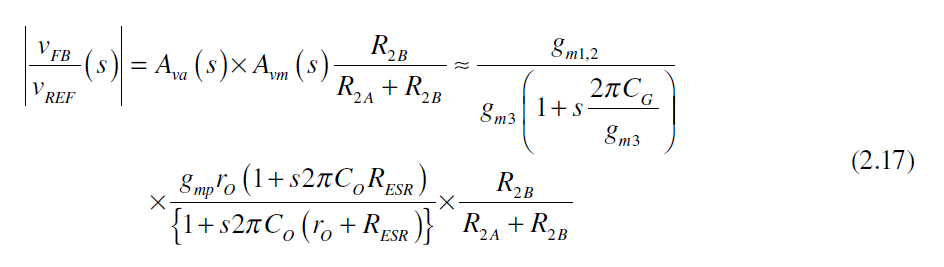

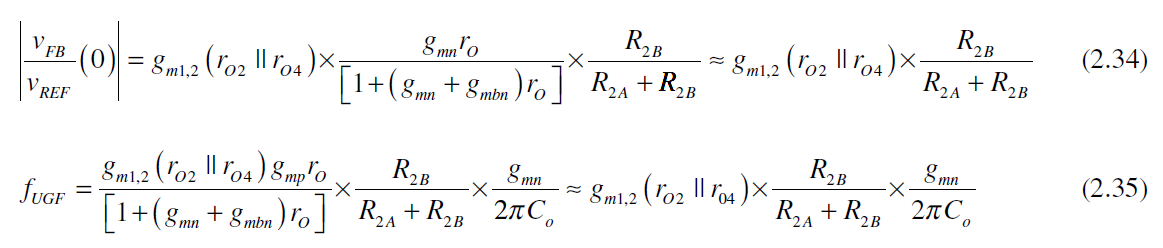

带电容的单级LDO, 环路Loop gain为.

其中Cg为Vg处的寄生电容, 大约为Mp的gate电容, Cg=Cox*W * L, 包括Cgs和Cgd.

Loop DC gain为

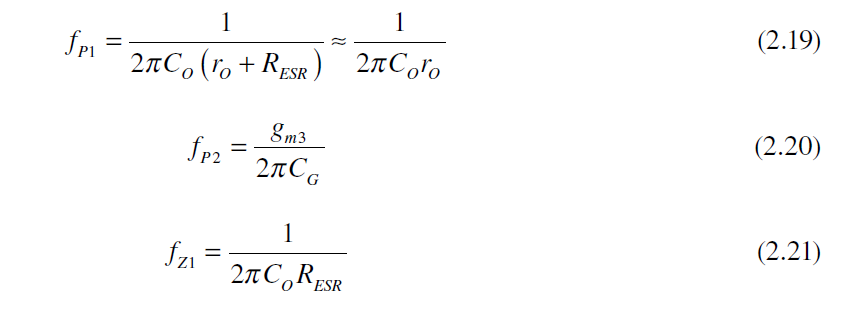

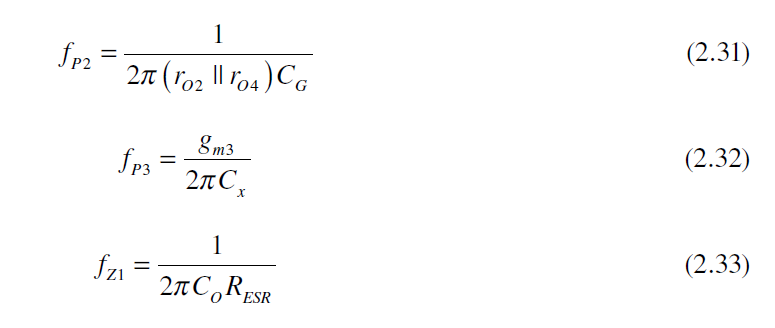

主极点fp1在输出, 零极点位置为

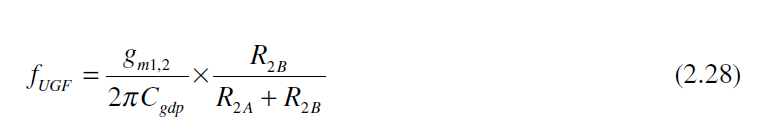

GBW 或者UGF (Unity gain frequency)为DC gain × fp1

当负载iLoad减小时, ro = 1/λiLoad变大, gm1,2∝√IO, 因此DC-gain变大. fp1变小. GBW变小. 一般把fz1和fp2放到环路带宽以外.

Case-2: Capacitor-less Single-Stage Regulator

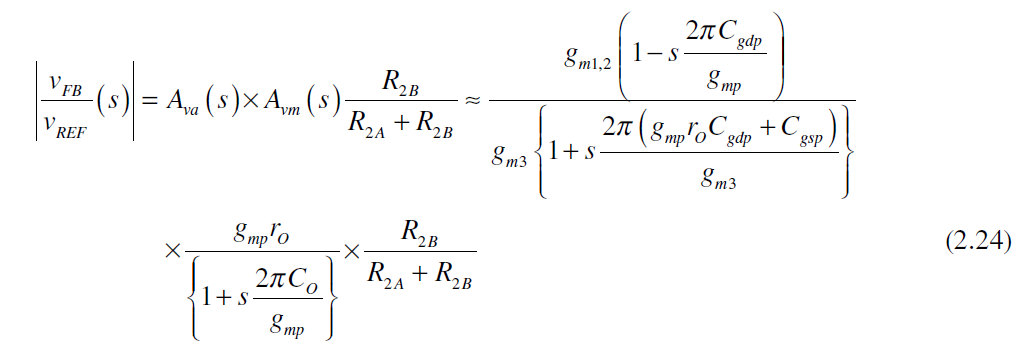

对于Capless LDO, Cout只有pF级别. 主极点在Vg处, MP处形成miller效应电容, 等效电容值Cg=gmp *ro *Cgdp+Cgsp. miller效应带来极点分离, 在高频, Cgdp short, 输出阻抗变为1/gmp. 同时miller效应引入右零点. Capless LDO的loop gain为

主极点在Vg处, 次极点在输出Vo处, 次级点和右零点需要远大于GBW.

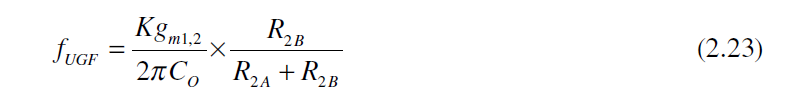

unity gain frequency:

MP处于饱和区时, fugf, fp2和fz1 与I0\sqrt{I_0}I0 成正比,

2.5.1.1.4 Large-signal Analysis

在极大负载下, EA运放饱和, 一些管子进入线性区, regulator取决于slewing. iLoad负载激增, Vout跌落, M2关断, M1和M3流过IF, Vg fall, 调压速率为IF/Cg. Vout上升, 只能靠IF下拉, 速度很慢.

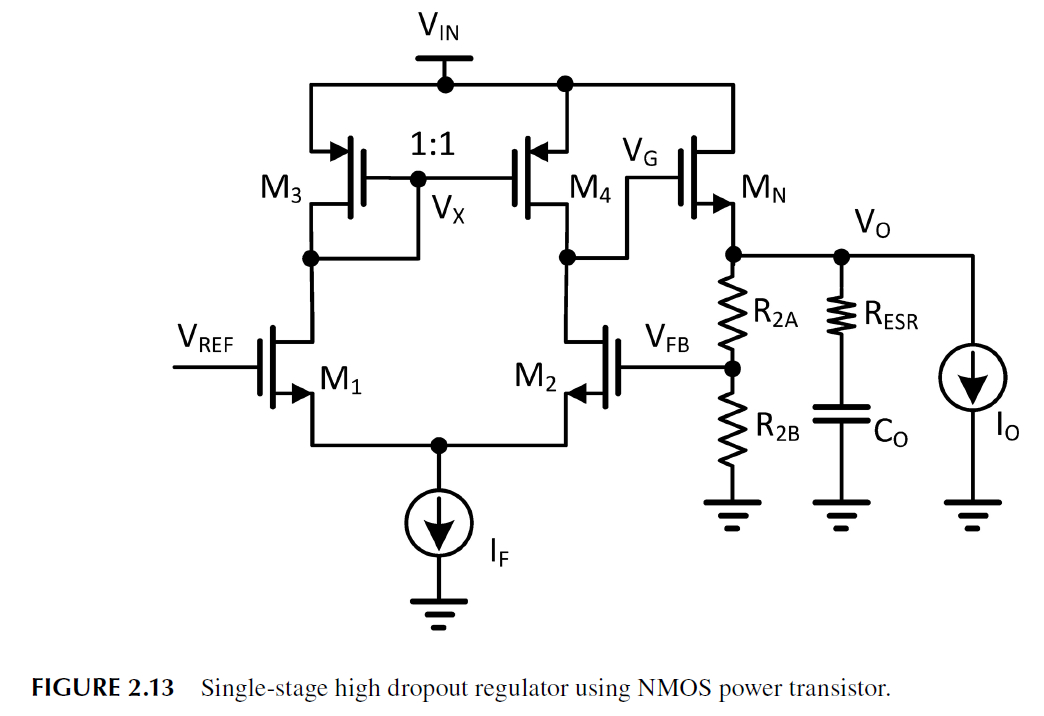

2.5.1.2 With NMOS Power Transistor

NMOS功率管LDO结构如下, 采用source follower结构.

2.5.1.2.1 AC or Small-signal Analysis And Compensation Strategy

Case-1: With-capacitor Single-stage Regulator

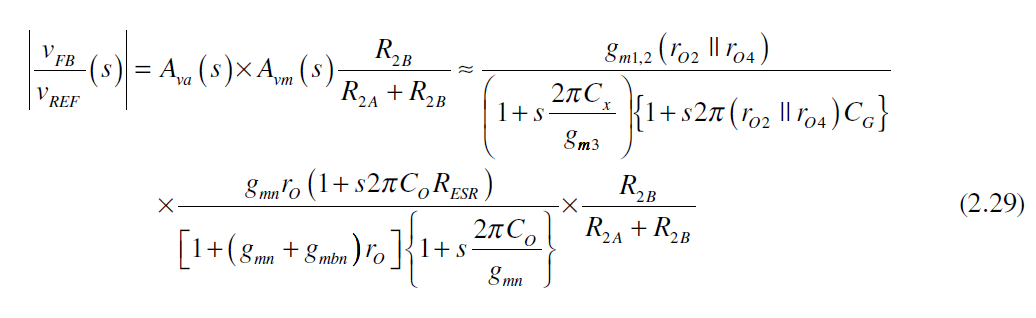

带电容的Loop Gain为

主极点在输出处, Rout=1/gmn, 需要Co >> Cg

次极点在Vg处

DC gain和ugf为

Case-2: Capacitor-less Single-stage Regulator

对于Capless LDO, Co很小, 输出Rout小, 因此主极点在Vg处, 次极点在Vout. UGF为. 次级点和零点几乎不随着iLoad变化.

2.5.1.2.2 Large-signal Analysis

对于大信号跳变, slew rate依然是If/Cg.

对于一级LDO, 补偿简单,因为极点少而且分离. 但DC gain差, 因此Vout精度较差.

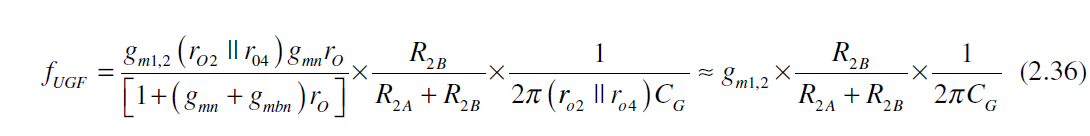

2.5.2 Two-stage Topology

为了提高DC gain可用2级联结构, 如下图所示. 差分结构+CS放大. R2A/B作为leakage path, 防止MP进入深亚阈值区.

2.5.2.1 AC or Small-signal Analysis and Compensation Strategy

Case-1: With-capacitor Two-stage Regulator

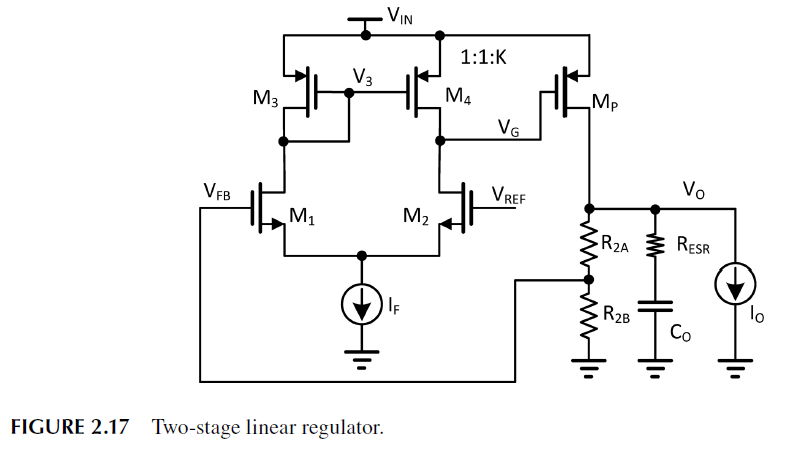

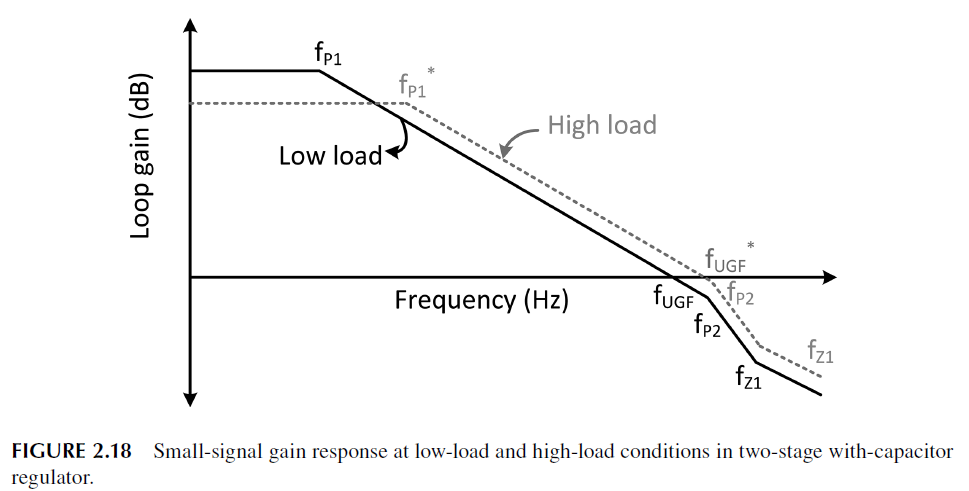

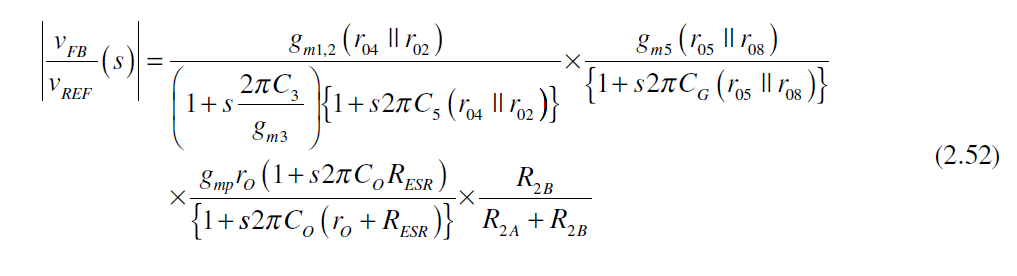

带外围电容的Loo Gain传函为下式, 其中C3和Cg为gate处电容.

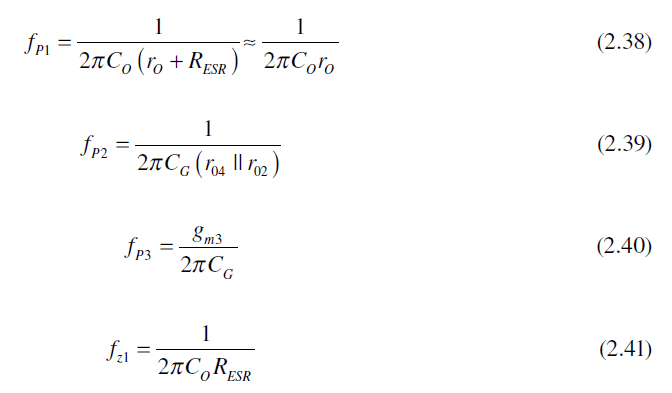

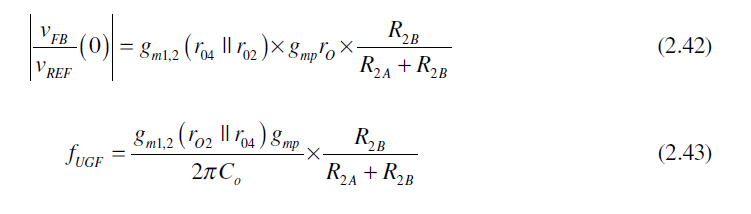

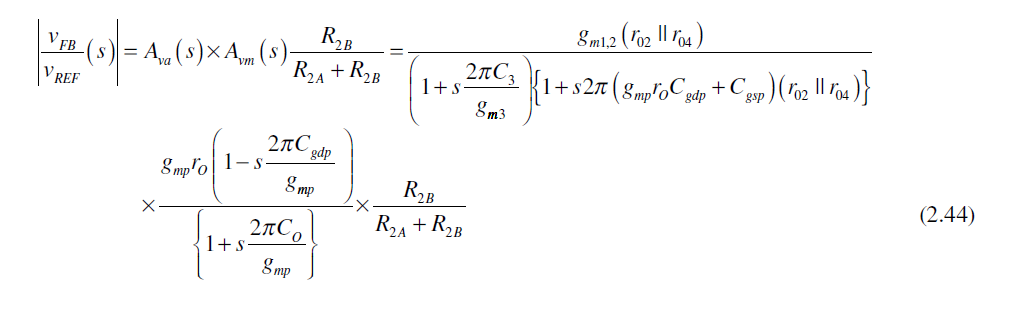

主极点fp1在Vout处, 次级点fp2在Vg处, 注意两极点位置可能较近, 零极点分布为

DC gain和UGF为下式

随着iLoad增加, DC gain减小, UGF增加, 更靠近次级点, 重载下补偿更困难. Cout越小, 越难补偿.

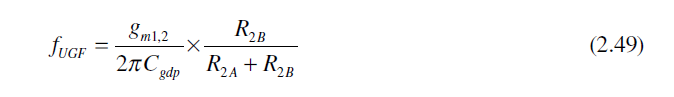

Case-2: Capacitor-less Two-stage Regulator

对于Capless LDO, 功率管的miller效应, 让MOS Vg处为主极点, 次极点为Vout处. ro=Vo/Io.

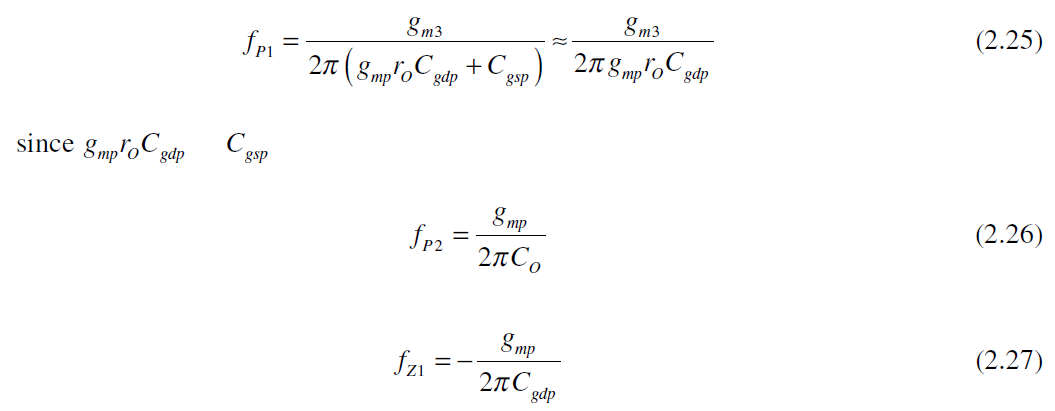

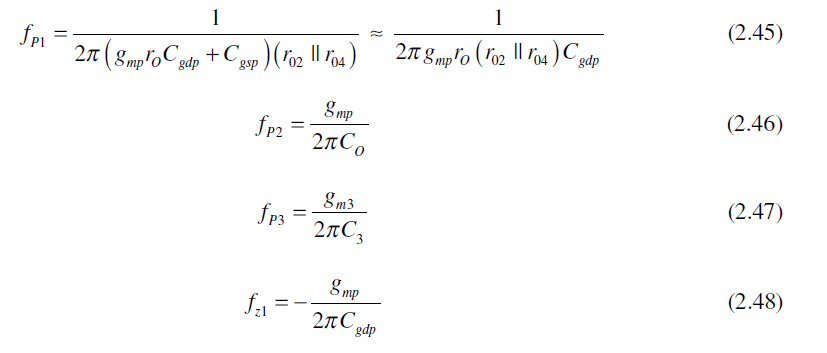

零极点位置和UGF为下式

随着负载降低, UGF和fp3不变, 但 fp2和fz1减小, 因此轻载下环路更难补偿. 功率管size决定输出电流能力, 提高Phase Margin的办法只能减小gm1,2. 但减小gm1,2会降低DC gain, 而且削弱大信号响应.

2.5.2.2 Large-signal Analysis

对于大信号, Vg上调和下调的速率一直, 都是IF/CG. 对于Vout, 上调和下调速率取决于MP电流和Io.

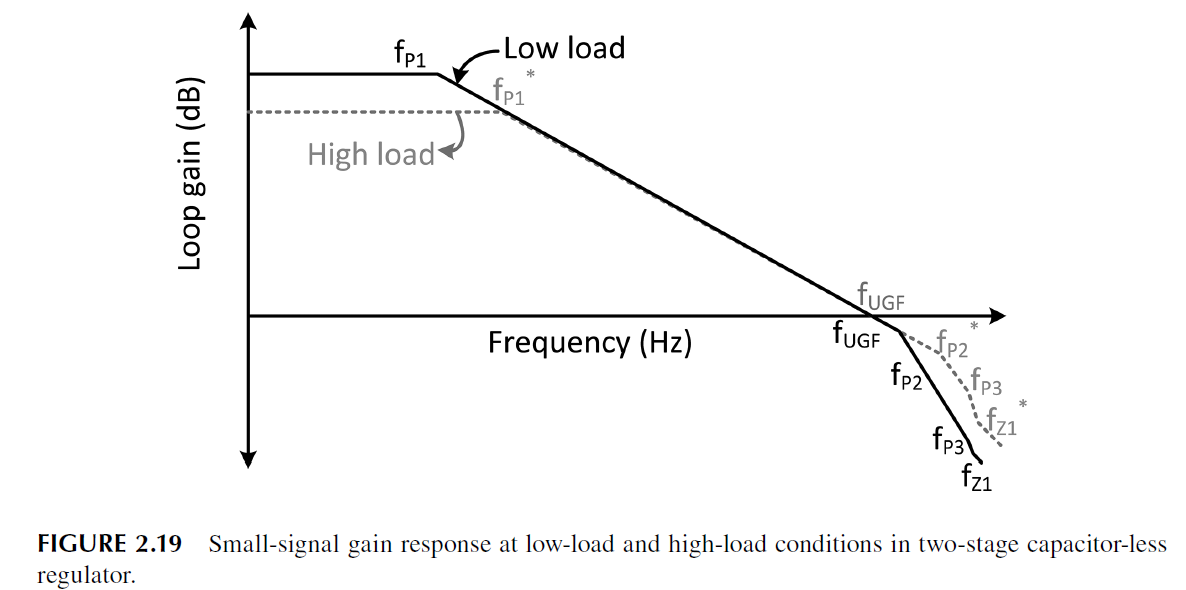

2.5.3 Three-stage Topology

为了进一步调高DC gain, 可用三级运放

其有4个极点和1个零点, 较难补偿

2.6 System-Level Considerations

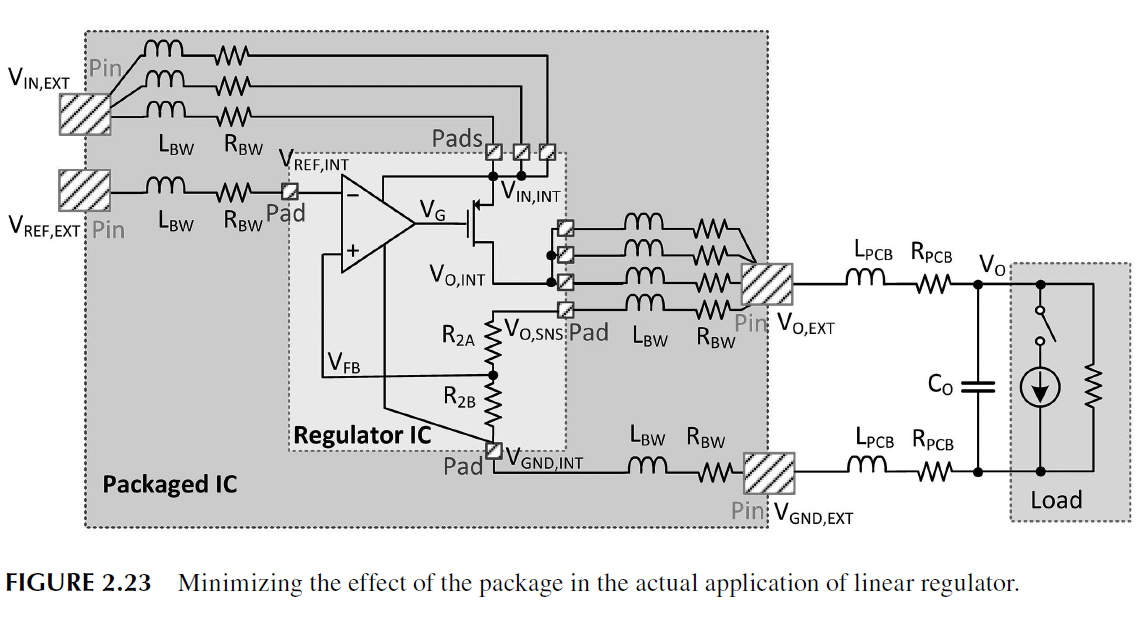

实际LDO芯片需要考虑封装pad的电感和电阻.

2.7 Key Advantages And Limitations Of Using Linear Regulators

LDO的主要优点是面积小, 器件简单. 主要缺点是效率低, 一般用在几W功率以内.