一、引言

计算机硬件系统的核心功能可分为两类:计算控制与数据存储,二者是所有数据处理、存储、传输操作的底层基础,也是软考数据系统工程师考试中计算机体系结构模块的核心考点,占比约 5%-8%,常以选择题、概念辨析题形式出现。本文将系统拆解 CPU 与存储器系统的核心结构、工作原理及联动机制,覆盖软考大纲要求的全部相关知识点,同时结合典型真题强化考点记忆。

二、计算与控制的中枢 ------CPU

CPU 是计算机的核心控制与运算单元,负责解释执行系统指令、完成算术逻辑运算、协调所有硬件模块的工作时序,其性能直接决定了数据处理的效率。

2.1 运算器:计算执行单元

运算器是 CPU 的 "实干部门",负责完成所有算术运算、逻辑运算及数据移位操作,核心组成部件包括:

算术逻辑单元(ALU):作为计算引擎,执行加减乘除等算术运算、与或非等逻辑运算,以及移位、比较等操作,是所有计算任务的最终执行载体。

累加寄存器(AC):作为临时工作台,暂存 ALU 的运算结果、待运算的操作数,减少 CPU 对内存的访问次数,提升运算效率。

数据缓冲寄存器(DR):作为数据搬运工,暂存 CPU 与内存、外设之间传输的数据,匹配不同模块的速度差异,避免数据传输冲突。

状态条件寄存器(PSW):作为计算状态报告,存储 ALU 运算过程中产生的状态标志,如进位标志、溢出标志、零标志、负标志等,为分支判断、异常处理提供依据。

CPU 运算器内部结构及数据流向示意图

(标注各核心部件的功能及数据交互路径)

2.2 控制器:指令调度单元

控制器是 CPU 的 "指挥部门",负责控制指令的读取、译码、执行全流程,协调运算器、存储器、外设的工作时序,核心组成部件包括:

程序计数器(PC):存储下一条待执行指令的内存地址,每执行一条指令自动递增,实现指令的顺序执行,支持分支、跳转指令对地址的修改。

指令寄存器(IR):暂存当前正在执行的指令,在指令执行完成前保持内容不变。

指令译码器(ID):对 IR 中的指令操作码进行翻译,生成对应操作的控制信号,发送给运算器、存储器等模块。

地址寄存器(AR):暂存 CPU 访问内存或外设的地址,直到读写操作完成。

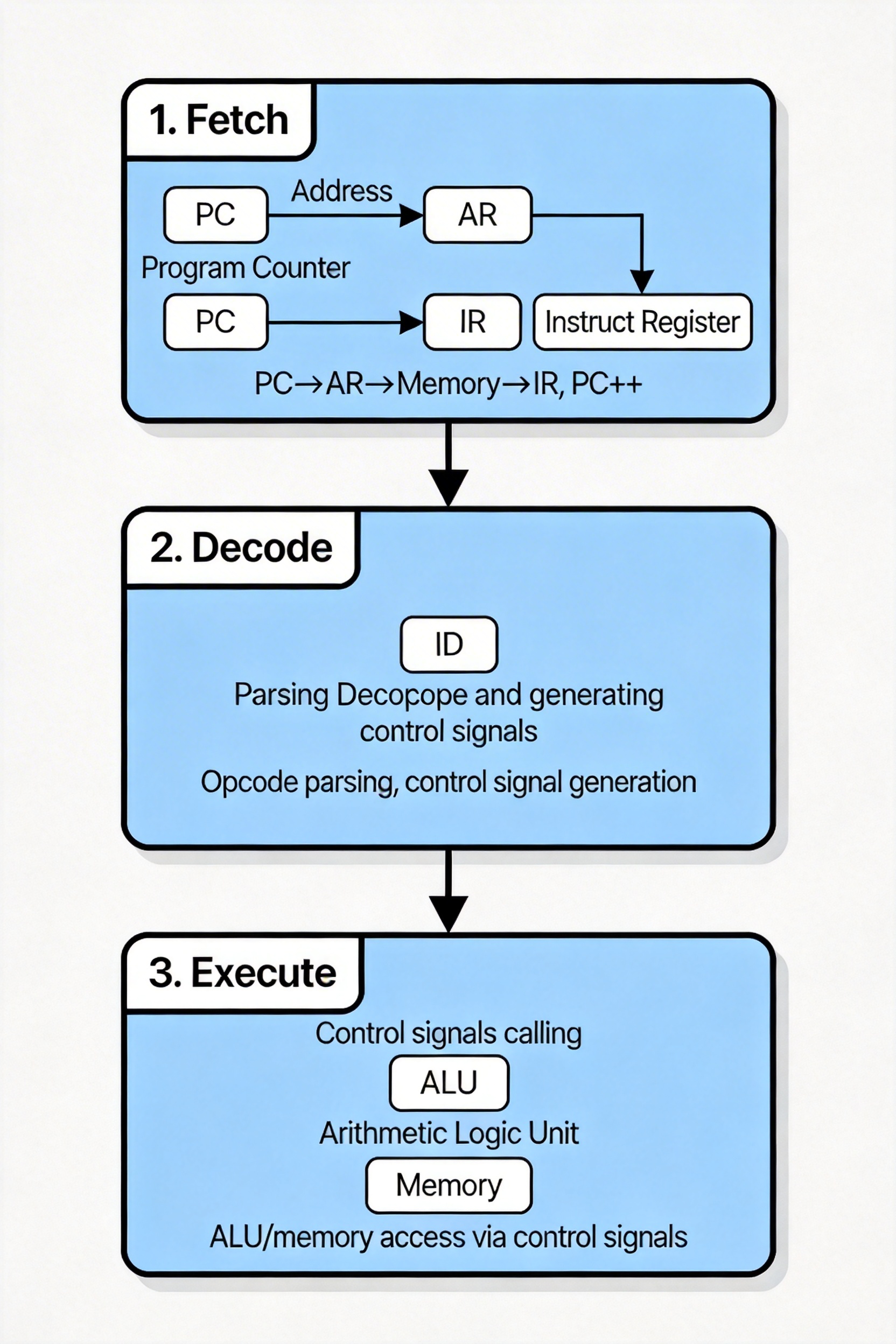

控制器的核心工作流程为三级流水线循环:取指阶段(PC 输出地址到 AR,从内存读取指令存入 IR,PC 自动递增)→ 译码阶段(ID 解析 IR 中的操作码,生成控制信号)→ 执行阶段(根据控制信号调用运算器、存储器等模块完成对应操作)。

2.3 指令与寄存器组

CPU 指令由操作码和操作数两部分组成,操作码说明指令要完成的操作类型,操作数说明参与运算的数据或数据的存储地址。

寄存器组是 CPU 内部的超高速存储单元,分为专用寄存器和通用寄存器两类:

专用寄存器包括上述运算器、控制器的核心部件,功能固定;

通用寄存器可由程序员灵活调用,暂存运算过程中的临时数据,进一步降低内存访问开销。

CPU 指令执行三级流水线流程图

(标注每个阶段涉及的核心部件及操作内容)

三、数据的家园 ------ 存储器系统

存储器系统负责存储计算机运行过程中的所有程序、数据、运算结果,采用分层架构设计,平衡速度、容量、成本三类核心指标。

3.1 存储器层次与分类

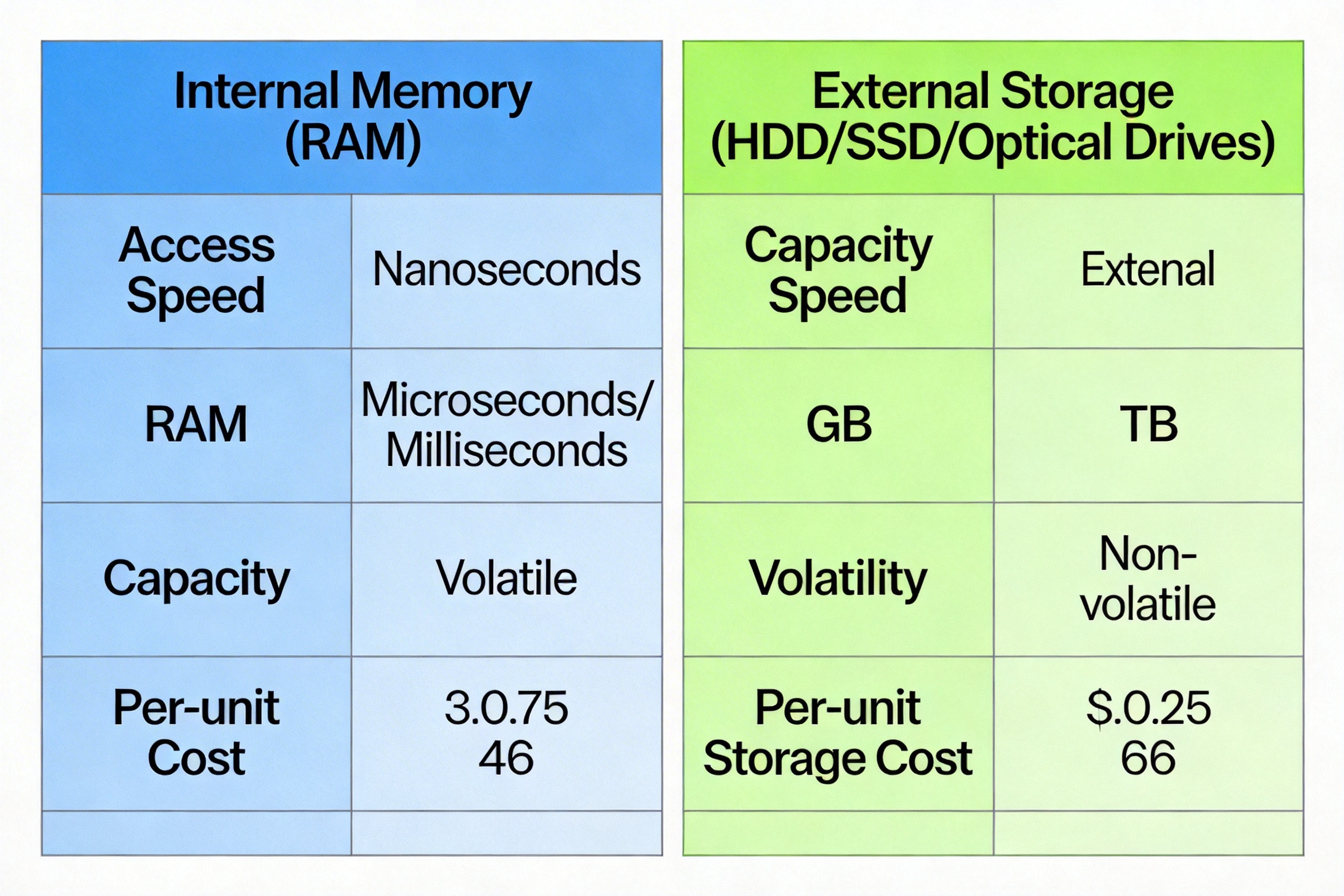

按照与 CPU 的耦合程度及功能定位,存储器可分为内部存储器和外部存储器两类:

内部存储器(内存):是 CPU 的直接工作区,由 DRAM 芯片组成,核心特点为访问速度快(纳秒级延迟)、容量相对较小(通常为 GB 级)、易失性(断电后数据全部丢失),用于临时存储当前正在运行的程序代码、待处理的数据及运算中间结果。CPU 只能直接访问内存中的数据,所有外存中的数据必须先加载到内存才能被 CPU 处理,因此内存容量直接决定了系统可同时运行的程序数量及数据处理规模,是影响系统流畅度的核心因素之一。

外部存储器(外存):是计算机的永久档案库,包括机械硬盘、固态硬盘、光盘等存储介质,核心特点为访问速度慢(微秒级到毫秒级延迟)、容量大(通常为 TB 级)、非易失性(断电后数据可长期保存),用于长期存储系统文件、用户数据、备份资料等不需要实时访问的内容。

存储器层次结构对比图

(标注内存与外存在速度、容量、易失性、成本四个维度的差异)

3.2 CPU 与存储器的联动机制

结合典型软考真题可进一步巩固二者的联动逻辑:

真题:CPU 中用于跟踪下一条待执行指令地址的寄存器是?(一般是选择题)

答案:程序计数器(PC)。

解析:PC 的核心功能是存储下一条指令的内存地址,是实现指令顺序执行的核心部件,属于软考高频考点。

CPU 读取并执行一条指令的完整流程如下:

① PC 将下一条指令的地址发送到 AR,同时发送内存读请求;

② 内存根据 AR 中的地址定位存储单元,将指令数据发送到 DR;

③ DR 将指令传输到 IR;

④ ID 对 IR 中的指令操作码进行译码,生成控制信号;

⑤ 若指令涉及运算,控制信号调度 ALU、AC 完成运算,若涉及内存读写,控制信号调度 AR、DR 完成内存操作;

⑥ PC 自动递增,准备读取下一条指令。该流程完整串联了 CPU 核心部件与内存的交互逻辑,是计算机体系结构的核心基础。

四、总结与建议

4.1 核心知识点提炼

CPU 由运算器和控制器组成,运算器负责执行具体计算,核心部件包括 ALU、AC、DR、PSW;控制器负责指令调度,核心部件包括 PC、IR、ID、AR,核心工作流程为取指 - 译码 - 执行三级循环。

存储器系统分为内存和外存,内存是 CPU 的直接访问存储区,速度快、容量小、易失;外存是长期存储介质,速度慢、容量大、非易失,所有外存数据必须加载到内存才能被 CPU 处理。

PC 的核心功能是跟踪下一条待执行指令的地址,是 CPU 与存储器联动的核心枢纽。

4.2 软考考试重点提示

本模块考点以选择题为主,高频考点包括:CPU 各寄存器的功能辨析、内存与外存的特性对比、指令执行流程的步骤排序。复习时需重点区分各寄存器的功能边界,避免混淆 PC 与 AR、AC 与 DR 的功能差异。

4.3 实践应用建议

在数据库系统性能优化场景中,CPU 运算能力、内存容量是核心瓶颈指标,理解 CPU 与存储器的工作原理,可针对性通过提升内存容量、优化数据缓存策略降低磁盘 IO 开销,提升系统整体性能。CPU 与存储器的高速运行需要与键盘、打印机等慢速外设实现高效协同,二者之间的数据传输通道、交互协议将在下篇中系统讲解,覆盖总线体系、输入输出控制方式等软考核心考点。