1.摘要:

记录一下从阅读数据手册到原理图绘制再到使用FPGA进行驱动芯片的过程。作为替代芯片,所设计的程序也完全兼容IS66WVR8M8FALL/BLL的使用。计划是使用一次突发长度为256,写入从0-255共256个字节数据到PSRAM然后读出来,通过观察读写数据是否一致来验证驱动程序是否正确。

关于spi驱动控制模块我在这里记录了:基于FPGA的APS6404L-3SQR QSPI PSRAM驱动设计(2)

2.芯片简介:

APS6404L-3SQR 是一款3V 电压域 QSPI 伪静态随机存取存储器(PSRAM),采用 SPI/QPI 双模接口设计,兼具高传输速率、低引脚数、低功耗特性,集成自管理刷新机制,无需系统主机提供 DRAM 刷新支持,专为低功耗、低成本的便携式设备应用打造。

2.1、核心基础规格

存储容量与组织 :64Mb(8M×8bits),字节寻址,地址位宽为 A [22:0];供电电压 :单电源供电,VDD 范围 2.7~3.6V;页面规格 :页大小 1024 字节,支持线性突发和 32 字节环绕突发两种突发模式;工作温度 :标准级 - 40℃~+85℃,扩展级 - 40℃~+105℃;封装形式:提供 8 引脚 SOP-8L (150,封装码 SN)、8 引脚 USON-8L 3x2mm(封装码 ZR),同时提供裸片(KGD)形式。

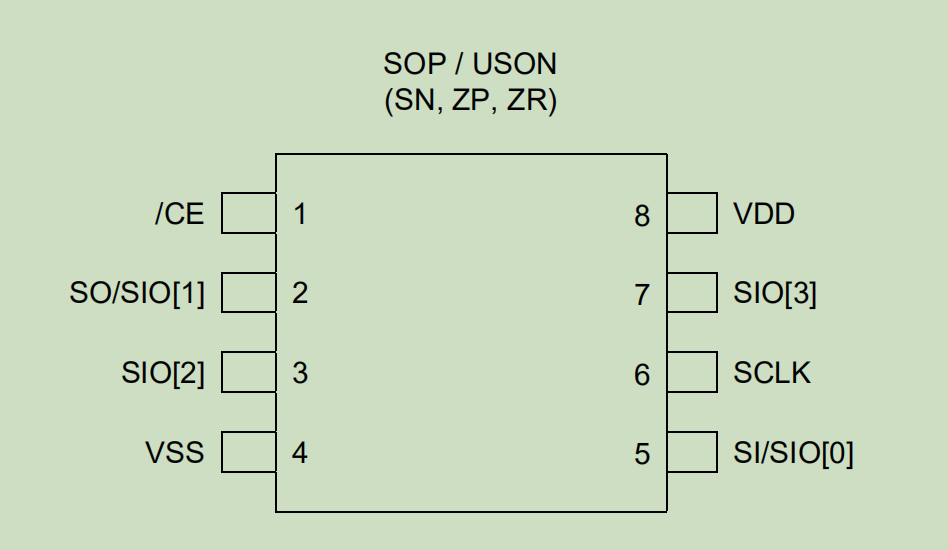

2.2、引脚说明

APS6404L-3SQR 提供标准封装和先进封装两种类型,前者为 8 引脚 SOP-8L (150) 封装,后者为 8 引脚 3×2 毫米 USON-8L 封装。如下图所示:

所有的信号介绍如下所示:

总而言之,和普通SPI区别不大,只是根据速度的不同分为SPI和QSPI。

3.命令控制:

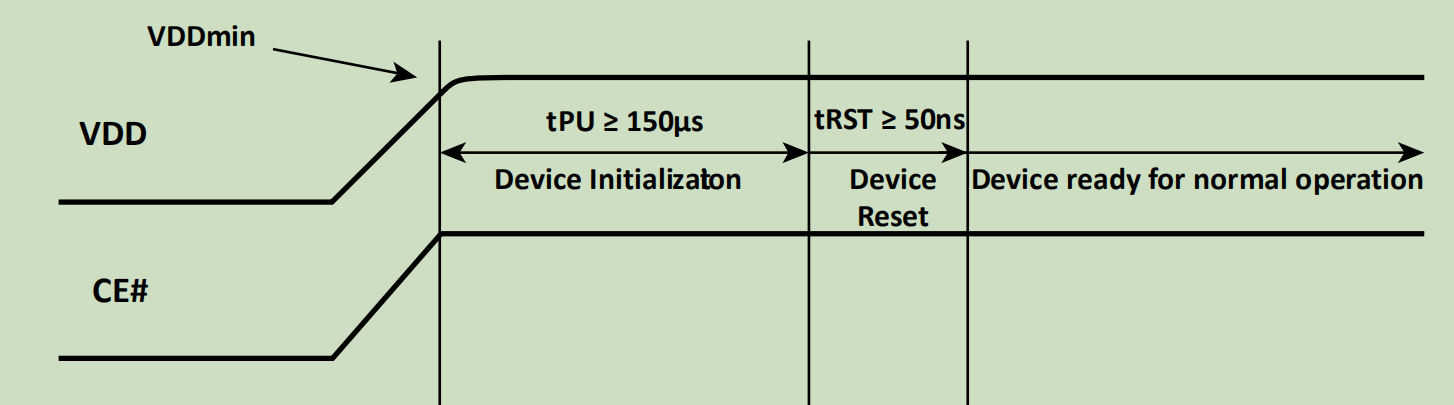

3.1、上电初始化

芯片上电后需完成电压稳定 + 初始化等待 + 软件复位 ,否则无法正常操作,FPGA 需严格按此时序输出控制信号,全程 CLK 保持低电平,CE# 保持高电平,SIO [3:0] 保持低电平。

电压稳定等待 :当 VDD 达到 2.7V 以上稳定值后,FPGA 延迟 **≥150μs**(tPU),等待芯片内部自初始化;

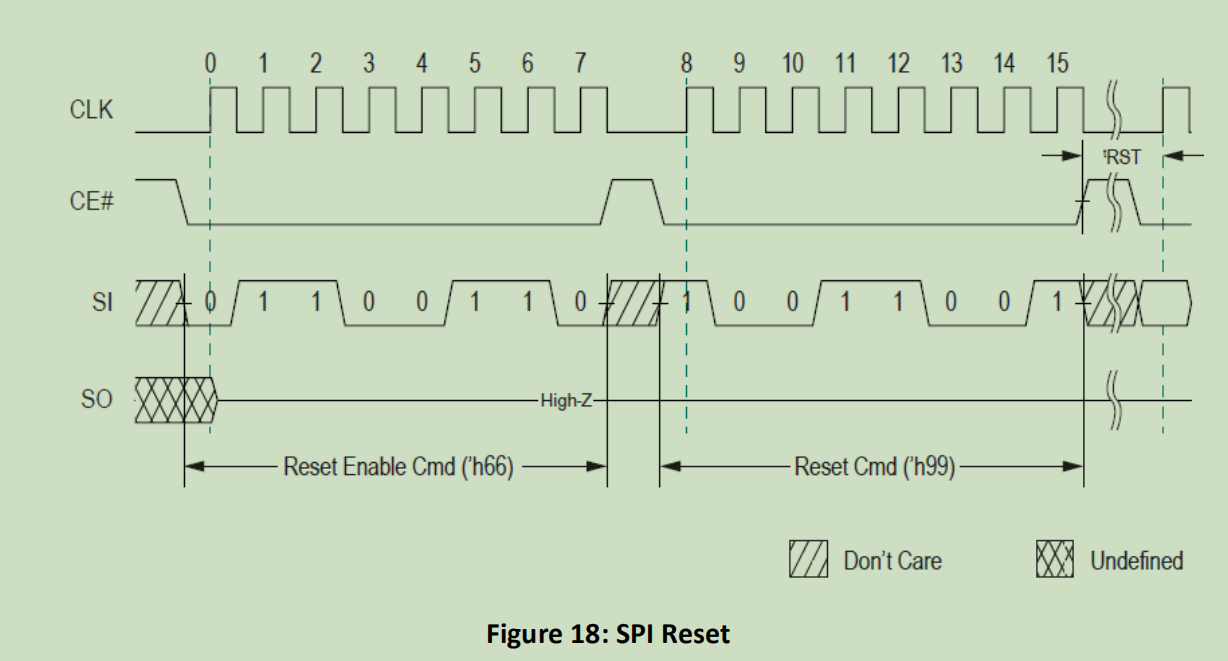

3.2、软件复位指令:

复位分为复位使能(0x66)+ 复位(0x99) 两步,需连续执行,中间不可插入其他指令,SPI/QPI 模式均支持,推荐默认用 SPI 模式执行复位(芯片上电默认 SPI 模式):

-

拉低

CE#(片选使能),FPGA 通过SI/SIO[0]串行发送复位使能指令 0x66(8bit,MSB 先送); -

继续保持

CE#低,紧接着发送复位指令 0x99(8bit); -

拉高

CE#,完成复位指令发送; -

复位后等待:复位完成后,FPGA 延迟 **≥50ns**(tRST),芯片进入 SPI 待机模式,完成初始化,可接受后续指令。

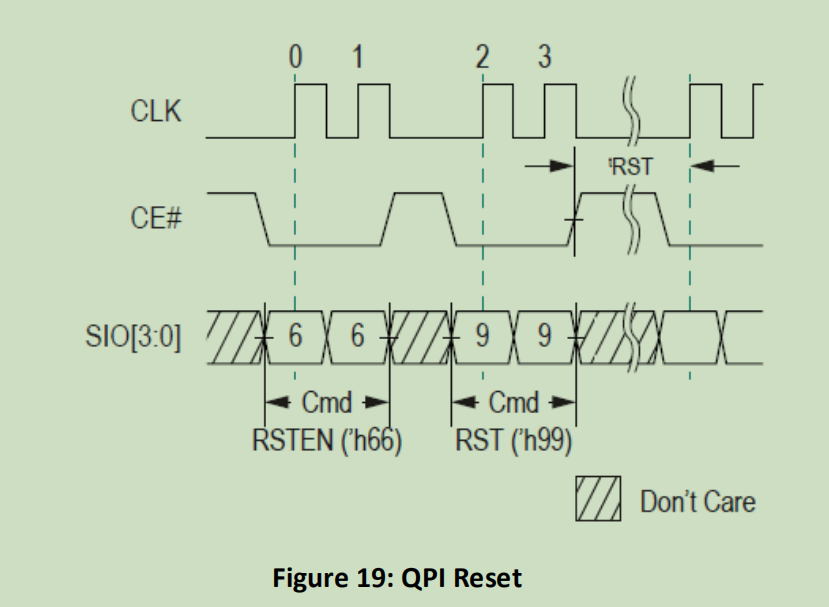

作如果是配置成QPI模式的话就要按照QPI RST的时序图进行操。

3.3、突发模式配置(可选,线性 / 32 字节环绕):

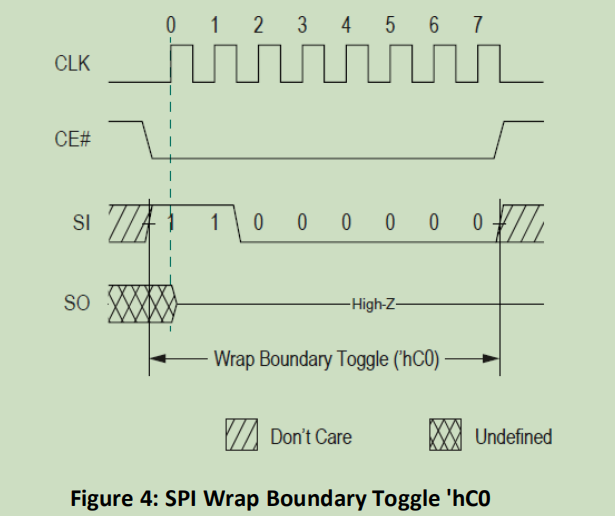

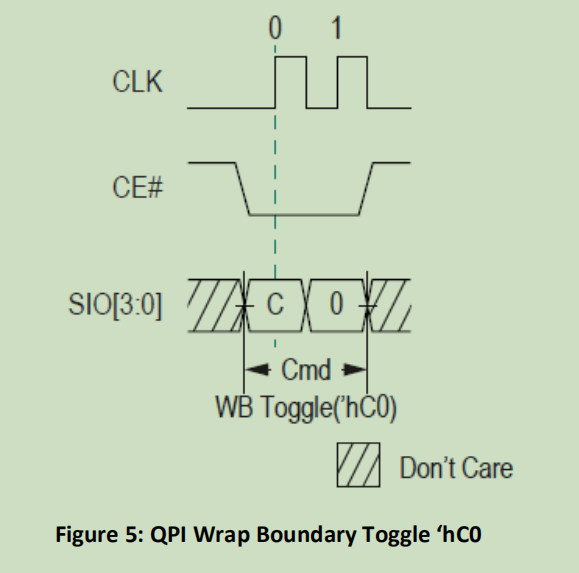

芯片默认线性突发模式 (支持跨页,最高 84MHz),若需高频操作(109/133MHz),需切换为32 字节环绕突发模式 (不支持跨页),通过环绕边界切换指令。

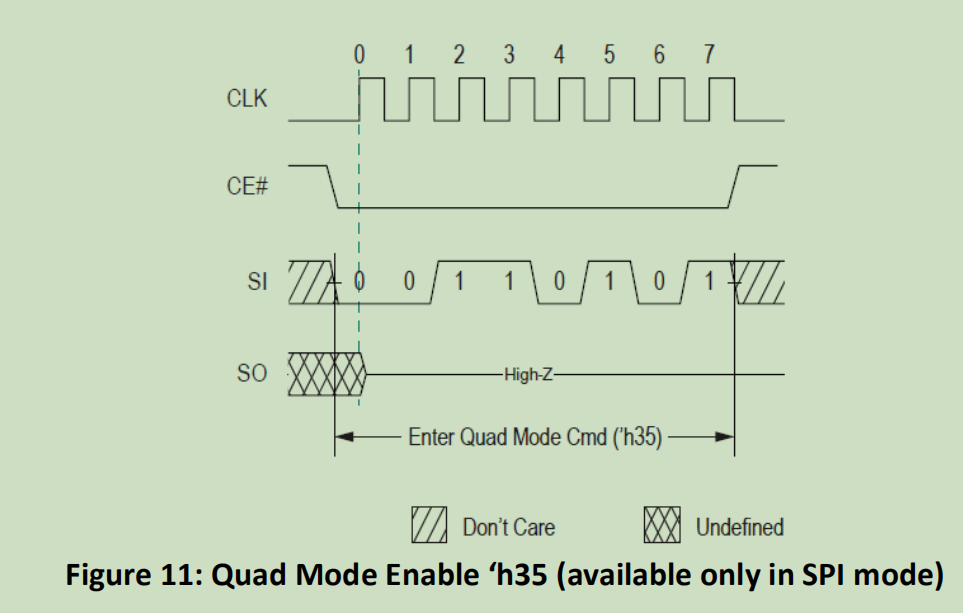

3.4、QPI模式配置:

通过此命令可以切换到QPI模式,并且只能用spi模式驱动。同样的如果想要退出QPI模式就必须要在QPI模式下驱动退出命令。具体操作如下图所示:

3.5、读数据(SPI/QPI 模式分述,支持两种突发模式):

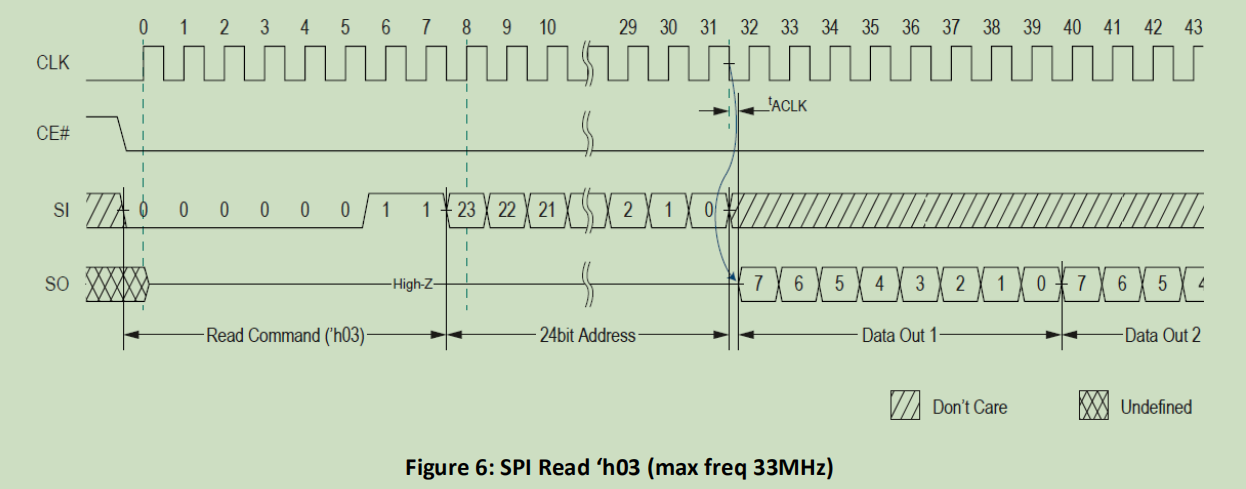

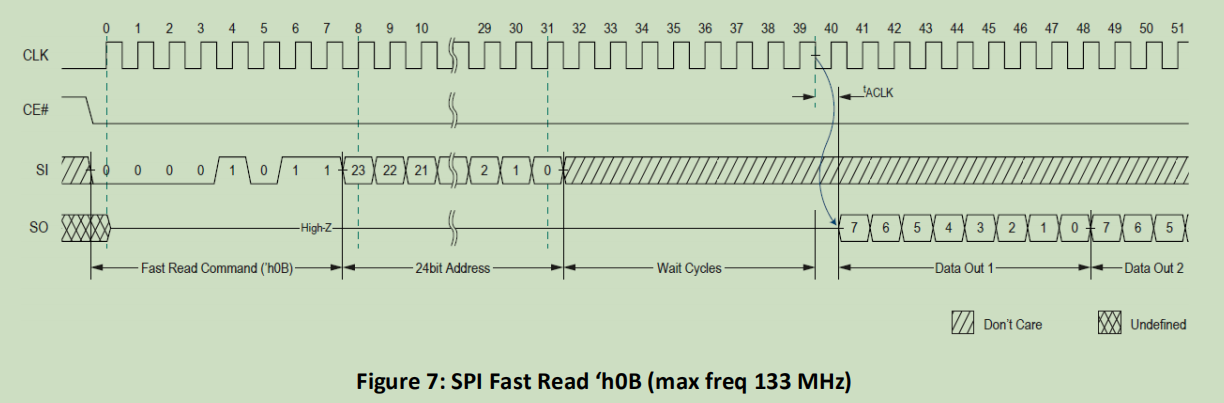

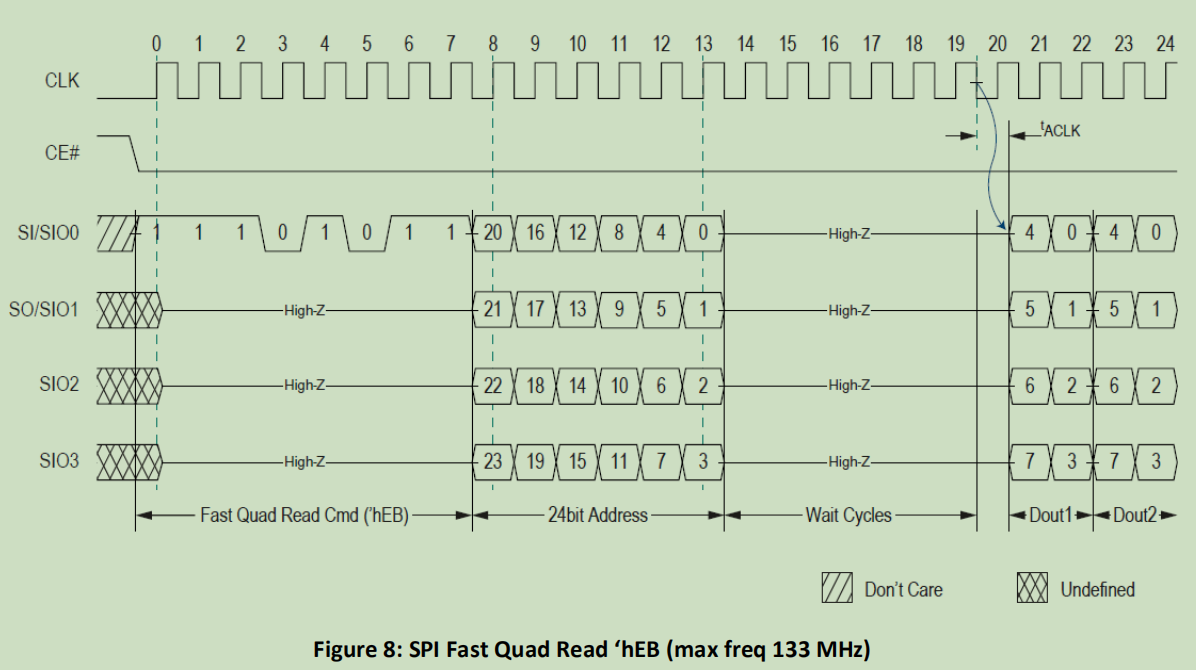

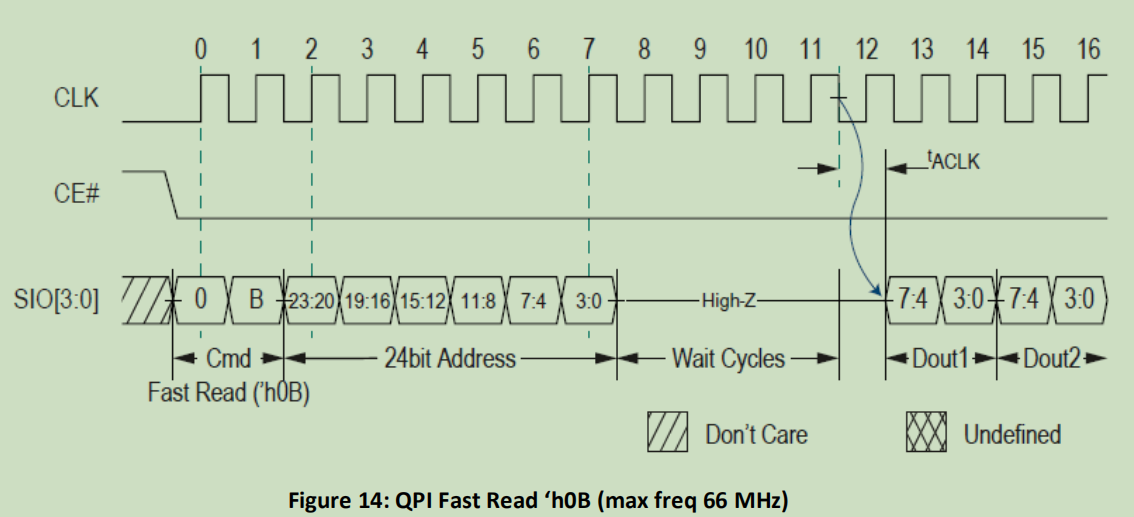

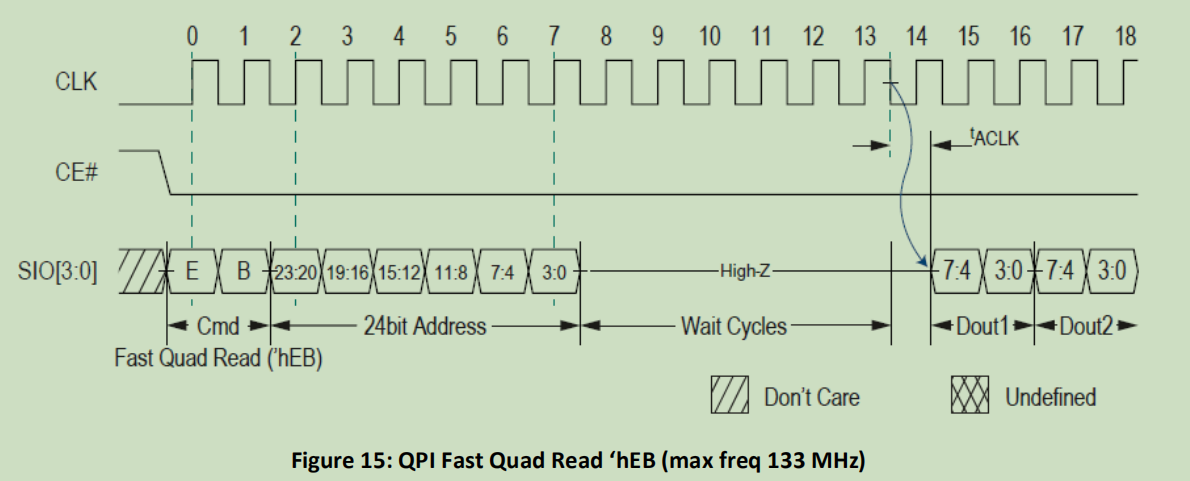

读操作需遵循 **"片选使能→发读指令→发 24bit 地址→等待周期(若有)→读取数据→片选失能"** 流程,芯片所有读数据均在CLK 下降沿后 tACLK(2~5.5ns) 输出,FPGA 需在 CLK 下降沿采样 SIO 口数据,MSB 先出。

读数据(SPI/QPI 模式分述,支持两种突发模式):

读操作需遵循 **"片选使能→发读指令→发 24bit 地址→等待周期(若有)→读取数据→片选失能"** 流程,芯片所有读数据均在CLK 下降沿后 tACLK(2~5.5ns) 输出,FPGA 需在 CLK 下降沿采样 SIO 口数据,MSB 先出。

SPI 模式读操作: (3 种指令,适配不同速率),芯片上电默认 SPI 模式,支持 3 种读指令,FPGA 按指令要求发送即可,核心区别为是否有等待周期、是否四通道传地址。

QPI 模式读操作(2 种指令,全四通道传输),QPI 模式下所有传输均为 4 路并行,FPGA 需将指令 / 地址 / 数据按 4bit 为一组并行发送 / 接收,支持 2 种读指令。

读操作通用注意点:

- 24bit 地址为字节寻址(A22~A0),对应芯片 64Mb(8M×8bit)空间,FPGA 需按实际访问地址拼接 24bit,MSB 先传;

- 等待周期内,FPGA 无需操作,芯片 SIO 口为高阻态;

- 读取数据长度由 FPGA 控制,可连续读取 N 个字节,直至拉高 CE# 终止;

- 必须通过拉高 CE# 终止读操作,否则芯片会阻塞内部刷新,导致内存故障。

3.6、写数据(SPI/QPI 模式分述,支持两种突发模式)

写操作流程为 **"片选使能→发写指令→发 24bit 地址→写入数据→片选失能",无等待周期,FPGA 需在 CLK 上升沿 ** 将数据送入芯片 SIO 口,MSB 先送,且写操作速率与突发模式 / 电压匹配(133/109/84MHz)。

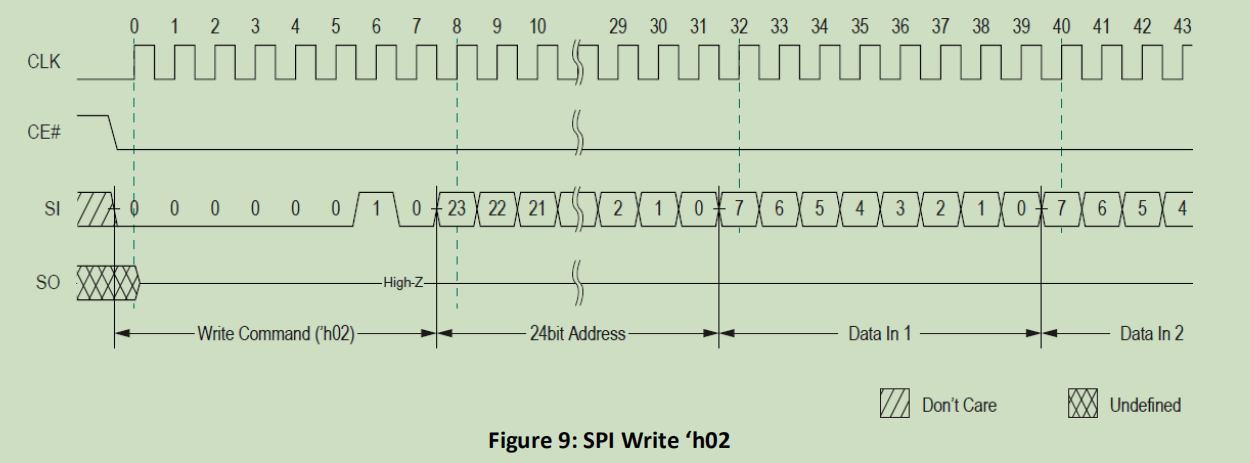

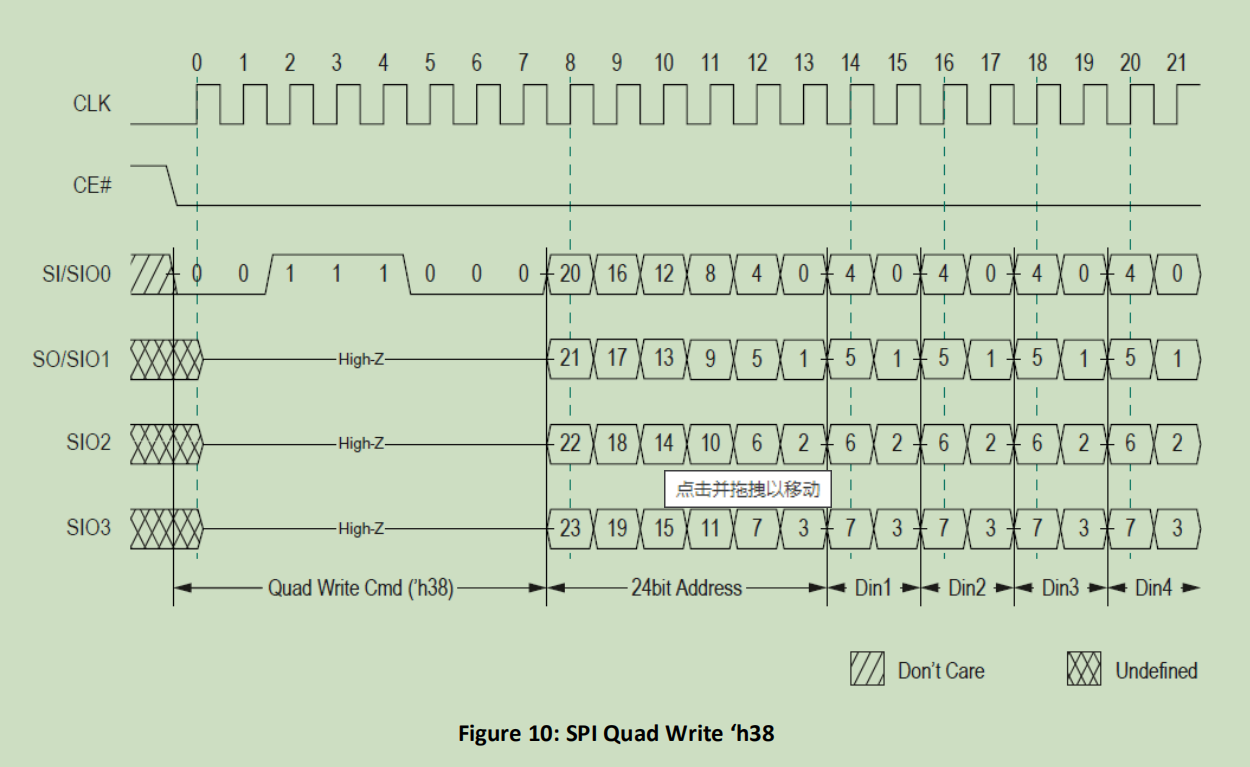

**spi写模式:**分为写指令(s 'h02 和 'h38)、写地址和写数据,标准的三模式。朴实无华好无操作可言。

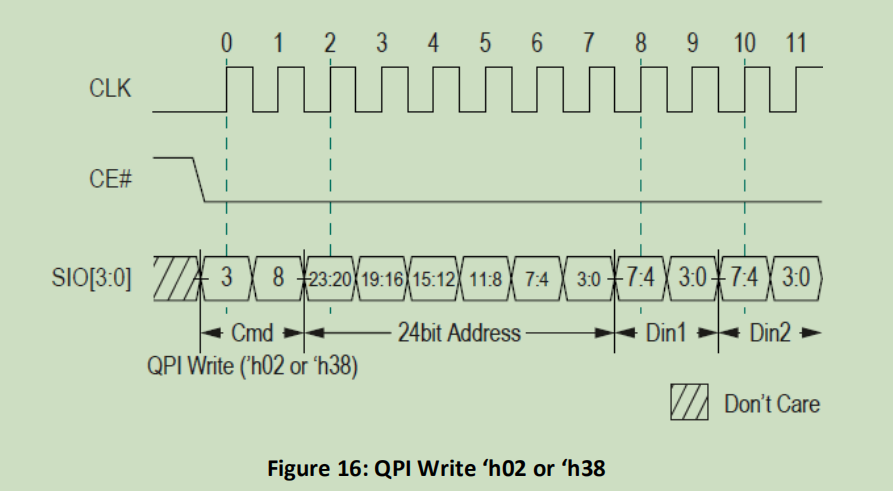

QPI 模式写操作(1 种指令,兼容 0x02/0x38)

QPI 模式下仅需通过0x02 或 0x38 指令(效果一致),全四通道传输:

- 拉低

CE#,FPGA 通过 SIO [3:0] 并行发送写指令 0x02/0x38; - 继续保持

CE#低,四通道并行发送 24bit 目标地址(A22~A0); - 四通道并行发送待写入数据,数据长度由 FPGA 控制;

- 拉高

CE#,终止写操作,芯片完成数据写入。

写操作关键注意点

- 芯片为字节写,支持连续突发写,数据按地址连续存储,线性突发模式下可单次跨页写(84MHz);

- 写操作时 FPGA 需保证数据建立 / 保持时间≥2ns,避免数据采样错误;

- 必须拉高 CE# 终止写操作,否则会导致数据写入异常和芯片内部刷新阻塞;

- 写操作完成后,可立即执行读操作验证数据,芯片无写后等待要求。

4.FPGA 驱动核心设计要点

4.1、状态机实现:

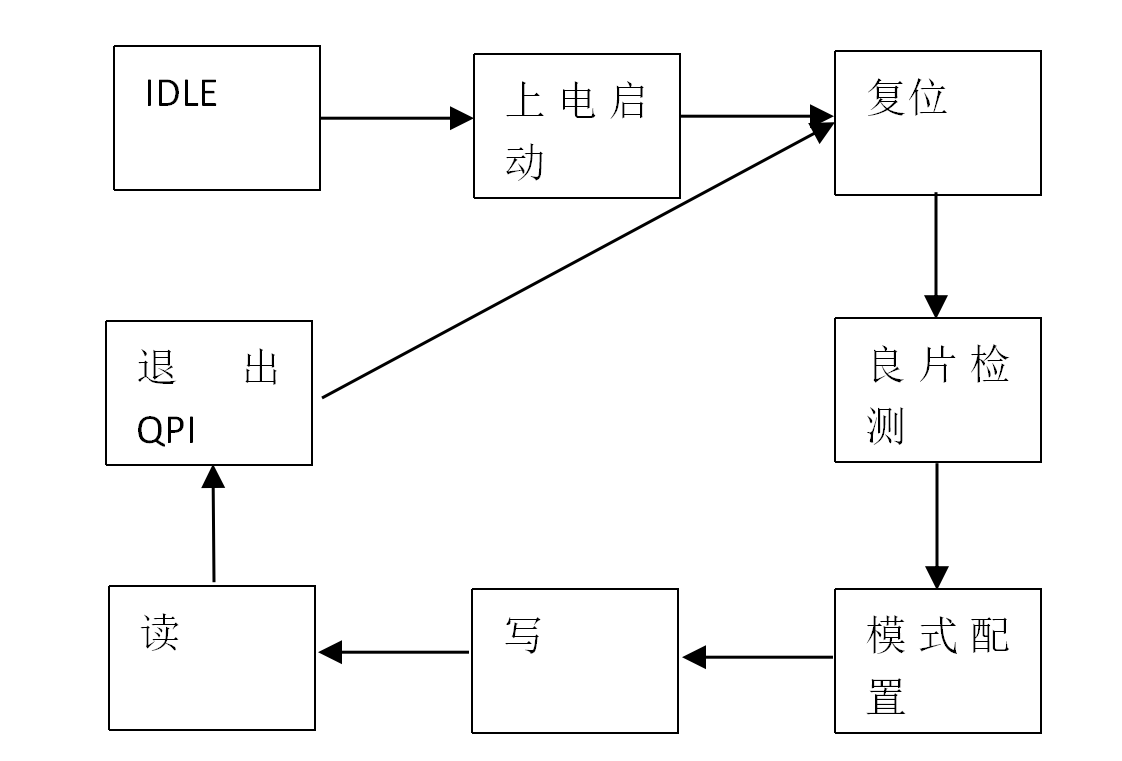

将整个流程拆分为上电→初始化→模式配置→读 / 写 / 复位→终止 多个状态,用 FPGA 有限状态机(FSM)实现状态跳转,避免指令执行混乱;

首先是上电启动 ,按照2.3的时序要求,大于150us的上电稳定外加50ns的稳定等待。之后跳转到复位状态 ,复位操作需要连续进行cmd66和cmd99,连续操作之后跳转到良片检测。 接收到8'h5D后开始进行模式配置, 既然选择了四线模式的芯片没理由放着不用用spi模式吧?配置完之后就到了读写状态, 读完数据之后我是跳转到退出QPI模式 在进行一次**复位操作,**我是为了应对同一个地址进行多次多写的情况,状态机可加状态也可以减,根据需要来定。

4.2、模块接口设计

芯片6线接口具体如表2.2所示:

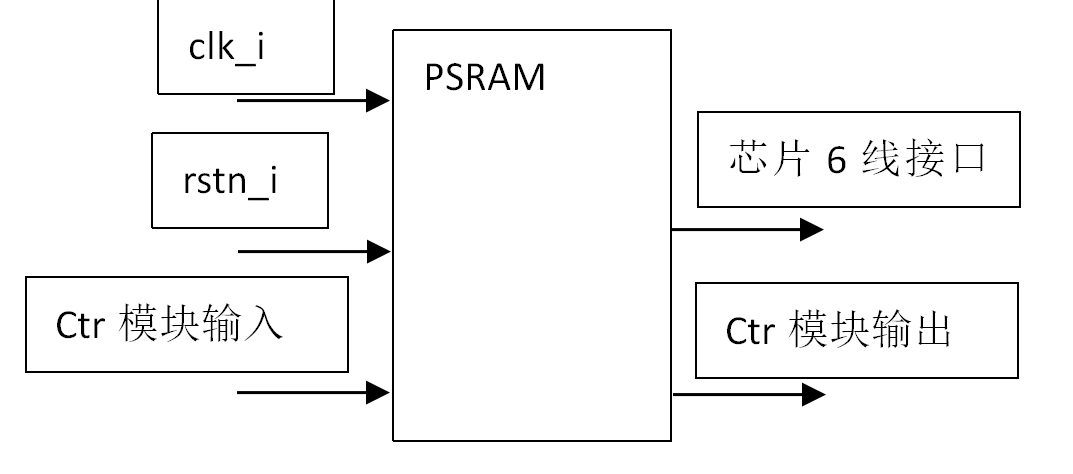

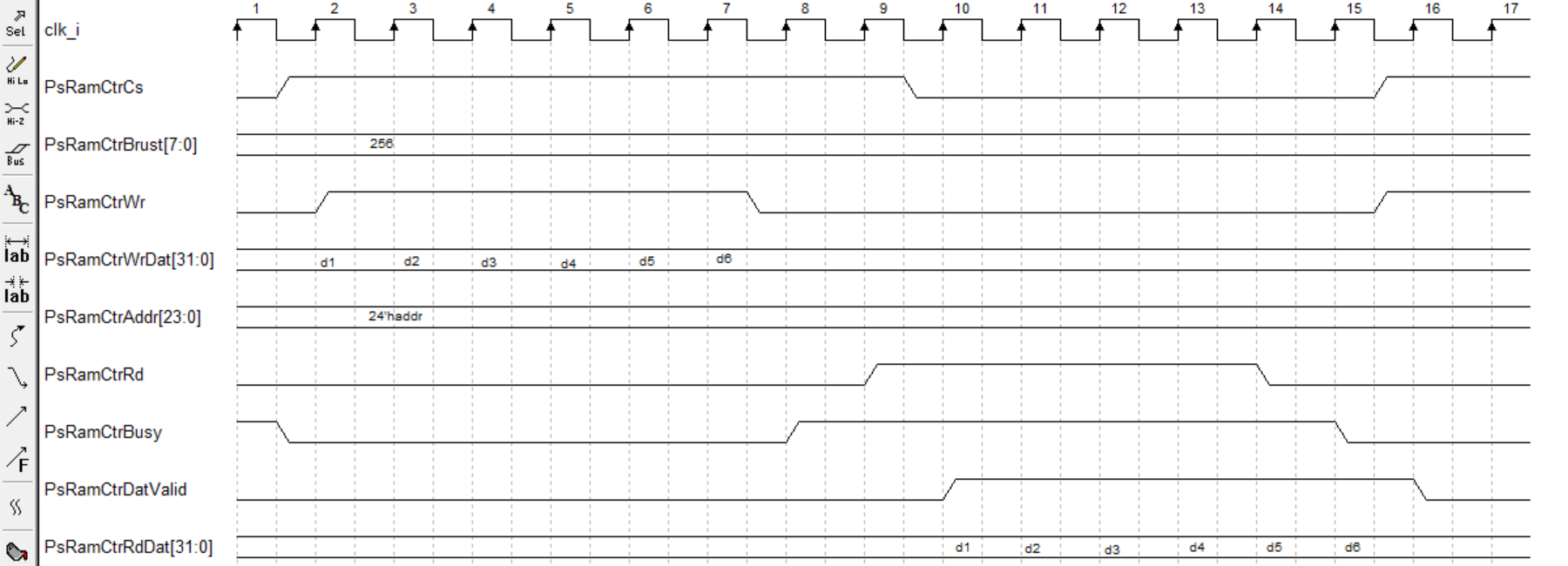

Ctr模块接口的时序图如下所示,和AXIS或者Avalon协议差不多。

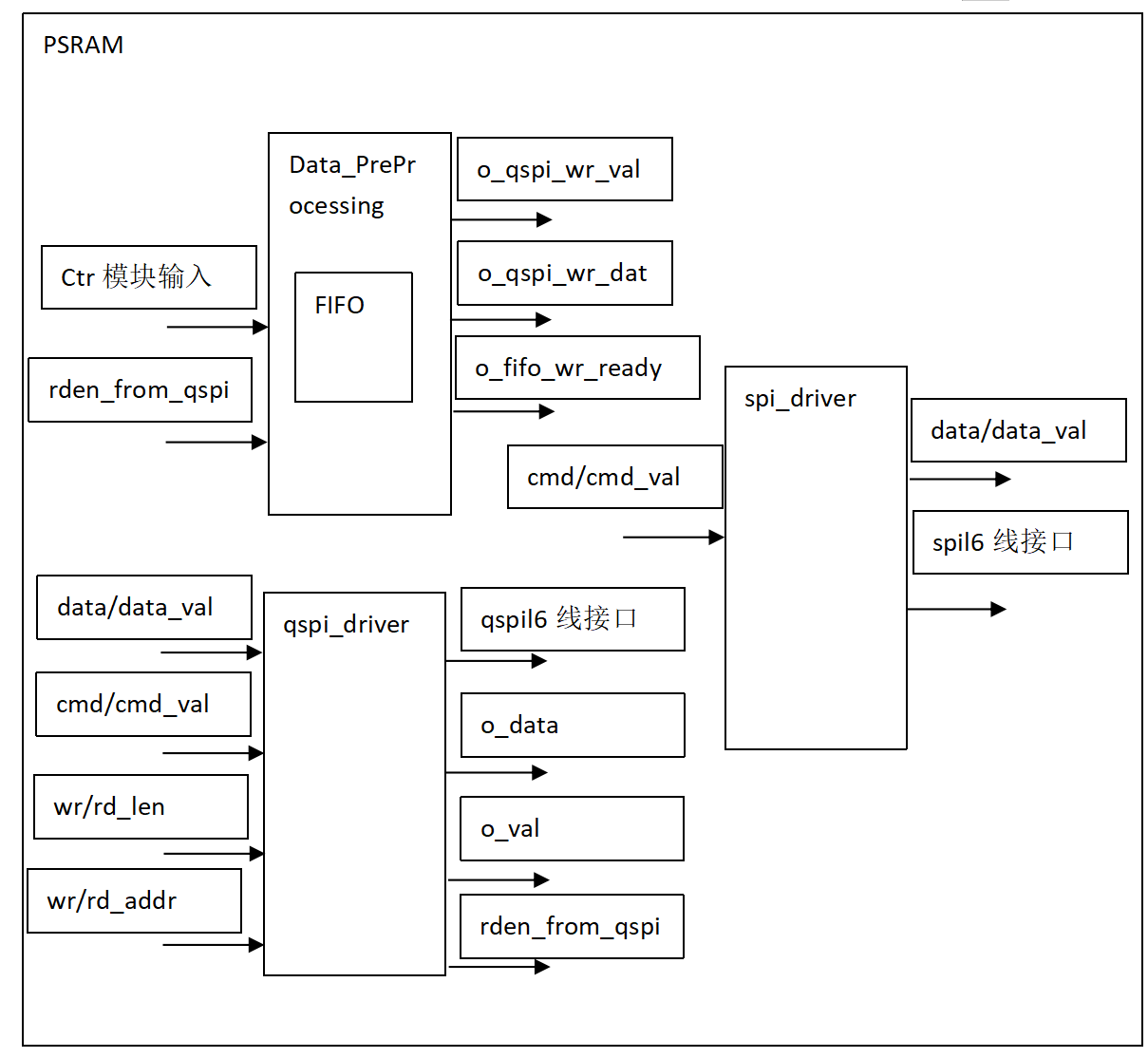

整体的模块框图如下所示:

通过PSRAM驱动模块负责分配不同命令给SPI模块和QSPI模块,QSPI模块负责处理读写数据,包括从FIFO中拿数据和输出数据到FIFO中给Ctr模块读出去。

5.总结

这篇主要介绍一下这款芯片和对手册以及设计过程中的一些总结,然后下一篇在记录一下其他模块的设计要点。