目录

[1. 系统连接框图](#1. 系统连接框图)

1. 系统连接框图

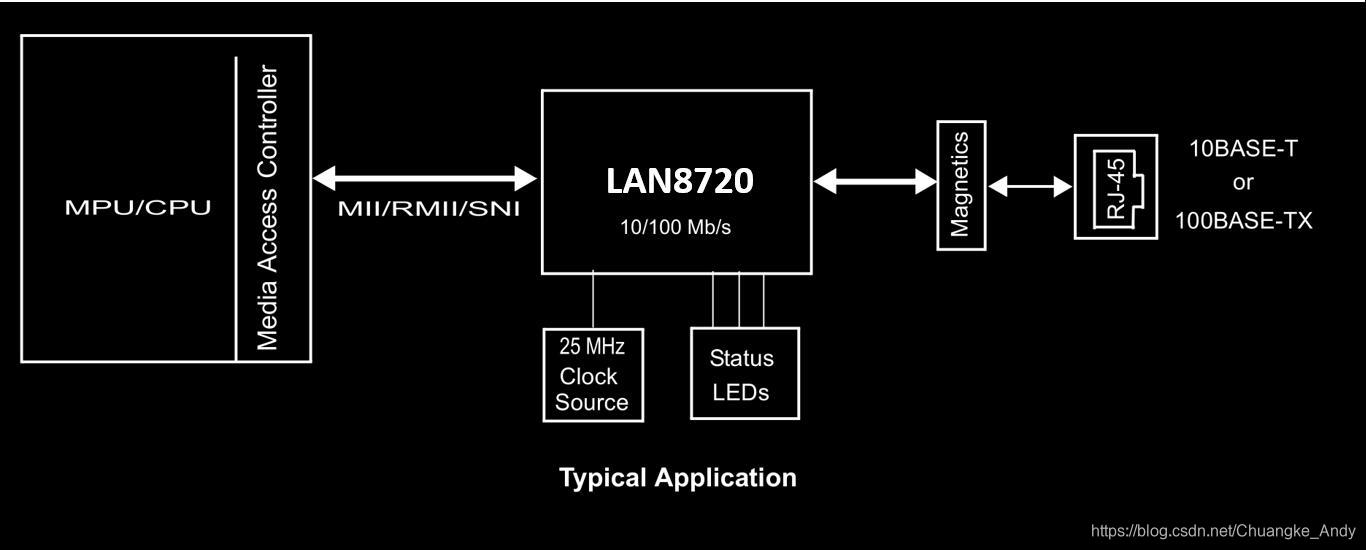

使用的是STM32F407 (MAC层)+ LAN8720以太网芯片(物理层) + RJ45插头的系统结构。

2.接口管理

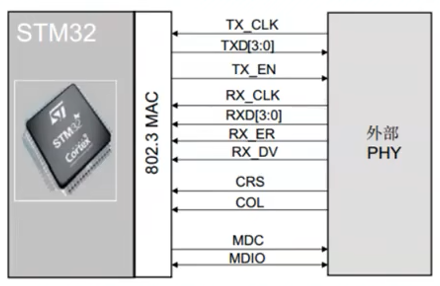

MII接口:

10/100M的MAC子层和PHY间的互联。(速率为10Mbit/s时要提供的为2.5MHZ,速率为100Mbit/s时为25MHZ)

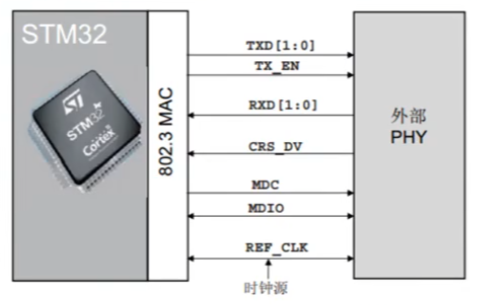

RMII接口:

相比于MII,降低了控制器以太网外设与外部PHY间的引脚数。仅为7个。(REF_CLK必须是50MHZ,但其实只需要提供25MHZ就行了,因为STM32内部存在PLL倍频)

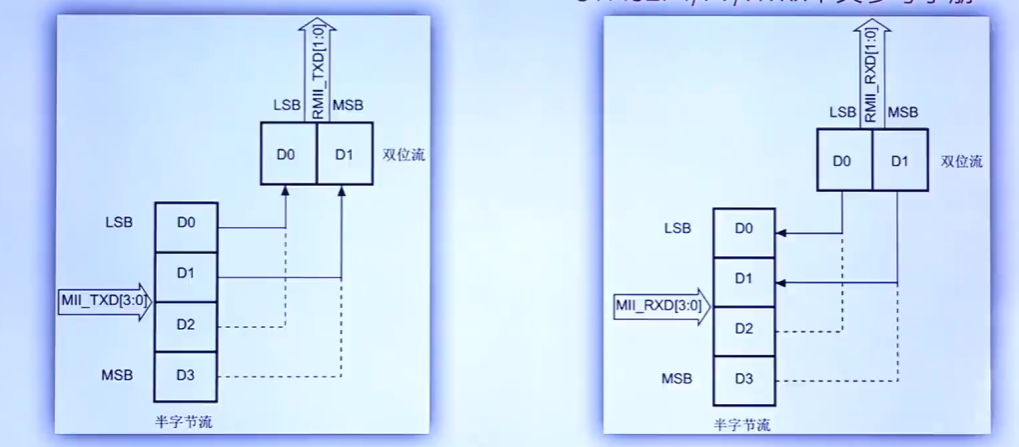

介质接口MII、RMII收发位宽:

MII接口一周期发送4bit数据、RMII一个周期发送2bit数据;

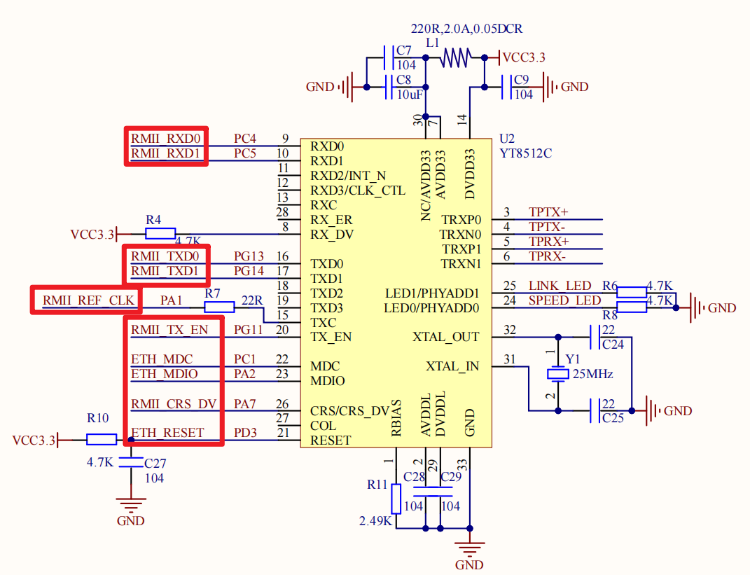

接口连接原理图

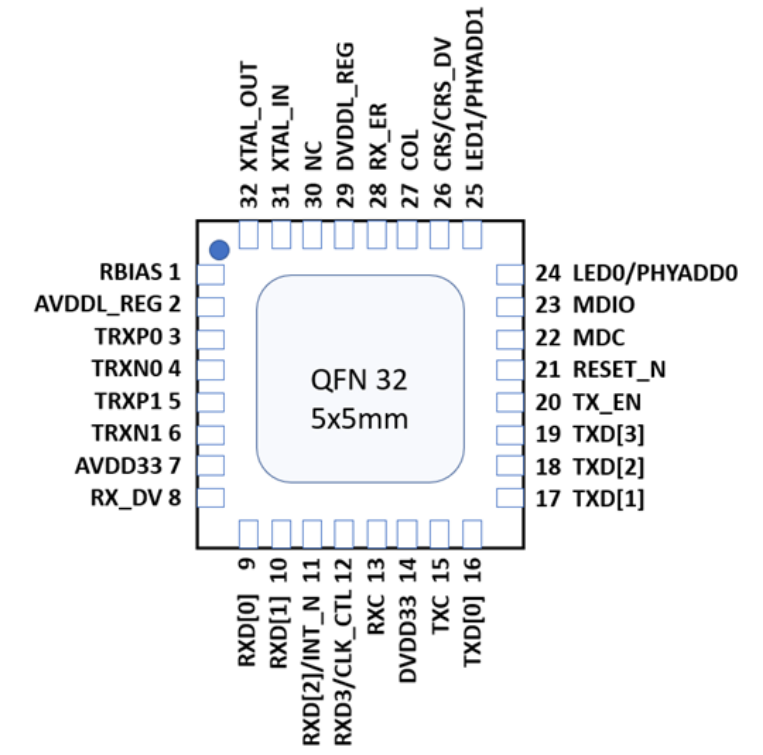

这里我使用的是YT8512C。通讯接口是RMII与MAC层进行连接。

YT8512C原理图:

3.MAC层

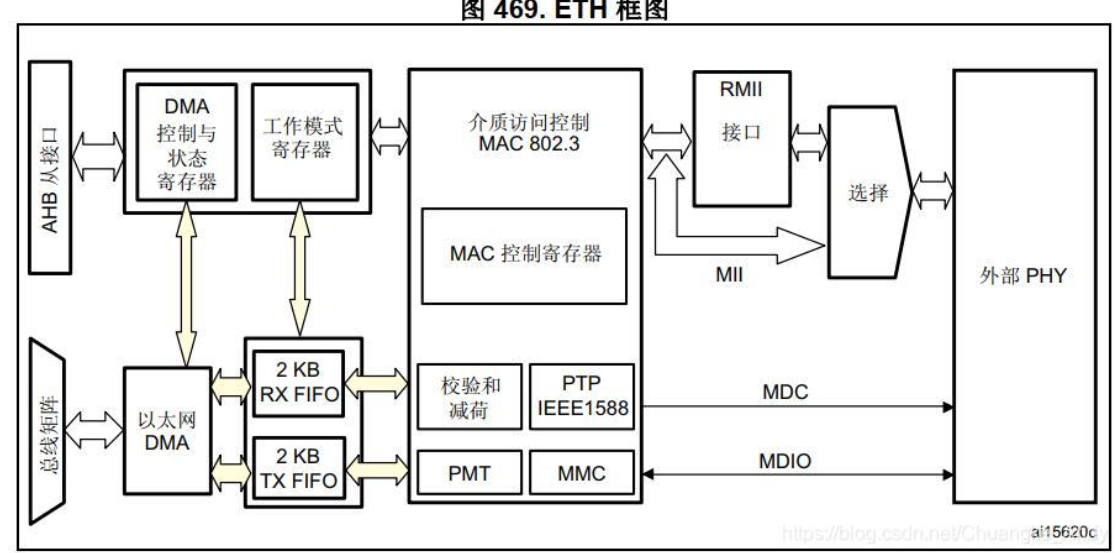

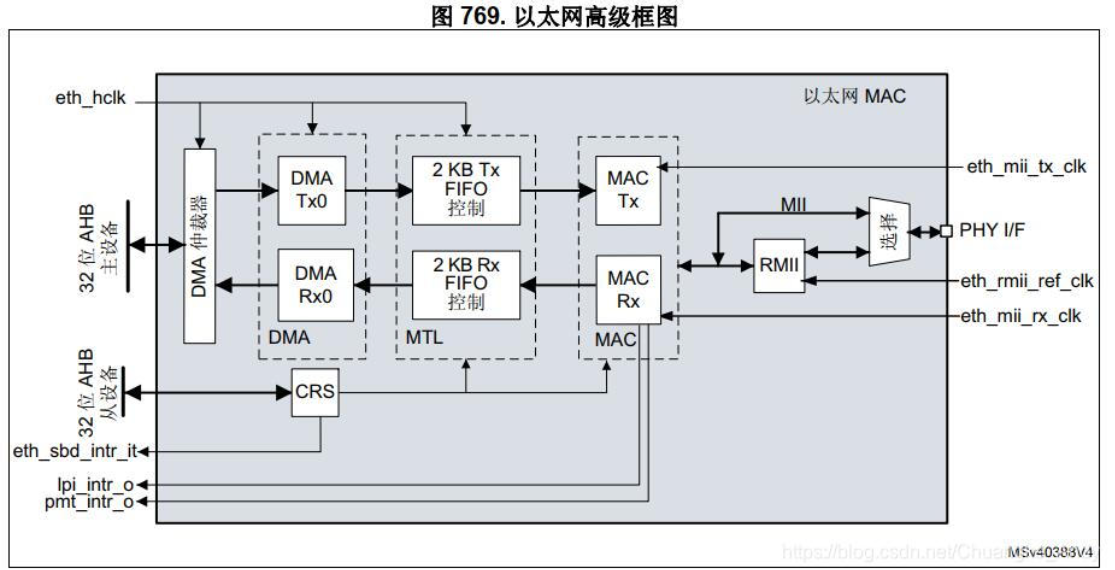

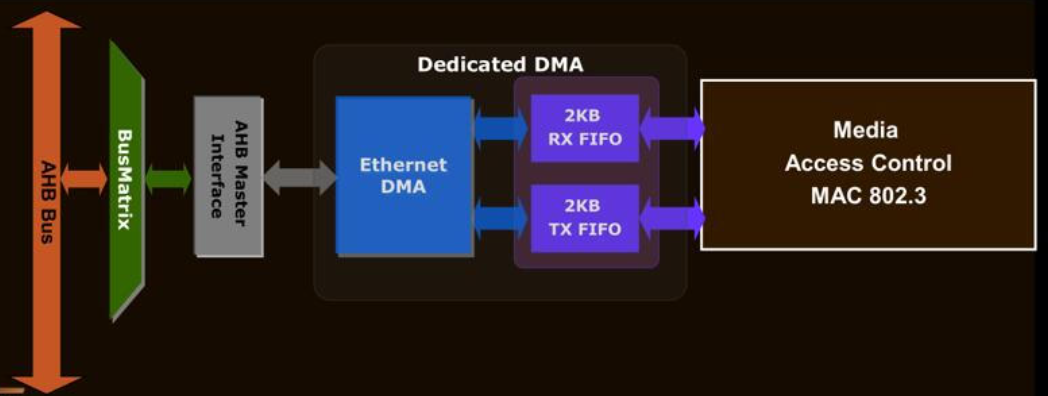

以太网外设包括带专用 DMA 控制器的 MAC 802.3(介质访问控制)。它支持介质独立接口(MII) 和简化介质独立接口 (RMII),并通过一个选择位在两个接口间进行切换。

以太网外设由 4 个主要功能模块组成:

- 控制和状态寄存器模块 (CSR),用于控制通过 AHB 32 位从接口进行的寄存器访问;

- 直接存储器访问接口 (DMA),此为逻辑 DMA 模块,具有 1 条用于接收的物理通道和 1 条用于发送的物理通道。该模块用于控制通过 AMBA AHB 32 位主接口在 MAC 和系统存储器之间进行的数据传输;

- 介质访问控制模块 (MAC),负责实现以太网协议;

- MAC 事务层 (MTL),负责控制应用和 MAC 之间的数据流;

此外,还增添了协议适配模块以支持 RMII PHY 介质独立接口:

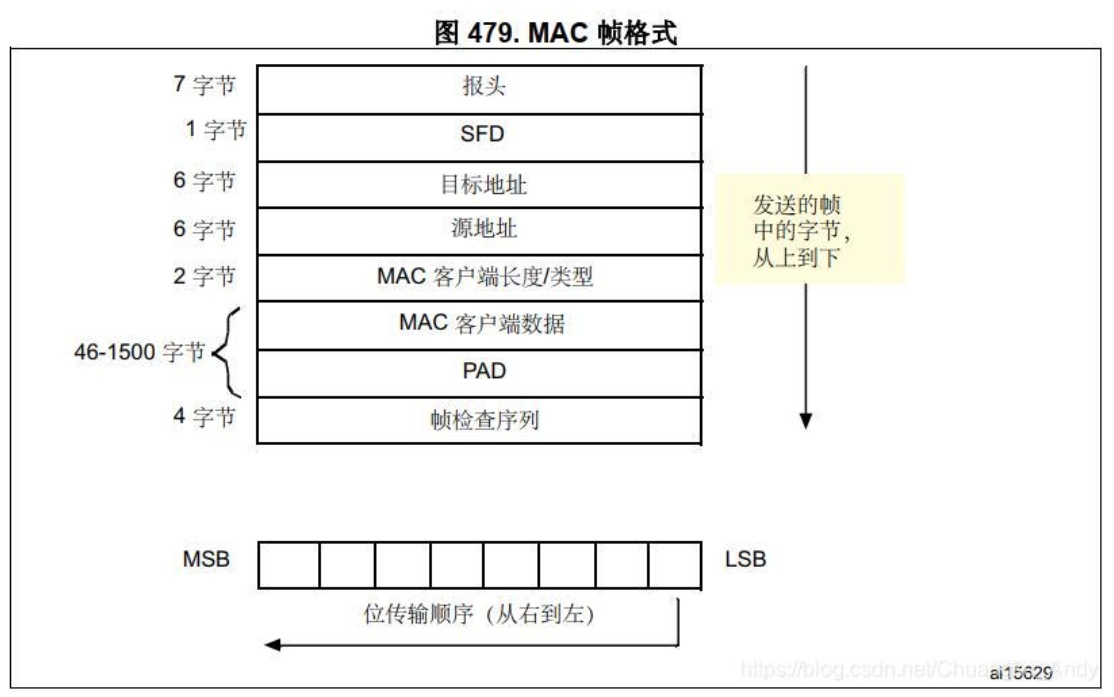

- MAC帧格式

- 帧发送过程

从系统存储器读取的以太网帧由DMA推入FIFO,然后将帧弹出并传输到MAC内核。帧传输结束时,从MAC内核获取发送状态并传回DMA。

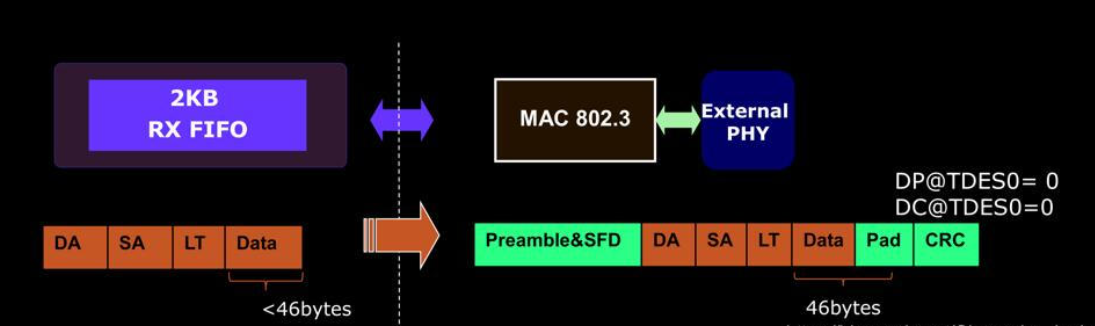

- 帧填充和CRC计算

当从应用程序接收到的字节数少于46时,会向发送帧附加零,使数据长度正好为46字节,以满足IEEE 802.3的最小数据字段要求。

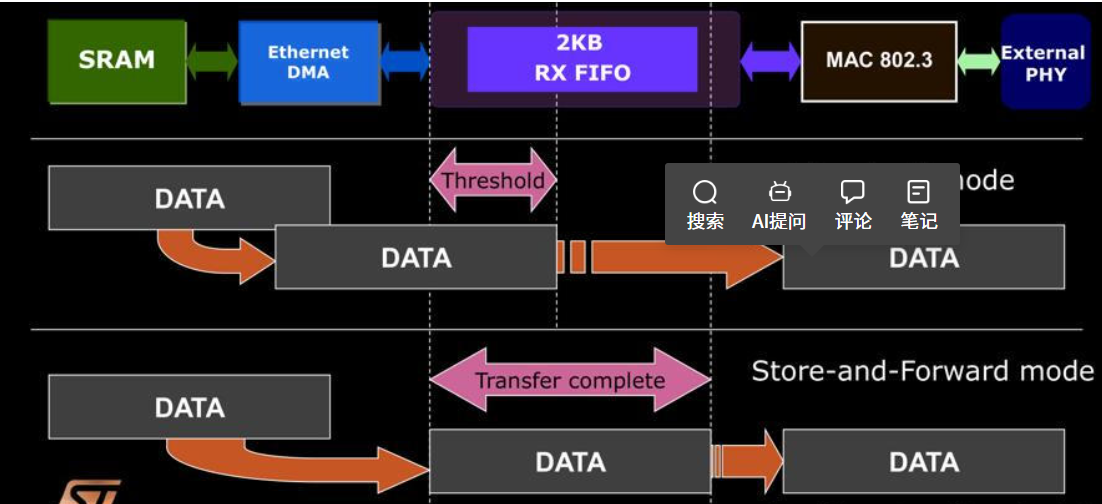

3.1、FIFO

FIFO向MAC内核弹出数据有两种模式:

- **阈值模式:**只要FIFO中的字节数超过配置的阈值,数据就准备好弹出并转发到MAC内核

- **存储转发模式:**仅在FIFO中存储完整的帧后,才会想MAC内核弹出帧

3.2、DMA

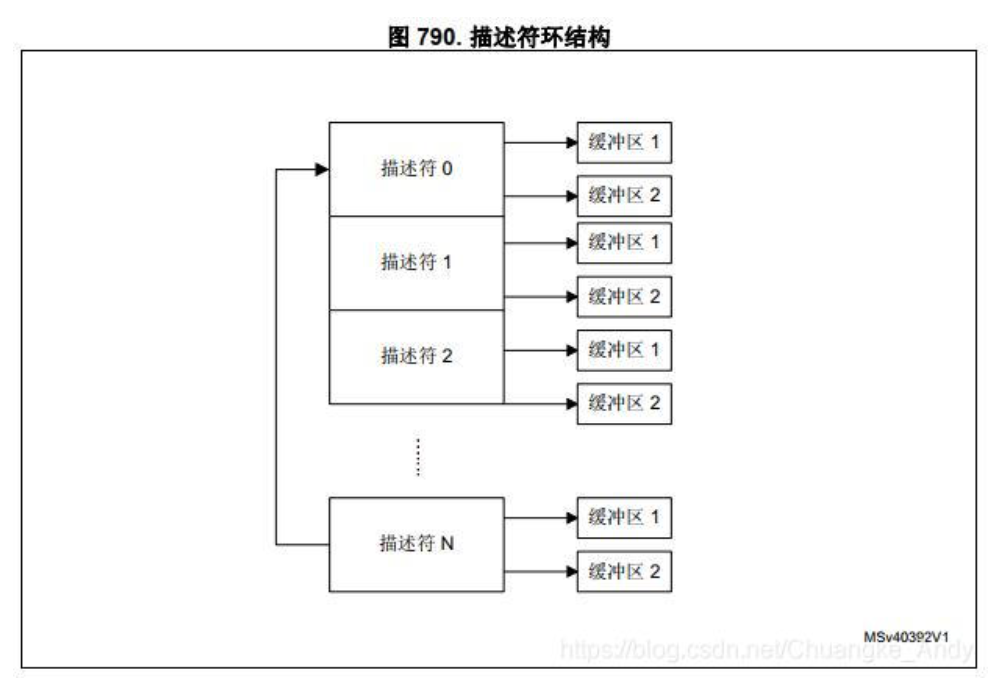

DMA基于描述符的链表传输数据。应用程序在系统存储器(SRAM)中创建描述符。支持正常描述符和上下文描述符两种。

以太网模块中的接收/发送FIFO和内存之间的以太网数据包传输时以太网DMA使用DMA描述符完成的。

一共有两个描述符列表:一个用于接收、一个用于发送,两个列表的基地址分别写入DMACRDLAR寄存器和DMACTDLAR寄存器中。

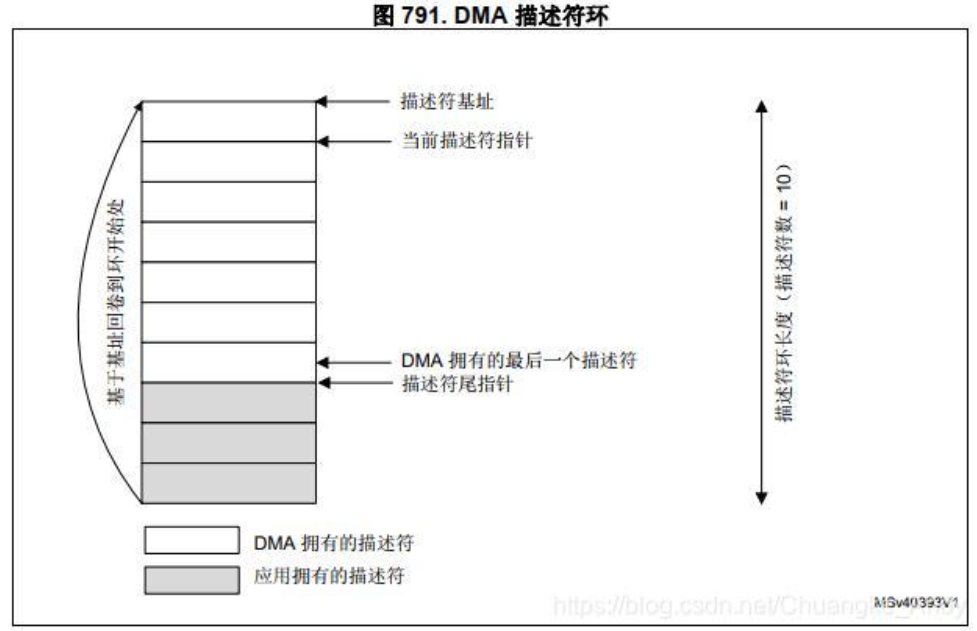

- DMA描述符环形结构

- **DMA描述符环链接结构:**到达环结束处时,DMA会自动基于基址进行回卷

- DMA描述符格式:

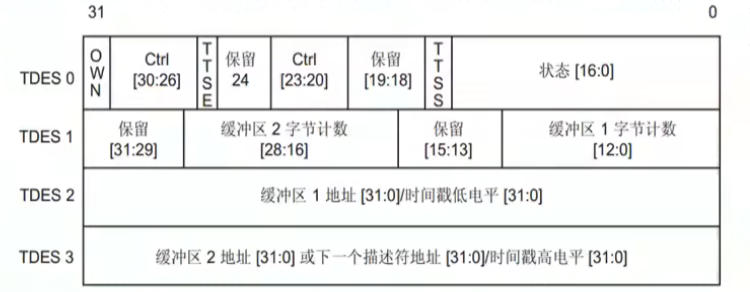

常规发送描述符:

增强发送描述符:

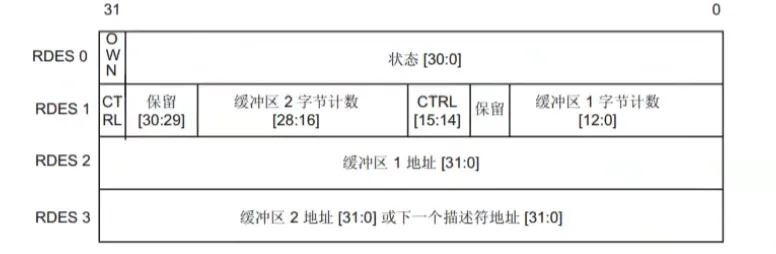

常规接收描述符:

4、PHY层

YT8512C支持RMII接口与以太网MAC通讯,内置10-BASE-T/100BASE-TX全双工传输模块,支持10Mbps和100Mbps。可以通过自协商的方式与目的主机最佳的连接方式(速度和双工模式)。支持HP Auto-MDIX自动翻转功能,无需更换网线即可将连接更改为直连或交叉连接。

YT8512C的配置及使用详见其数据手册,下面简单介绍几种常用的功能设置:

- **中断管理:**当中断事件发生且相应事件的中断位使能,YT8512C就会在nINT(11脚)产生一个低电平有效的中断信号。提供主中断和复用中断两种模式;

- **PHY地址设置:**MAC层通过SMI总线对PHY进行读写操作,YT8512C通过设置LED0/PHYADD0引脚或者LED1/PHYADD1来设置PHY地址,默认情况下为0;

- **nINT/REFCLKO配置:**nINTSEL(2脚)用于设置nINT/REFCLKO(14脚)引脚的功能;

- **内部寄存器:**所有以太网的PHY芯片都遵循IEEE 802.3标准,标准通用寄存器0~15;(所有PHY芯片都一样)

16~31扩展通用寄存器,不同的PHY芯片它们的功能都高度相似;

>= 32厂商自定义寄存器,每个芯片不一样,这是按厂商规定来的;