导语: 在集成电路设计领域,前端设计(RTL设计)的书籍汗牛充栋,但真正系统讲解后端物理设计的中文教材却凤毛麟角。今天推荐的这本书,是国内第一本全面、完整介绍数字集成电路后端布局布线设计技术的专门教材------《数字集成电路物理设计》。无论你是正在求职的应届生,还是寻求技术突破的在职工程师,这本书都值得放在案头反复研读。

一、为什么物理设计需要一本"中文指南"?

集成电路设计是一个从抽象到具体的漫长旅程。从系统架构到RTL代码,从前端仿真到逻辑综合,当设计流程进入物理实现阶段(Physical Implementation),工程师面对的是最真实的工艺约束、最复杂的时序挑战和最严峻的信号完整性问题。

长期以来,国内集成电路教育存在"重前端、轻后端"的倾向。市面上关于Verilog、SystemVerilog、UVM等前端技术的书籍层出不穷,但关于布局(Placement)、布线(Routing)、时钟树综合(CTS)、静态时序分析(STA)等后端核心技术的系统性中文教材却极为稀缺。这导致许多工程师在学习物理设计时,只能依赖零散的英文论文、EDA工具手册或口耳相传的"祖传脚本",知识体系支离破碎。

2008年,科学出版社推出的这本《数字集成电路物理设计》,第一次系统性地将数字后端设计的全流程以中文教材的形式呈现在读者面前。它不仅是"国家集成电路工程领域工程硕士系列教材"的重要组成部分,更是国内物理设计教育领域的开山之作。

二、内容深析:十章内容构建完整知识体系

本书共10章正文加16个附录,构成了从理论基础到工程实践的完整闭环。让我们逐一解读其核心内容:

第1章:集成电路物理设计方法------建立全局视野

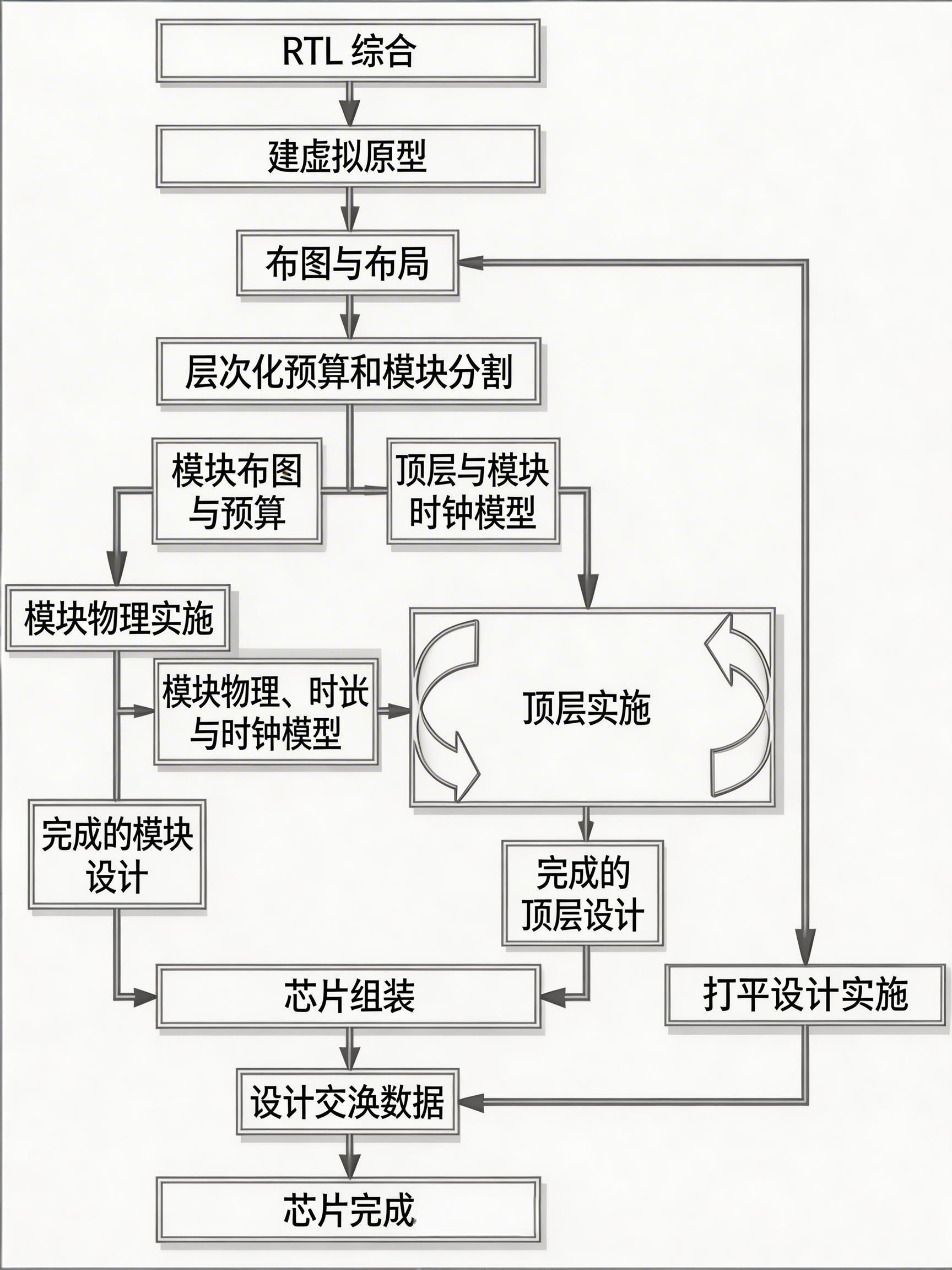

开篇即高屋建瓴地介绍了数字集成电路设计的挑战与流程演进。从"上帝时代"的手工设计,到"英雄时代"的EDA自动化,再到纳米时代的复杂性爆炸,作者梳理了从0.25μm到45nm工艺节点下设计流程的变迁。特别值得关注的是对三种物理设计方法的阐述:

展平式物理设计(Flat Design): 适合小规模设计,自底向上构建

硅虚拟原型设计(SVP): 快速评估与分割,缩短设计周期

层次化物理设计(Hierarchical Design): 应对超大规模SoC的必然选择

这一章帮助读者建立流程思维,理解物理设计不仅仅是"跑工具",而是时序、功耗、面积、可制造性(DFM)的多维博弈。

第2章:物理设计建库与验证------奠定基石

标准单元库是物理设计的"乐高积木"。本章详细介绍了:

CMOS工艺基础: 从阱工艺到SOI技术,理解制造对设计的约束

版图验证: DRC(设计规则检查)、LVS(版图与电路图一致性检查)的原理与实现

寄生参数提取: RC提取的算法与文件格式(SPEF、DSPF等)

标准单元库建立: 从逻辑单元分类到LEF/.lib文件生成,再到时序单元(ECSM/CCSM)建模

对于想深入理解Liberty文件、LEF文件格式的读者,这一章提供了清晰的技术路线图。

第3章:布图规划和布局------决定芯片成败的第一步

"好的开始是成功的一半",Floorplan的质量直接决定芯片的性能上限。本章涵盖:

布图规划(Floorplan): I/O布局、电源网络设计、宏单元(Macro)摆放、布线通道规划

电源规划: 电压降(IR Drop)分析、数字/模拟混合供电、多电压域(Multi-Voltage)设计

布局算法: 展平式布局与层次化布局的策略,扫描链重组(Scan Chain Reordering)技术

特别值得一提的是对电源网络设计的详细讲解,这是当前高性能芯片设计中的关键挑战。

第4章:时钟树综合------芯片的"心跳"工程

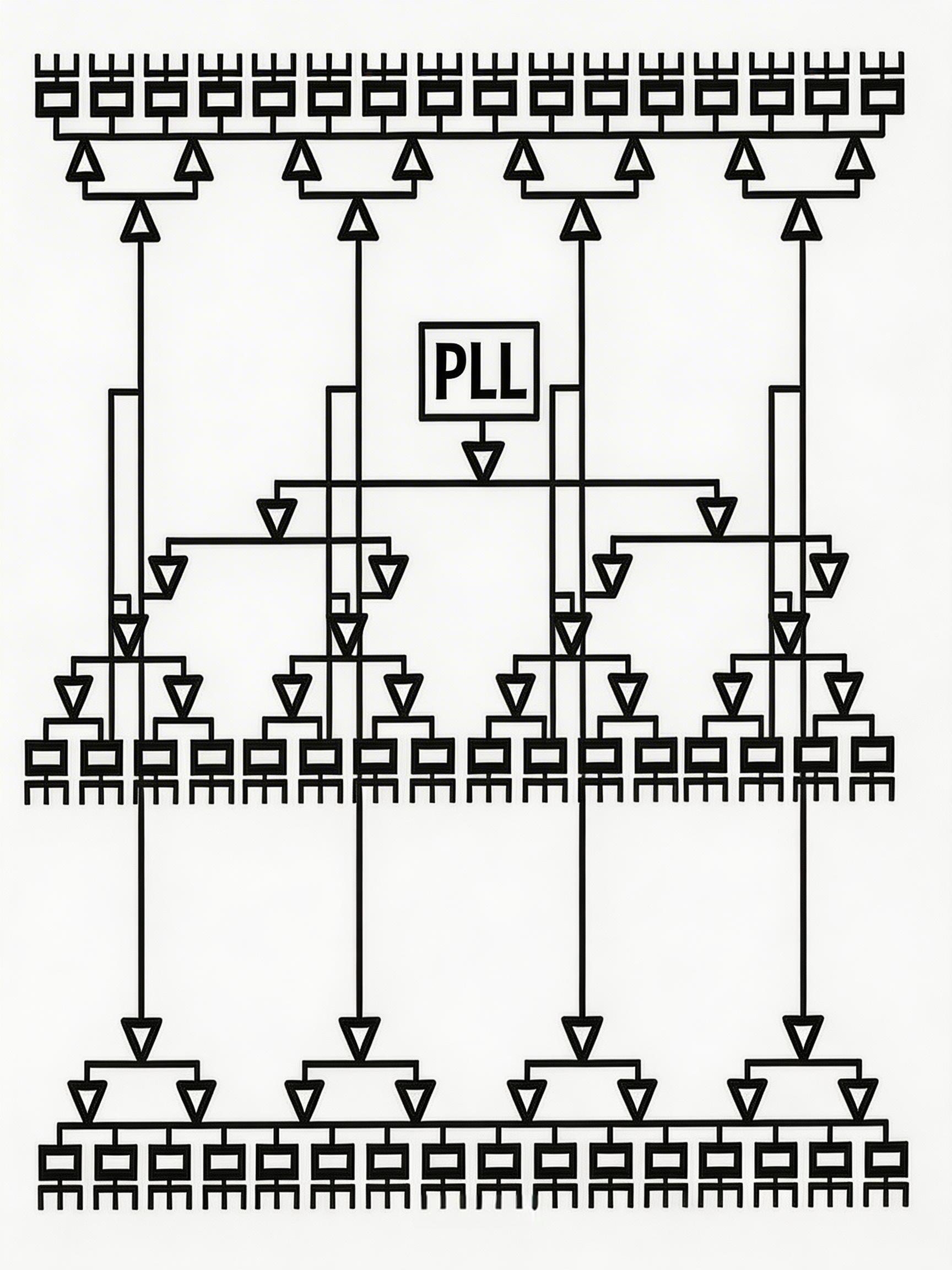

时钟信号是数字芯片的脉搏。本章系统讲解了:

时钟信号基础: 时钟偏斜(Skew)、抖动(Jitter)、延迟(Latency)的定义与影响

CTS方法: 基于标准设计约束(SDC)的时钟树综合,H树、鱼骨树等拓扑结构

先进策略: 有用偏斜(Useful Skew)技术、异步时钟树设计、门控时钟(Clock Gating)的物理实现

对于困扰许多工程师的"时钟树收敛"问题,本章提供了从约束定义到综合策略的完整解决方案。

第5章:布线------连接的艺术

当布局确定后,布线(Routing)决定了芯片的互连质量。本章区分了:

全局布线(Global Routing): 快速路径规划与拥塞评估

详细布线(Detailed Routing): 处理设计规则、天线效应(PAE)、布线修正

特殊布线: 电源网络布线、时钟树布线、总线(Bus)布线策略

虽然出版于2008年,但其中关于天线效应预防、布线算法(如A*算法、通道布线)的基础原理至今仍然适用。

第6章:静态时序分析------数字设计的"体检报告"

时序收敛是物理设计的核心目标。本章深入剖析:

延迟计算: 互连线RC模型(2.5D/3D提取)、Elmore延迟模型

寄生参数文件: SPEF、SDF(标准延迟格式)的语法与应用

STA方法: 建立/保持时间检查、时序路径分析、统计静态时序分析(SSTA)

时序优化: 造成时序违例的因素分析及ECO(工程变更指令)修复方法

这一章的内容与工业界PrimeTime等工具的使用紧密结合,极具实战价值。

第7章:功耗分析------应对"功耗墙"挑战

随着工艺演进,功耗已成为与性能同等重要的指标。本章涵盖:

静态功耗: 漏电流机制(反偏二极管、亚阈值、栅泄漏)

动态功耗: 开关功耗与短路功耗计算

电压降与电迁移: IR Drop对时序的影响、EM(Electromigration)分析

功耗文件格式: CPF(通用功耗格式)的介绍

对于低功耗设计中的多电压技术(MSMV)和电源关断(PSO),本章奠定了理论基础。

第8章:信号完整性分析------纳米时代的"噪声"管控

在130nm以下工艺,信号串扰(Crosstalk)成为影响芯片功能和性能的关键因素。本章讲解:

串扰机制: 耦合电容、噪声容限、串扰与延迟/功耗的关系

分析方法: 静态噪声分析、虚拟串扰分析

预防与修复: 屏蔽线插入、驱动能力调整、布线间距优化

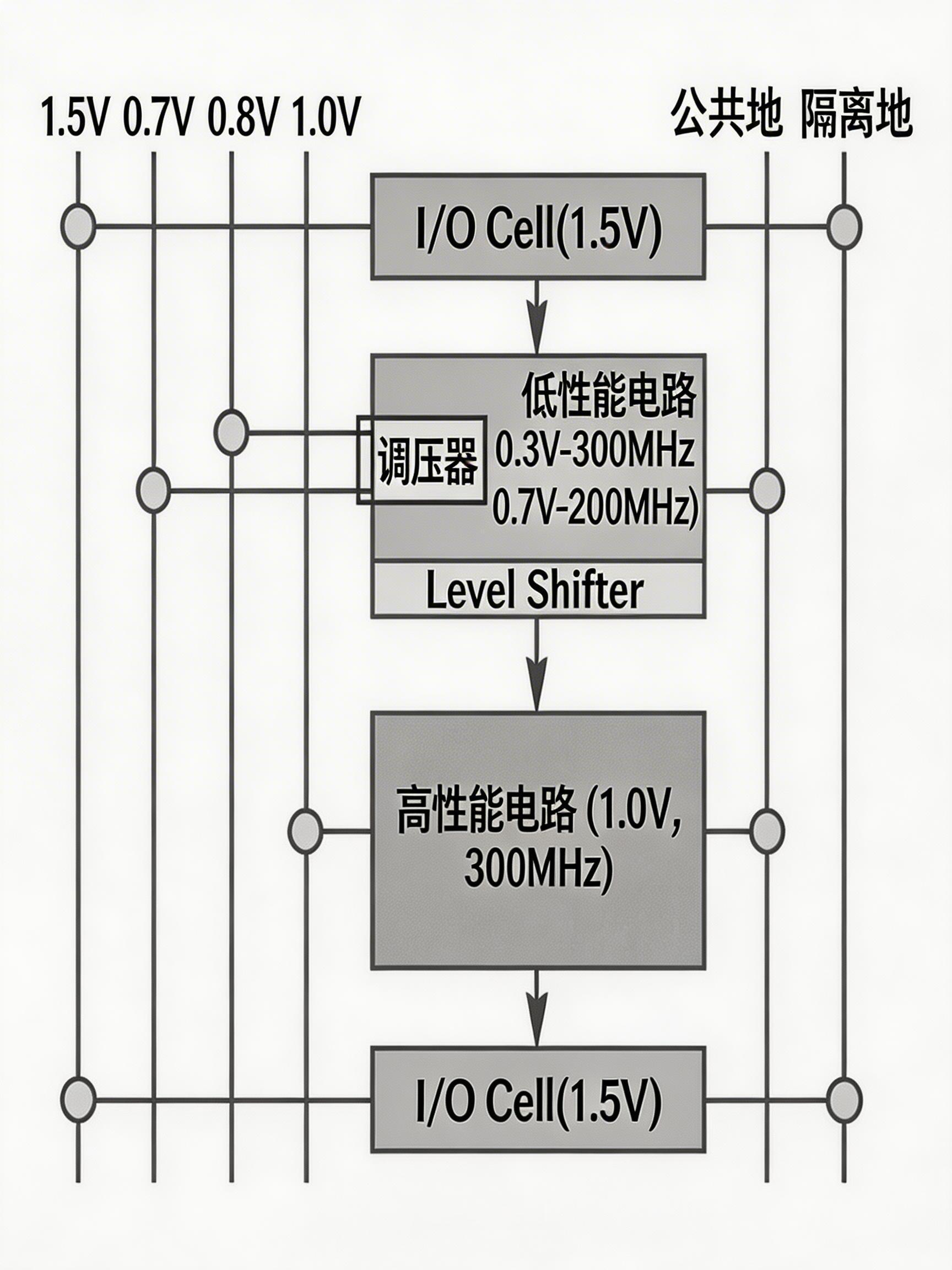

第9章:低功耗设计技术与物理实施------从架构到晶体管

作为本书的特色章节,本章将低功耗设计从架构层面落实到物理实现:

设计方案: 多阈值电压(MTCMOS)、门控时钟、动态电压频率调节(DVFS)

物理实施: 电源关断(Power Shut-off)的物理实现、状态保持电源门控(SRPG)技术

电源域管理: 多电压域的布图策略、电平转换器(Level Shifter)布局

第10章:芯片设计的最终验证与签核------通往流片的"最后一公里"

流片前的最终检查(Sign-off)是质量的守门员。本章介绍:

时序验证: MMMC(多模式多角)分析方法、OCV(片上变异)处理

物理验证: DFM(可制造性设计)、CMP(化学机械抛光)效应、光刻检查

逻辑等效验证: 形式验证与ECO流程

三、16个附录:工程师的"速查手册"

本书的价值不仅在于正文,更在于其16个详尽的附录,堪称数字IC设计文件格式的"百科全书":

设计交换格式: LEF(库交换格式)、DEF(设计交换格式)、GDSII(版图数据)

时序与功耗: SDC(时序约束)、SPEF/DSPF/RSPF(寄生参数)、SDF(延迟)、CPF/TCF(功耗)

设计语言: VHDL、Verilog HDL、VCD(波形文件)简介

对于经常需要处理各种标准文件格式的工程师,这些附录提供了极具价值的语法参考。

四、本书特色:为什么它历经16年仍值得阅读?

尽管本书出版于2008年,当时的先进工艺还是45nm,但其在今天仍然具有重要参考价值:

1.系统性极强

不同于零散的技术博客或工具手册,本书构建了从RTL到GDSII的完整知识图谱,帮助读者建立"端到端"的系统思维。

2.理论与实践并重

书中不仅讲解算法原理(如布线算法、布局优化算法),更强调工程实现细节(如天线效应处理、电源网络规划),体现了"工程硕士教材"的定位特色。

3.填补中文资料空白

许多概念(如Useful Skew、Silicon Virtual Prototyping、Hierarchical Design Flow)在当时的英文资料中也属前沿,本书首次将其系统性地引入中文教材。

4.工具无关性

虽然书中提及Cadence等工具,但核心方法论具有普适性,适用于Synopsys、Mentor等不同EDA平台。

当然,作为一本16年前的著作,读者也需要注意其局限性:

工艺节点停留在45nm,对于FinFET、EUV光刻等当代技术涉及较少

对先进封装(Chiplet、3D IC)的讨论缺失

部分EDA工具版本已更新,界面可能有所不同

但物理设计的基础原理------布局布线、时序分析、功耗优化、信号完整性------并未随工艺进步而过时,只是约束条件变得更加复杂。理解本书中的基础,正是掌握当代7nm、5nm设计方法的阶梯。

五、适合谁阅读?

高校学生: 集成电路、微电子专业研究生,作为后端设计课程的教材或参考书

初级工程师: 刚入行的数字后端工程师(PD Engineer),用于快速建立知识体系

转岗工程师: 从前端设计或验证转向后端实现的工程师

资深从业者: 需要系统梳理知识、查阅文件格式规范的技术专家

技术管理者: 需要理解物理设计流程以进行项目规划的管理者

结语:一本值得收藏的经典

在集成电路"卡脖子"技术备受关注的今天,培养具备全流程设计能力的工程师显得尤为重要。《数字集成电路物理设计》作为国内后端设计领域的奠基之作,虽然历经岁月,但其系统性的知识框架、严谨的工程思维和对基础原理的透彻讲解,使其依然是中文世界中最值得阅读的物理设计教材之一。

如果你正在学习数字后端设计,或是希望理解从RTL代码到真实芯片的"最后一公里"是如何实现的,这本书绝对值得你花时间去研读。建议配合当代EDA工具(如Innovus、ICC2)的实践操作,将书中的理论与现代设计方法相结合,必能收获颇丰。

技术会迭代,但基础永不过时。