3、PCB的Siwave的带反馈FB(Sensor点)的PMIC的直流阻抗仿真(DCIR)

最近对信号完整性(SI)、功率完整性(PI)比较感兴趣,博主六年前上本科时也是一个画板子好手,平时用AD软件搞点FR4的简单嵌入式的电路板子玩玩,几十兆的时钟玩得不亦乐乎,放在现在真的是out了。

现在像模像样的高大上的板子基本时钟频率非常高 ,板子上CPU和高速内存对电源、信号线有许多的要求,在实际投板前需要进行信号完整性(SI)、功率完整性(PI)的仿真,因此来学习一下下。学习资料是于博士的书籍《信号完整性揭秘》,还有配套的视频啥的,非常好用,简单开坑记录下。

Siwave是Ansys旗下的软件,专门用于SI和PI的仿真,之前用它家的HFSS非常多,这次也来尝尝鲜。软件的下载可以去老吴那边下载:Ansys EM 2025 R2 电磁仿真安装包已发布。

SIWAVE工程下载链接:PCB的Siwave的带反馈FB(Sensor点)的PMIC的直流阻抗仿真(DCIR)工程文件

0、前言

PCB的Siwave的直流阻抗仿真(DCIR)中最后提到,一般芯片会有两个要求,例如:

| Power domain | DC resistance (mΩ) -- PMIC VSW BGA → SoC BGA | DC resistance (mΩ) -- SMPS SENSE node → SoC BGA | Maximum impedance Z_specification (1--200 MHz) -- R_mid_freq (mΩ) | Maximum impedance -- L (pH) |

|---|---|---|---|---|

| VDD_MX | 17 | 7.5 | 95 | 850 |

-

PMIC VSW BGA to SoC BGA(17 mΩ)

表示从 PMIC 的开关节点(VSW)BGA 焊球,经 PCB 走线/过孔/铜层,最终到达 SoC 对应电源 BGA 的整段供电路径阻抗。

这是主功率电流的 DC 传输路径,其电阻越大,负载电流越高时在 SoC 处看到的电压越容易下降(I·R)。

-

SMPS SENSE node to SoC BGA(7.5 mΩ)

表示 PMIC 的电压反馈/采样(Sense)节点,从 SoC 电源球回到 PMIC 采样点的路径电阻。

这条路径用于让 PMIC 感知真实的 SoC 端电压,DCR 越小,采样越准确;若过大会导致 PMIC 误判实际电压,产生调压误差。

简而言之:

- 17 mΩ 是"送电路径"的 DCR(影响 SoC 端压降)。

- 7.5 mΩ 是"Sense 反馈路径"的 DCR(影响 PMIC 电压调节精度)。

其中,PMIC VSW BGA to SoC BGA 在PCB的Siwave的直流阻抗仿真(DCIR)中已经进行了仿真,SMPS SENSE node to SoC BGA的仿真需要更多的技巧,在此进行介绍。

1、SMPS SENSE node to SoC BGA仿真难点

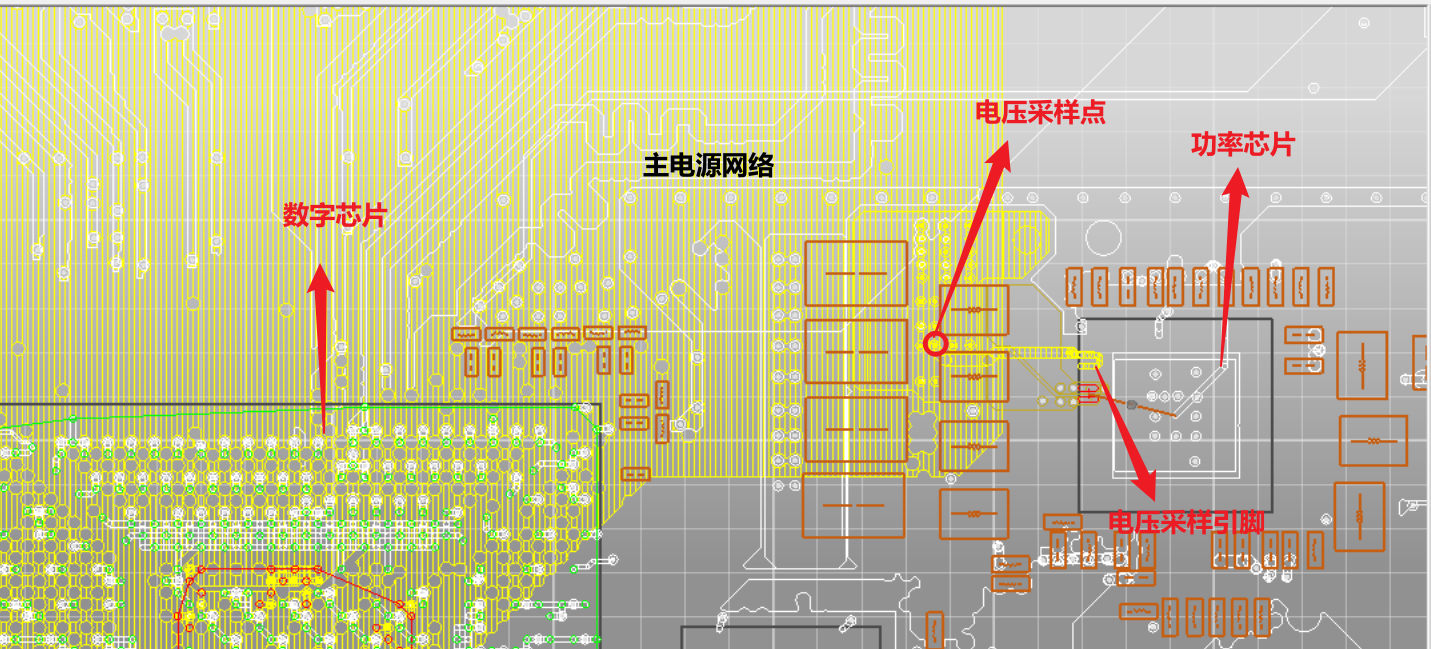

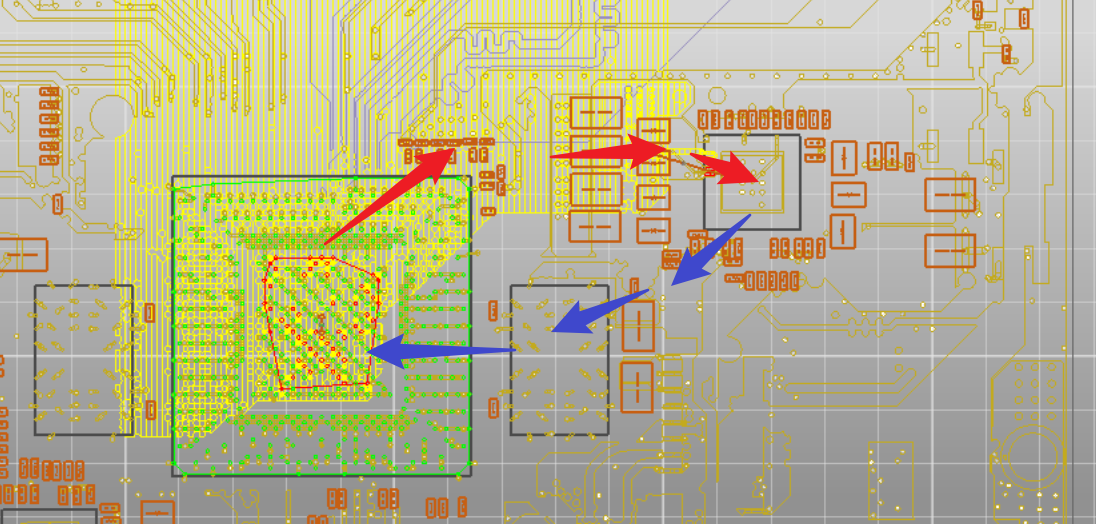

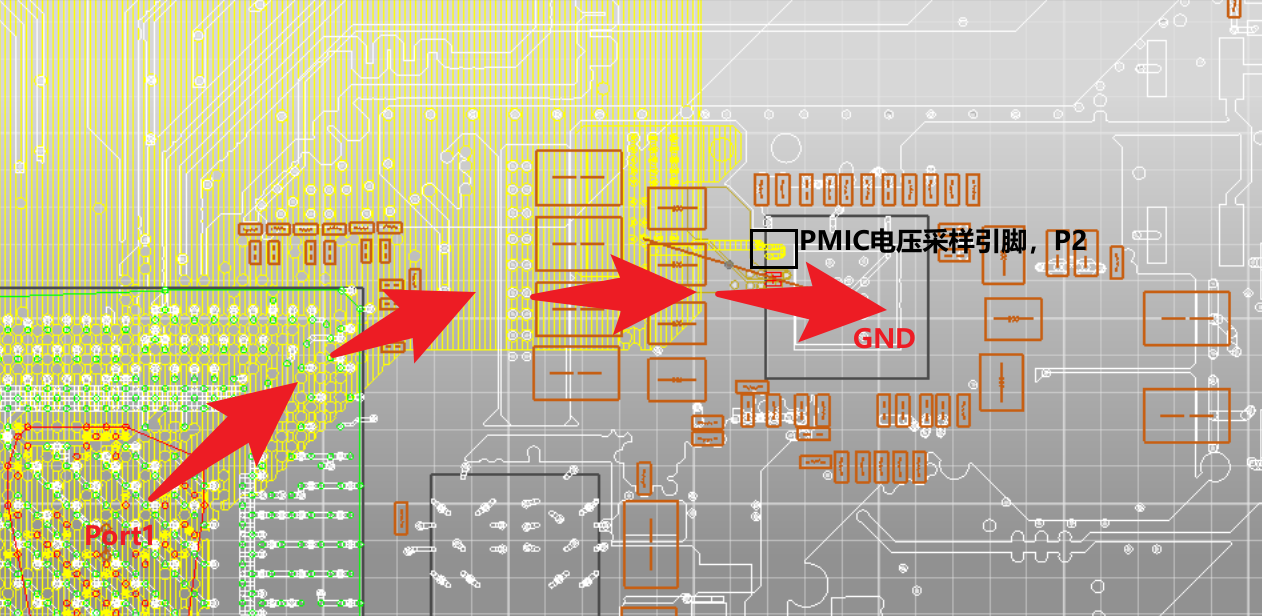

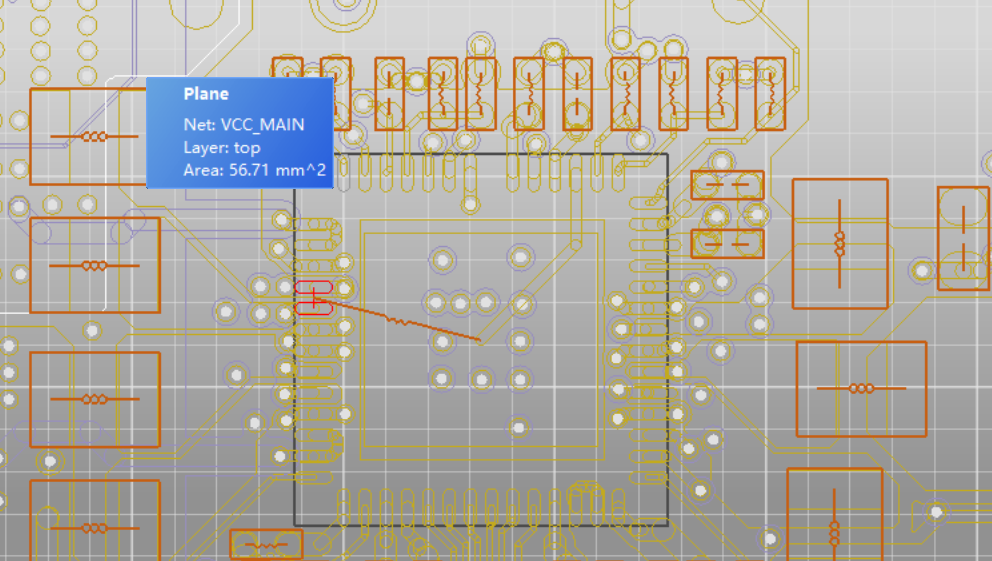

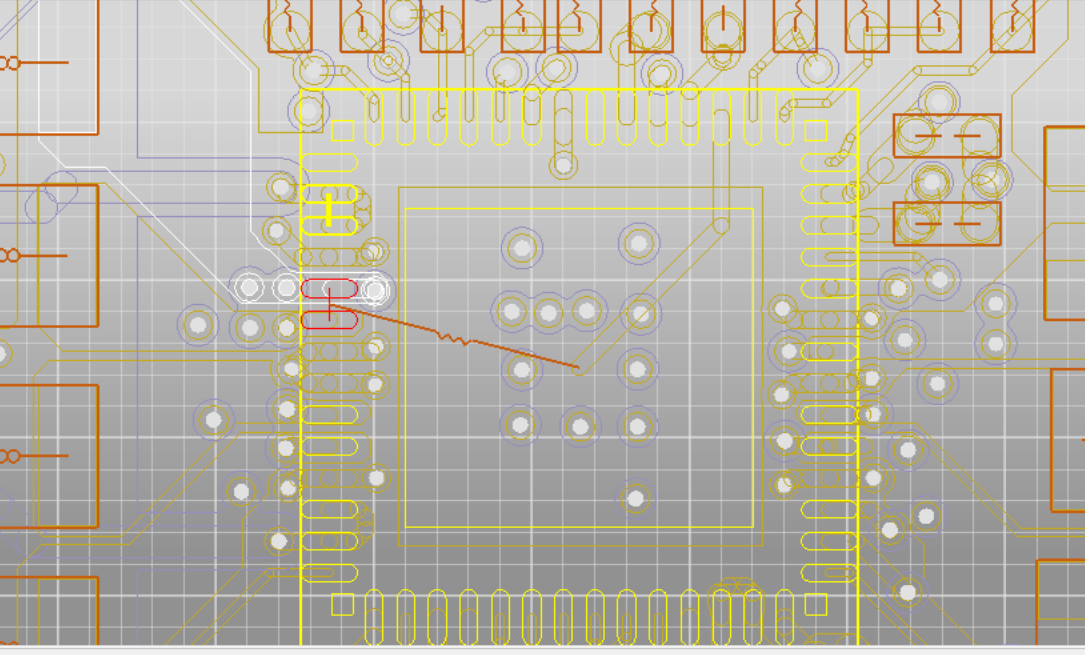

考虑和PCB的Siwave的直流阻抗仿真(DCIR)中一样的PCB,PMIC的电压采样点布局如下:

需要注意的是,图中未包含 PMIC 的主供电路径;实际大电流是经由电感 和铜皮 进入标黄网络的。PMIC 的电压采样引脚 与采样点 之间虽然采用了较窄的走线,但由于该反馈支路几乎不承载电流,因此其压降可近似忽略,采样精度通常不会因这段细线而明显下降。

但是,难点在于:电压采样点本质上是一个贯穿多层的过孔 。在计算该采样点到数字 IC 的回路电阻 时,究竟应以哪一层作为参考,并不是一个显而易见的问题。因为从建模角度看,电压源可以施加在该过孔所连接的任意一层,而不同的施加位置会对应不同的电流路径,从而得到不同的计算结果。下面对此作详细说明。

1.1 电压源加到采样点的TOP层

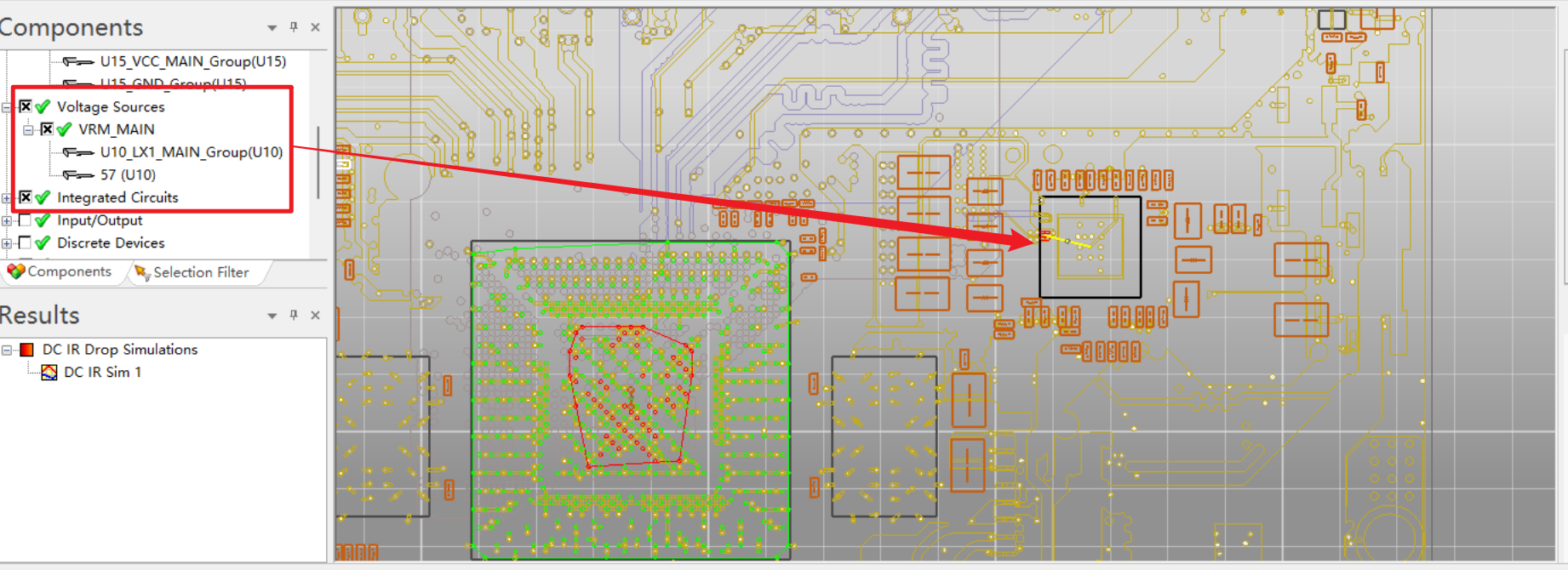

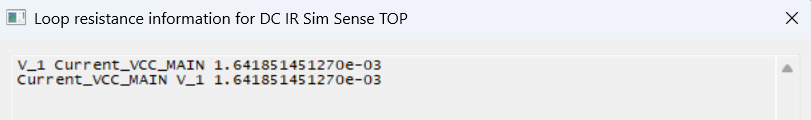

之前在PMIC上面加了电压源,此处删掉重新添加:

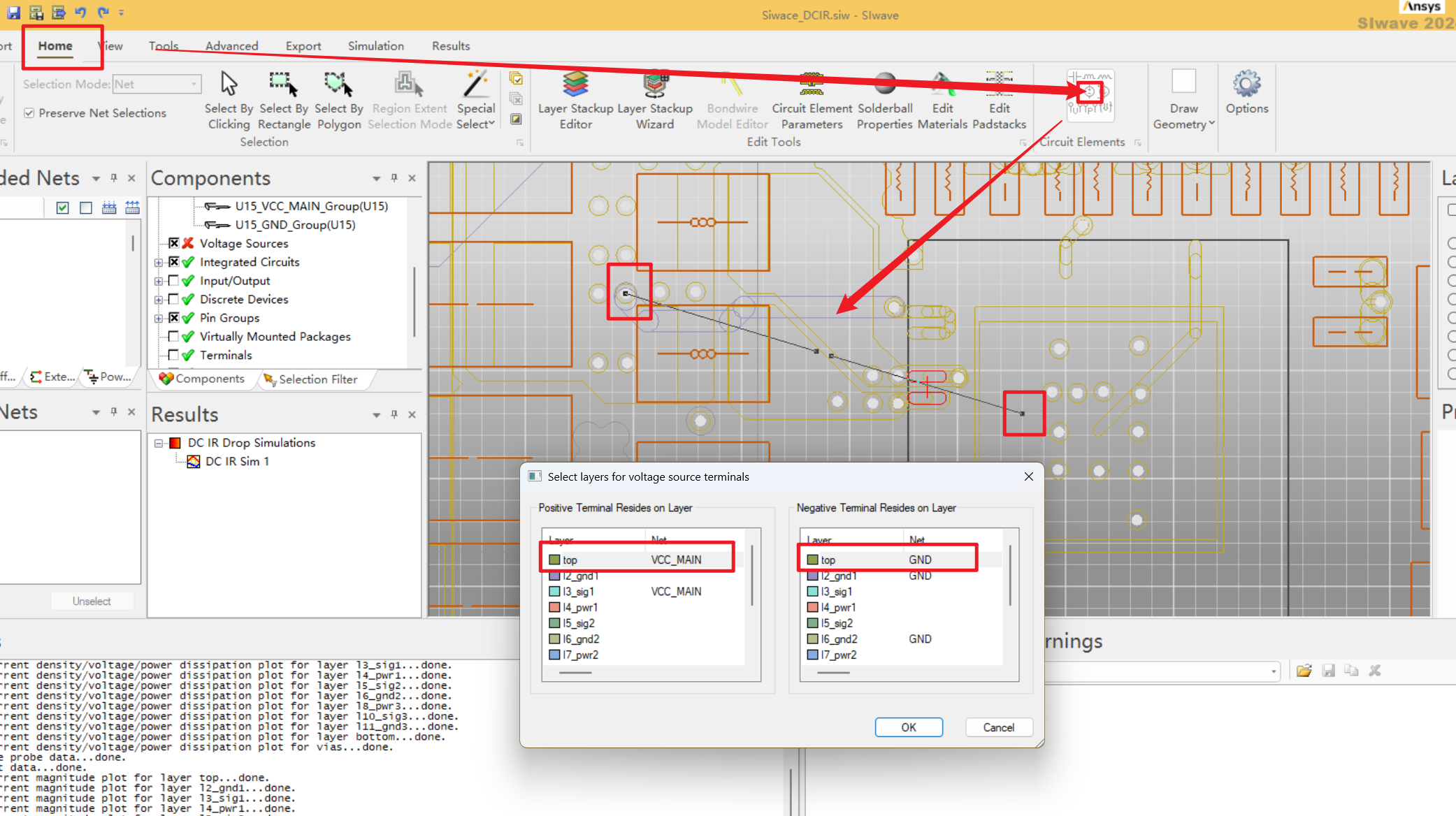

在电压采样处的TOP层添加电压源,负端选择PMIC的GNG的大PAD:

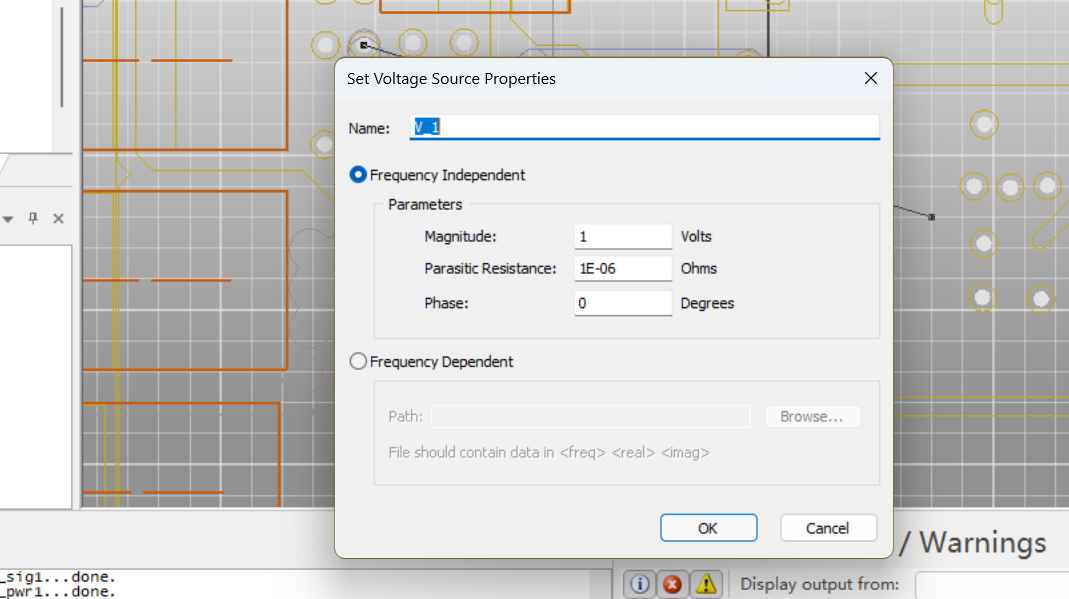

电压值设置为1V:

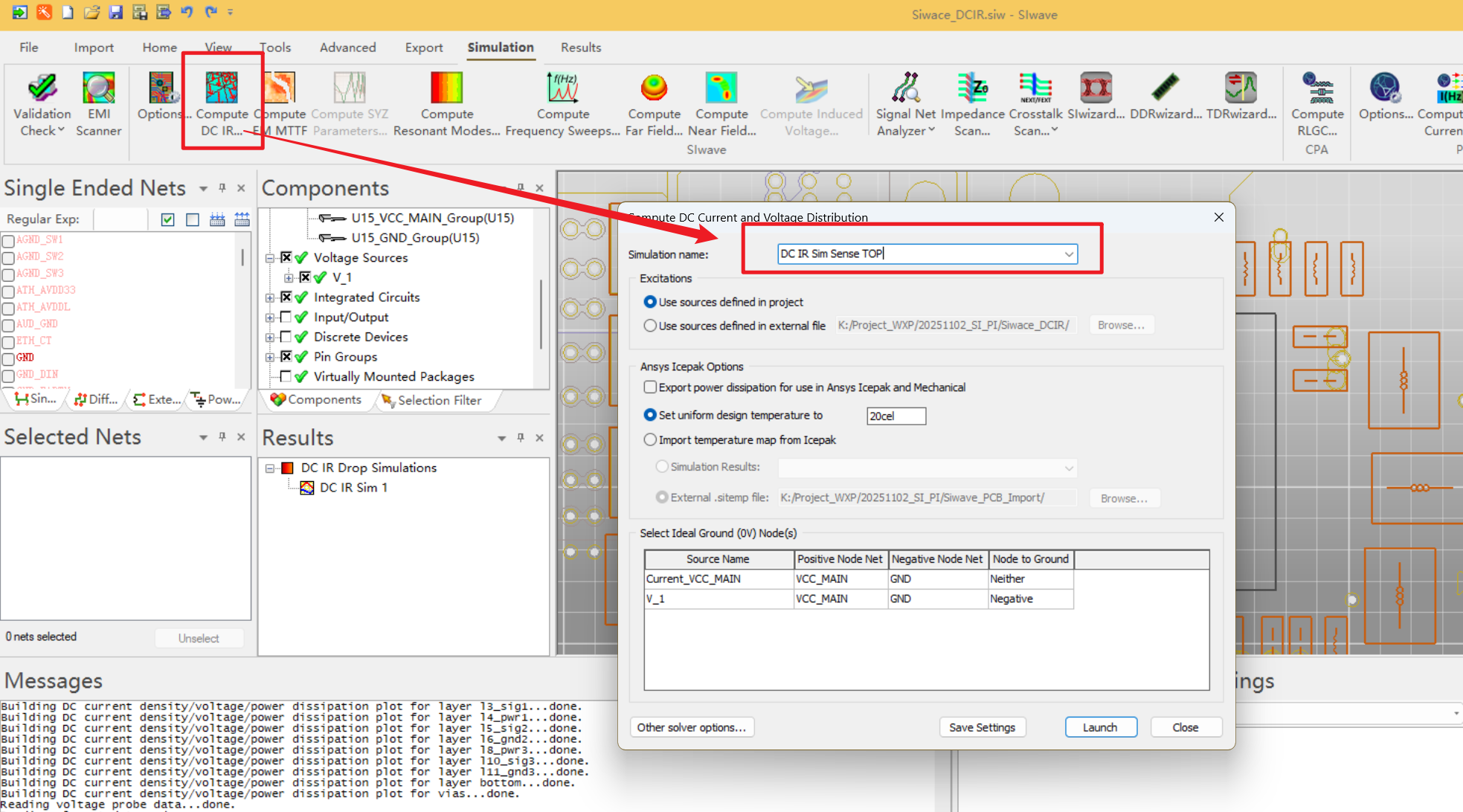

运行DCIR仿真,在命名上标注好这是Sense点的TOP层仿真:

运行完成,查看结果,SMPS SENSE node to SoC BGA的阻抗约为1.64毫欧:

1.2 电压源加到采样点的L10层

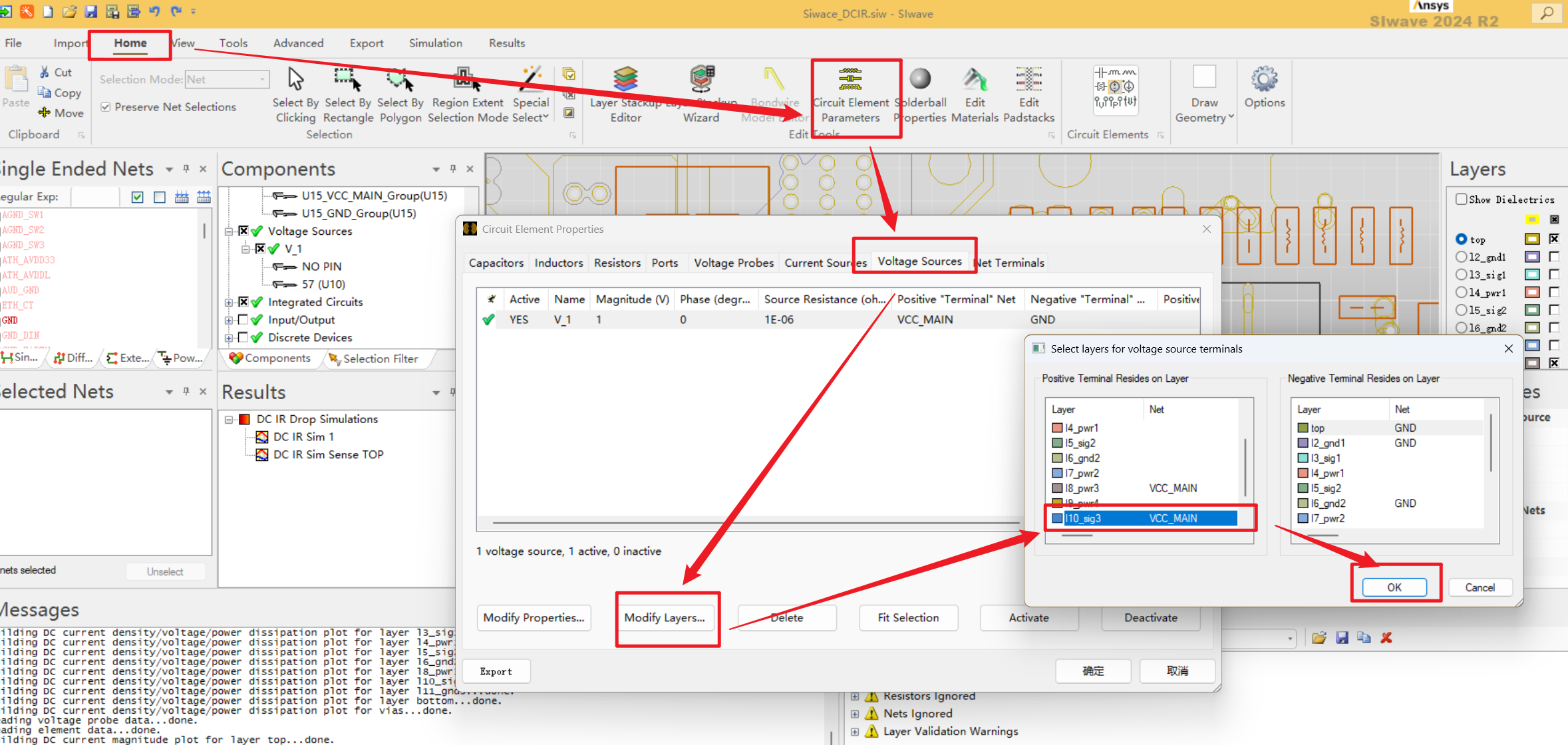

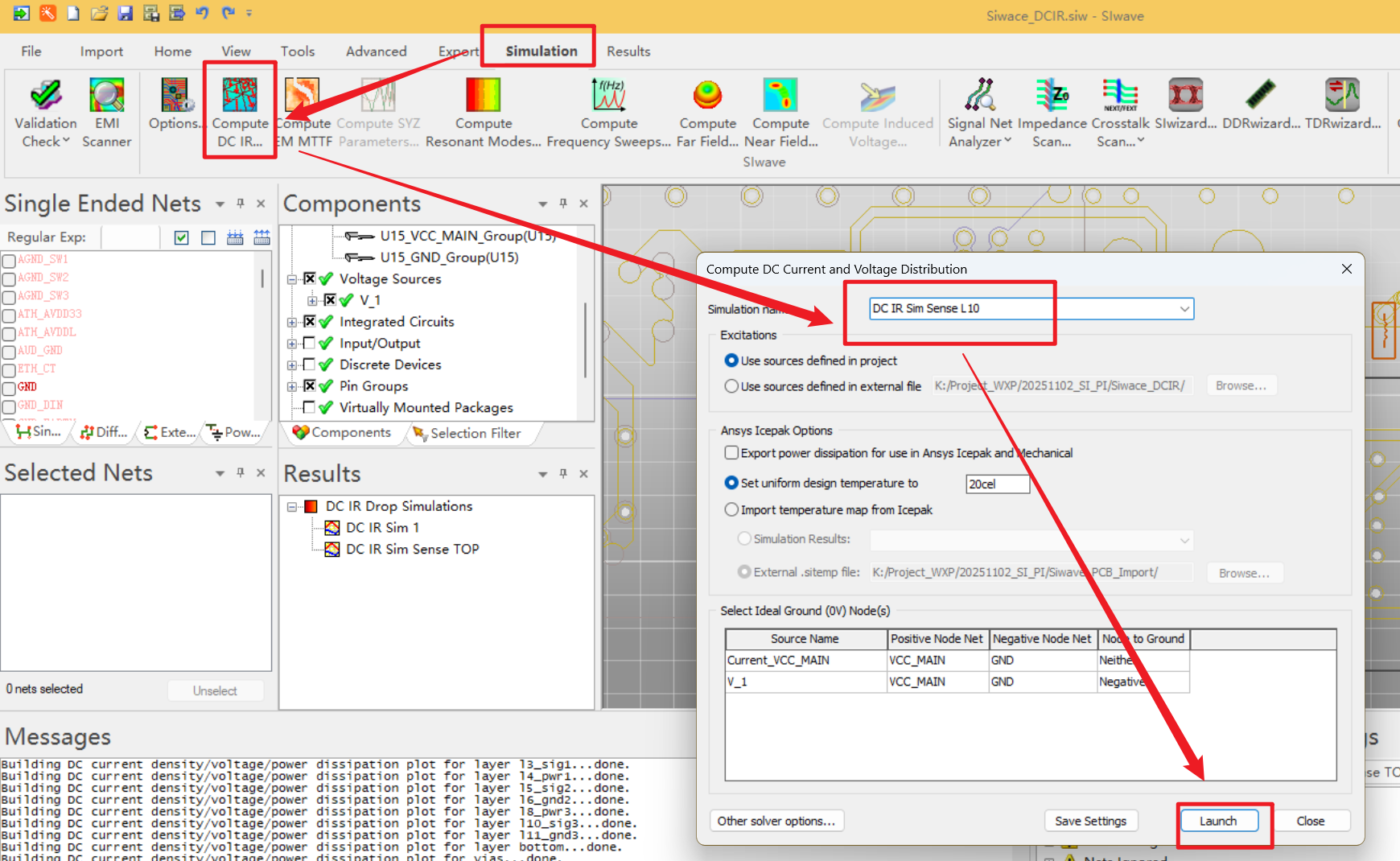

把电压源移动到第十层:

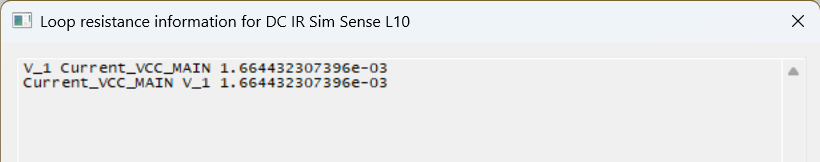

重新跑一下:

得到的结果是1.66mOhm

1.3 对比

| 电压源施加位置 | 回路电阻 | 与 TOP 相比差值 | 相对差异 |

|---|---|---|---|

| TOP | 1.64185 mΩ | 基准 | 基准 |

| L10 | 1.66443 mΩ | +0.02258 mΩ | +1.38% |

当电压源施加在采样点的 TOP 层时,计算得到的回路电阻为 1.64185 mΩ ;施加在 L10 层时,结果为 1.66443 mΩ 。两者相差 0.02258 mΩ (约 22.6 μΩ ),相对差异约为 1.38% 。这说明:对于同一个跨层过孔采样点,电压源施加层不同,得到的回路电阻会有可观但不算很大的差别。

2、SMPS SENSE node to SoC 高精度仿真

2.1、仿真理论

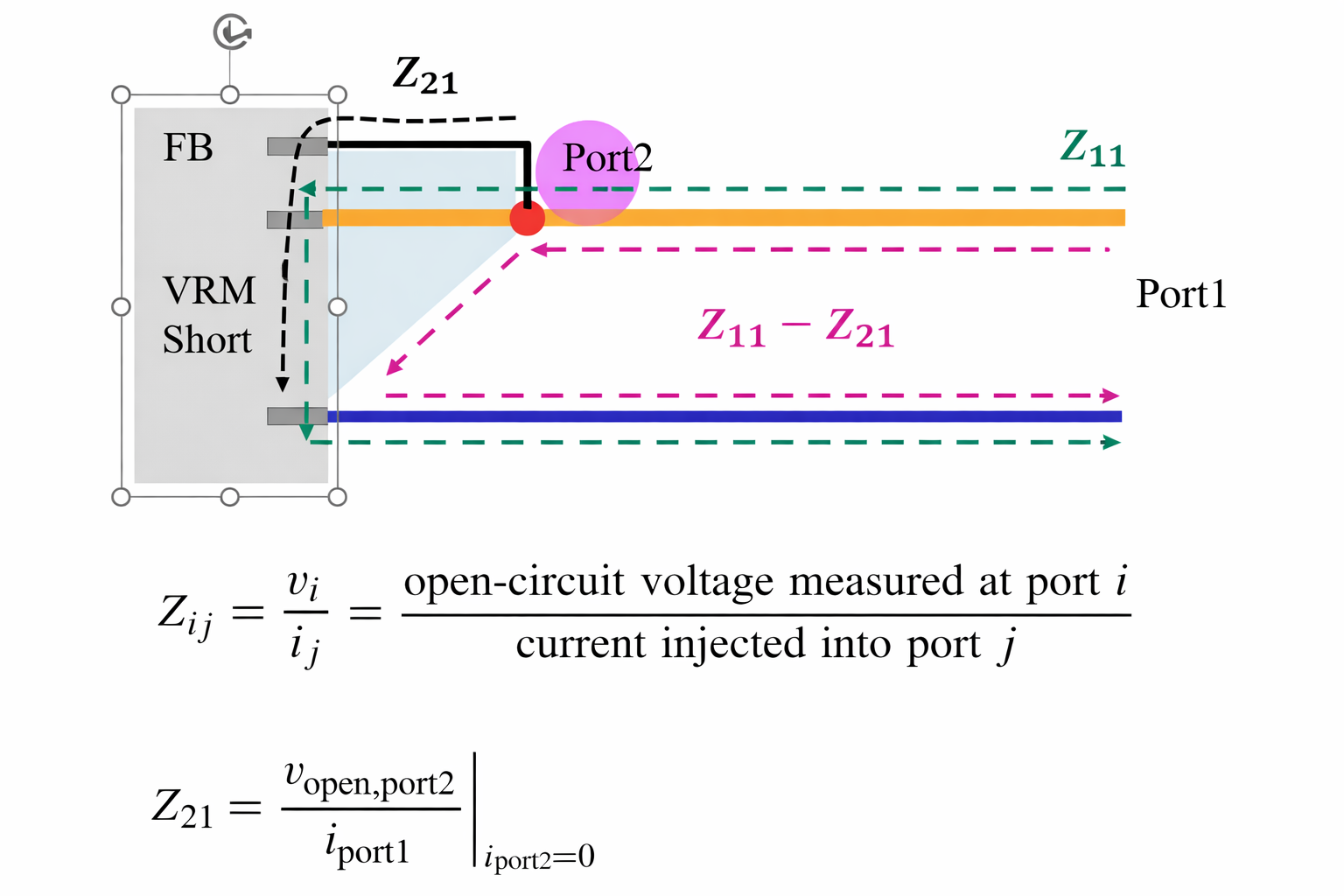

短路PMIC的电压功率输出口到GND ,然后在PMIC的电压采样引脚和IC芯片的用电网络添加Port,通过Z参数的计算得到最终的准确的SMPS SENSE node to SoC的回路阻抗。示意图如下:

之所以可以这样处理,先要明确 Z 11 Z_{11} Z11 和 Z 21 Z_{21} Z21 分别表征什么。

Z 11 Z_{11} Z11 的 1 端口加在用电 IC 的电源引脚上。计算 Z 11 Z_{11} Z11 时,2 端口处于开路 状态,因此 Z 11 Z_{11} Z11 表征的是从用电 IC 到 PMIC 功率引脚的完整回路阻抗 :电流从 Port1 正端出发,经过被短接的 PMIC 功率引脚,再返回 Port1 负端。

再看 Z 21 Z_{21} Z21 。计算 Z 21 Z_{21} Z21 时,由 Port1 施加激励,Port2 同样处于开路 状态。这里的关键在于理解 Port2 电压的物理意义:由于 2 端口开路,反馈采样支路几乎没有电流,因此 PMIC 电压采样引脚处的电压可近似视为与采样点电压相等 。也就是说,Port2 上测得的电压,实际反映的是采样点到 PMIC 功率引脚之间这段路径的阻抗特性 。如果采样引脚与 PMIC 功率输出引脚之间的阻抗为 0,那么在将 PMIC 功率输出端短接到 GND 的条件下,Port2 上就不会产生电压。

因此,Z 11 − Z 21 Z_{11}-Z_{21} Z11−Z21 的物理意义就很清楚了:它等于"从用电 IC 到 PMIC 功率引脚的完整回路阻抗"减去"从采样点到 PMIC 功率引脚的路径阻抗",最终得到的正是采样点到用电 IC 的回路阻抗,也就是我们真正需要的精确结果。

2.2、仿真实操

2.2.1、添加IC处端口

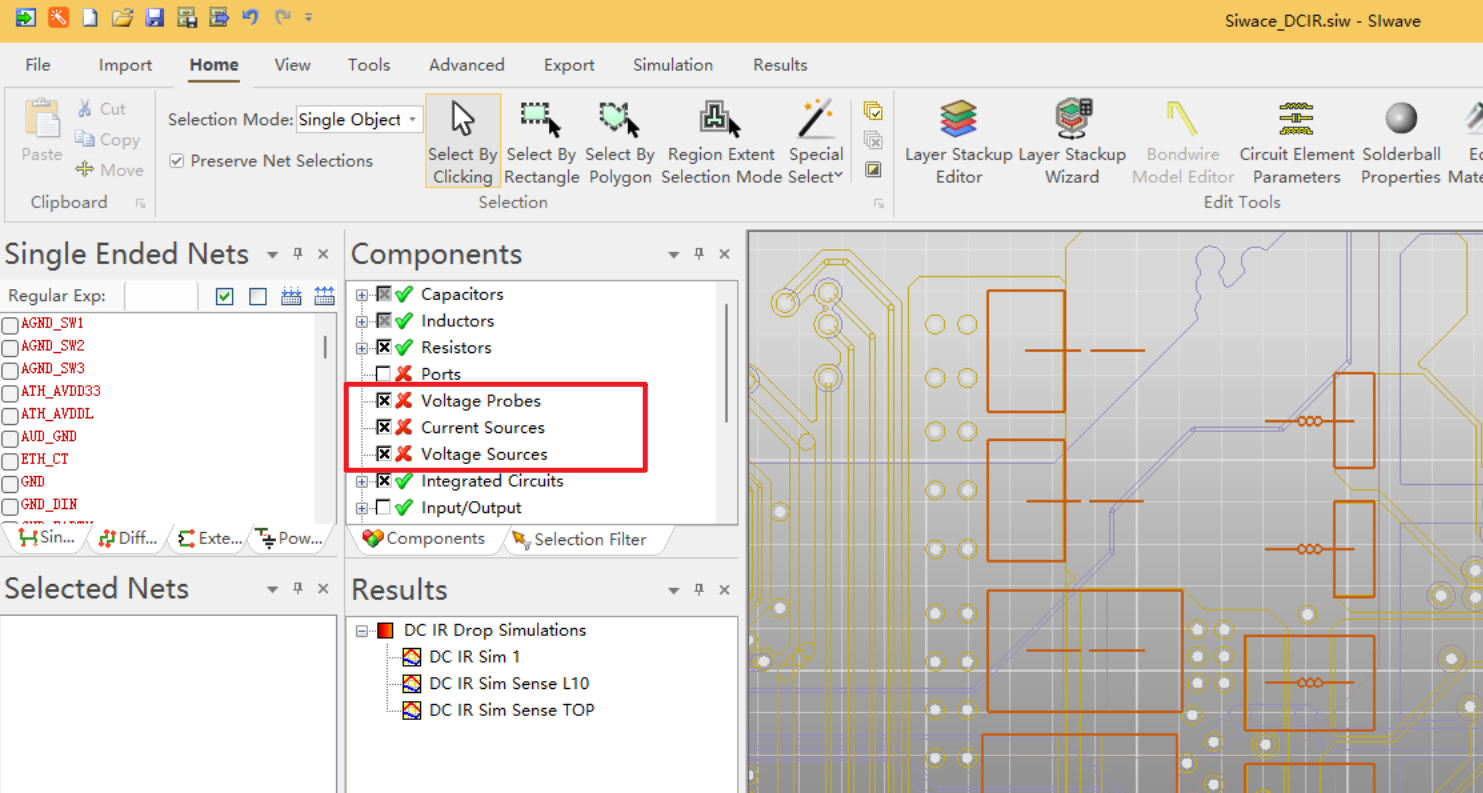

此时,不使用DCIR仿真器了,而是直接提取指定电路的Z参数矩阵,然后相减就行。先删除之前设置的电压源、电流源、电压探头:

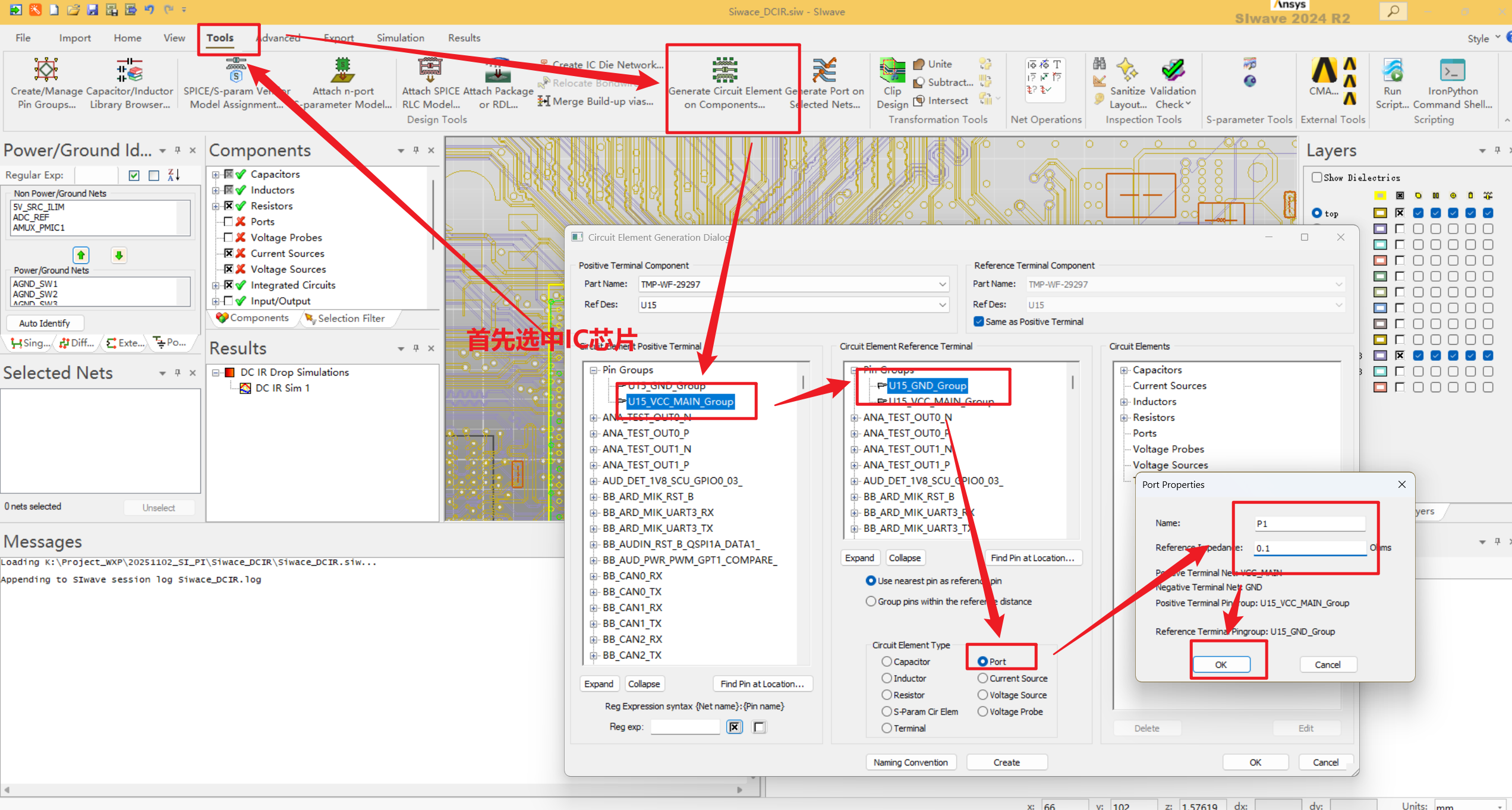

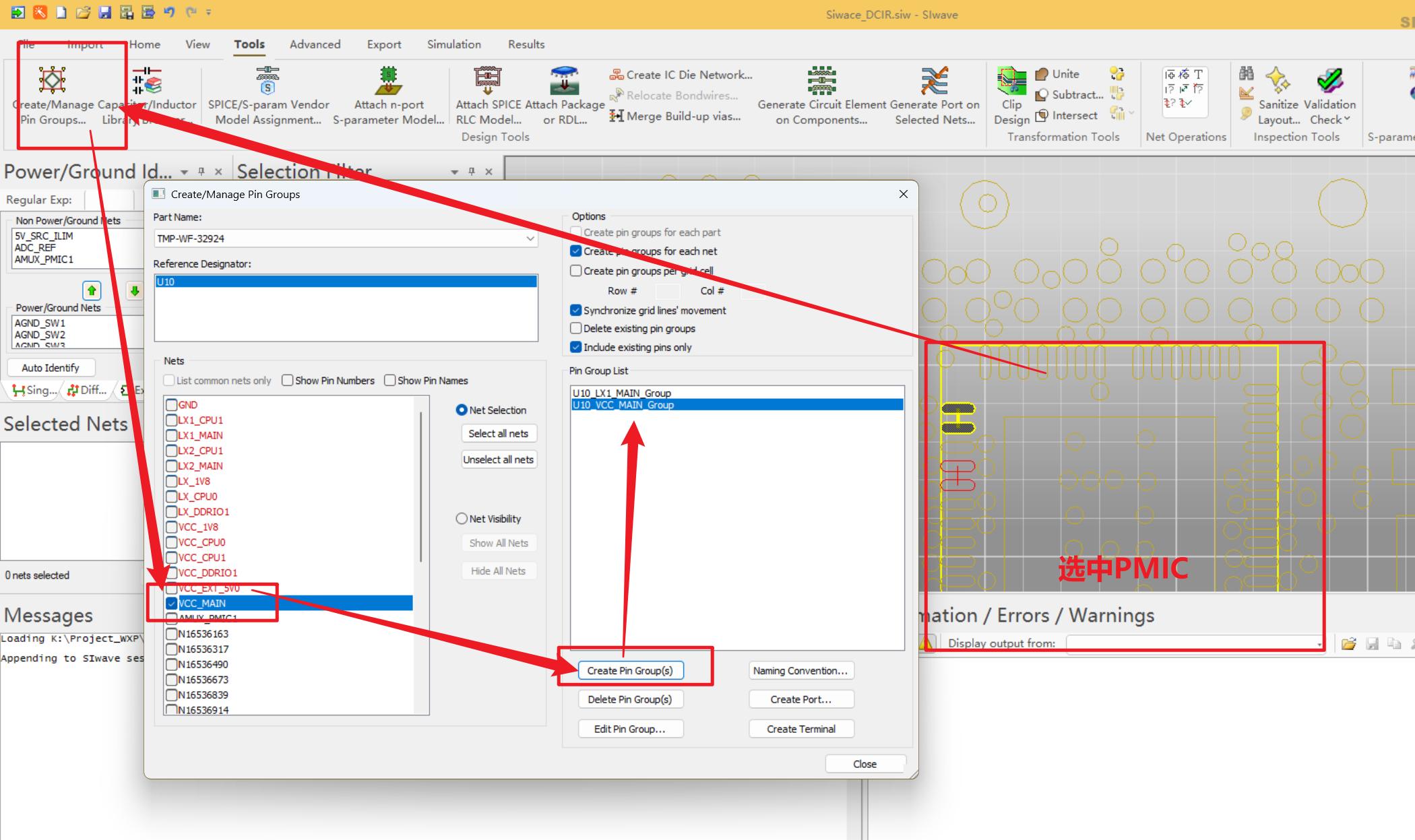

下面在用电芯片上增加Port端口,选中IC芯片,按照图片提示操作:

2.2.2、短路PMIC输出

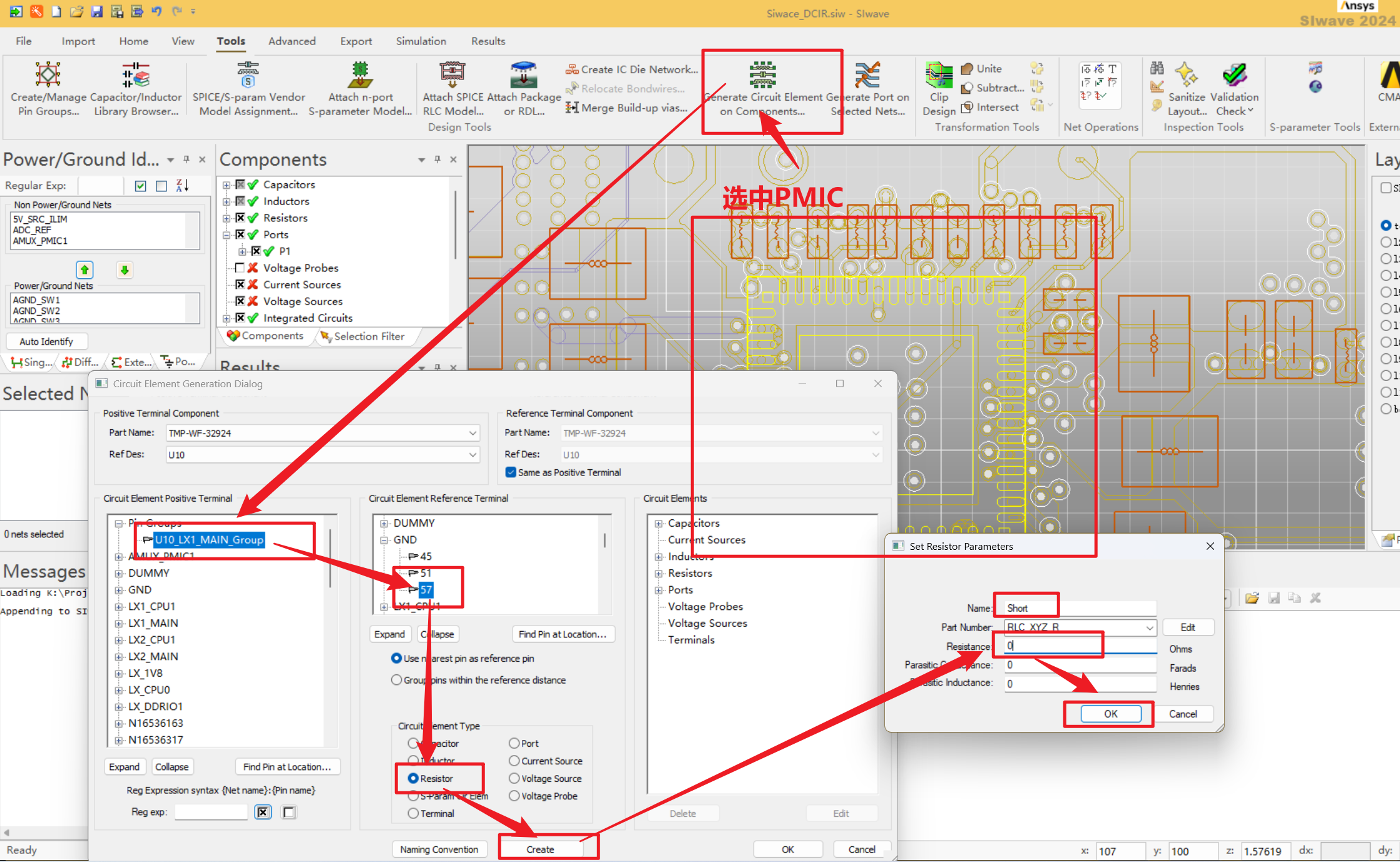

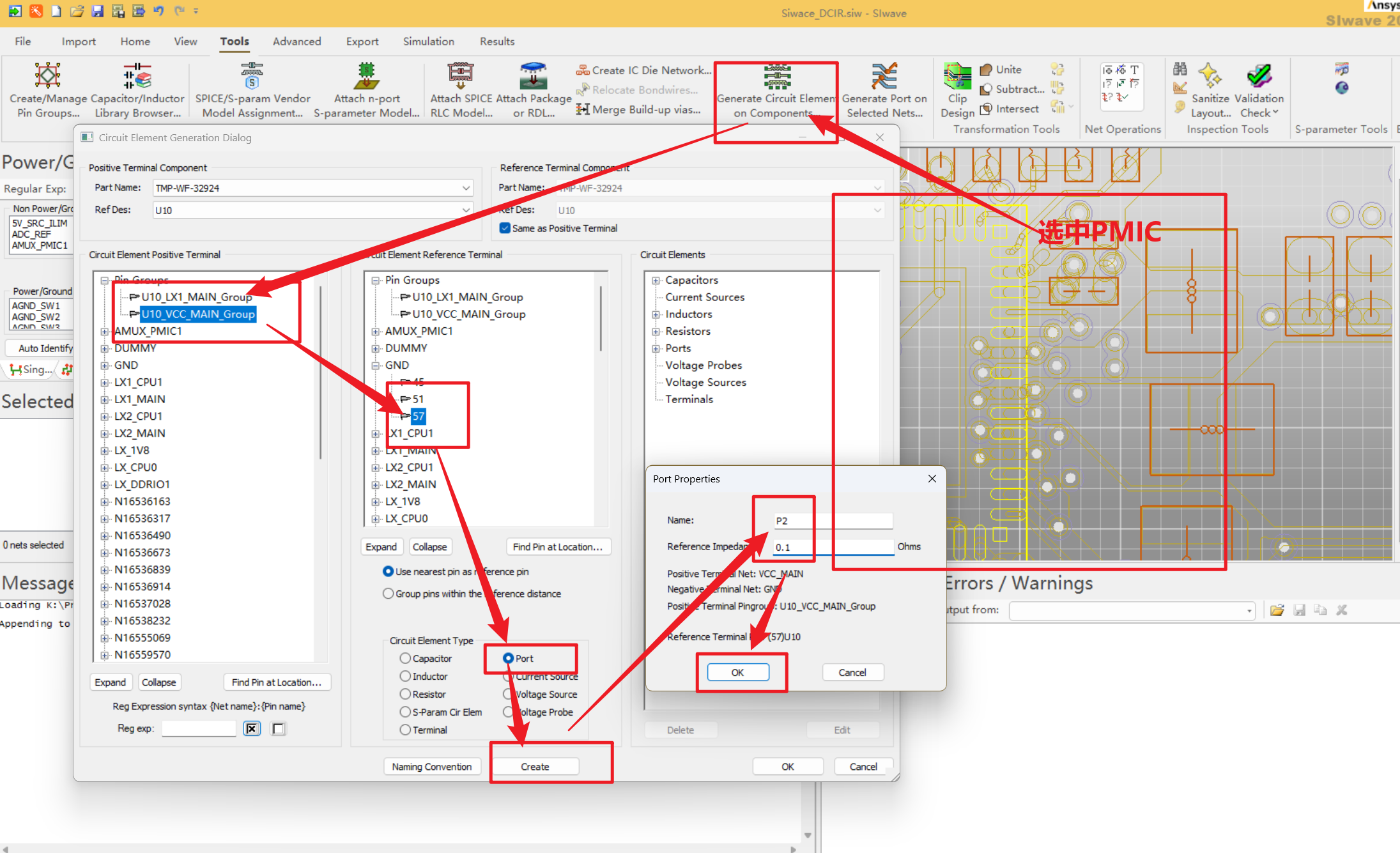

选中PMIC芯片,按照下面步骤进行操作:

设置完成后出现电阻的连接标记:

2.2.3、PMIC的Sense端口添加端口

先给两个Sense点创建PinGroup选中PMIC芯片,按照下面步骤进行操作:

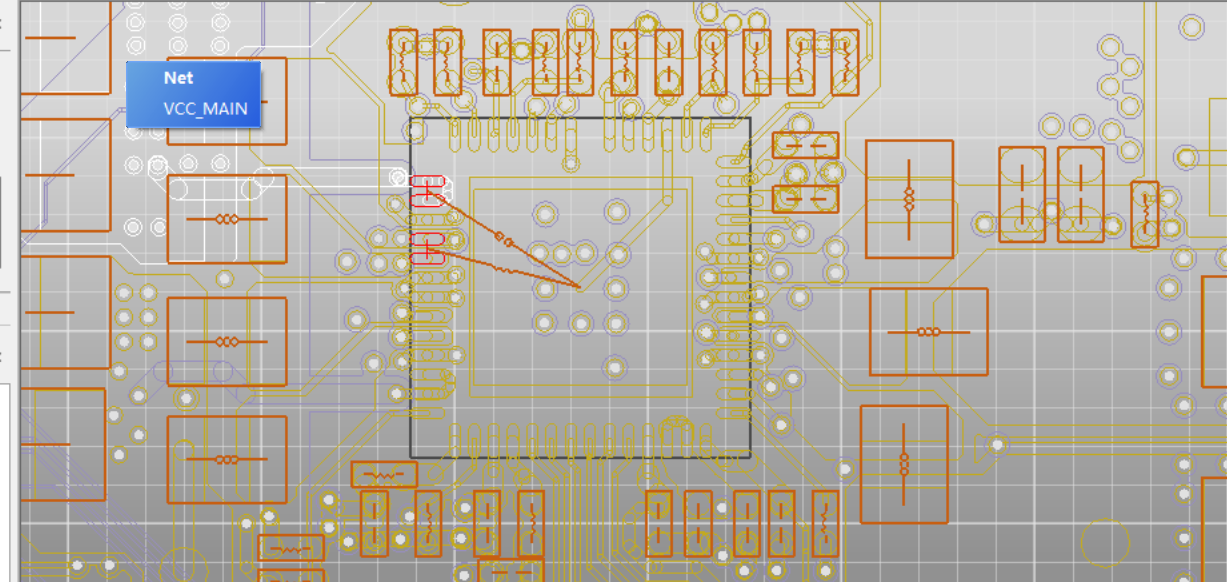

创建完成后如下所示:

然后重新选中芯片,创建端口:

设置完成如下所示:

2.2.4、仿真设置

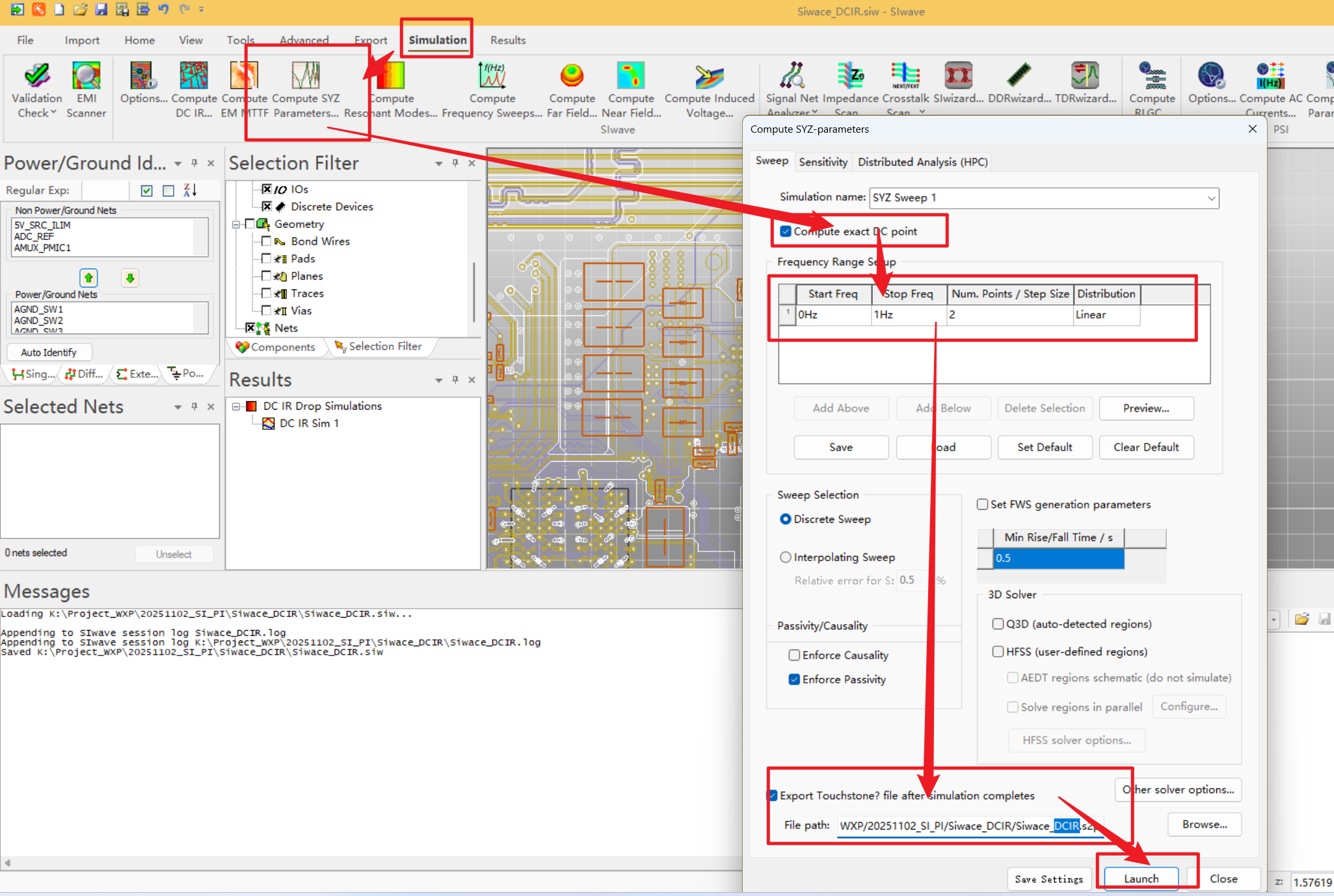

按照如下步骤设置并启动仿真,需要打开计算直流DC的框选,并设置SNP导出路径:

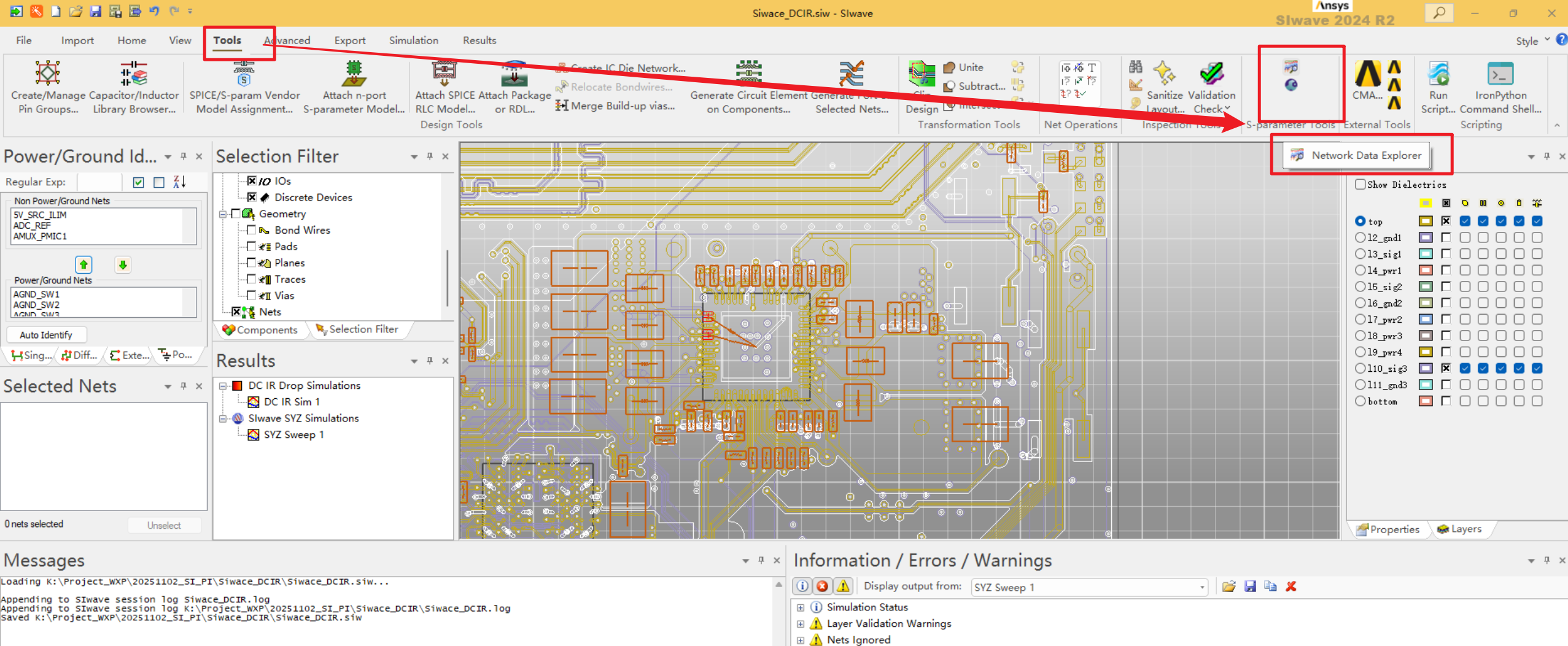

仿真完成后,打开网络分析工具:

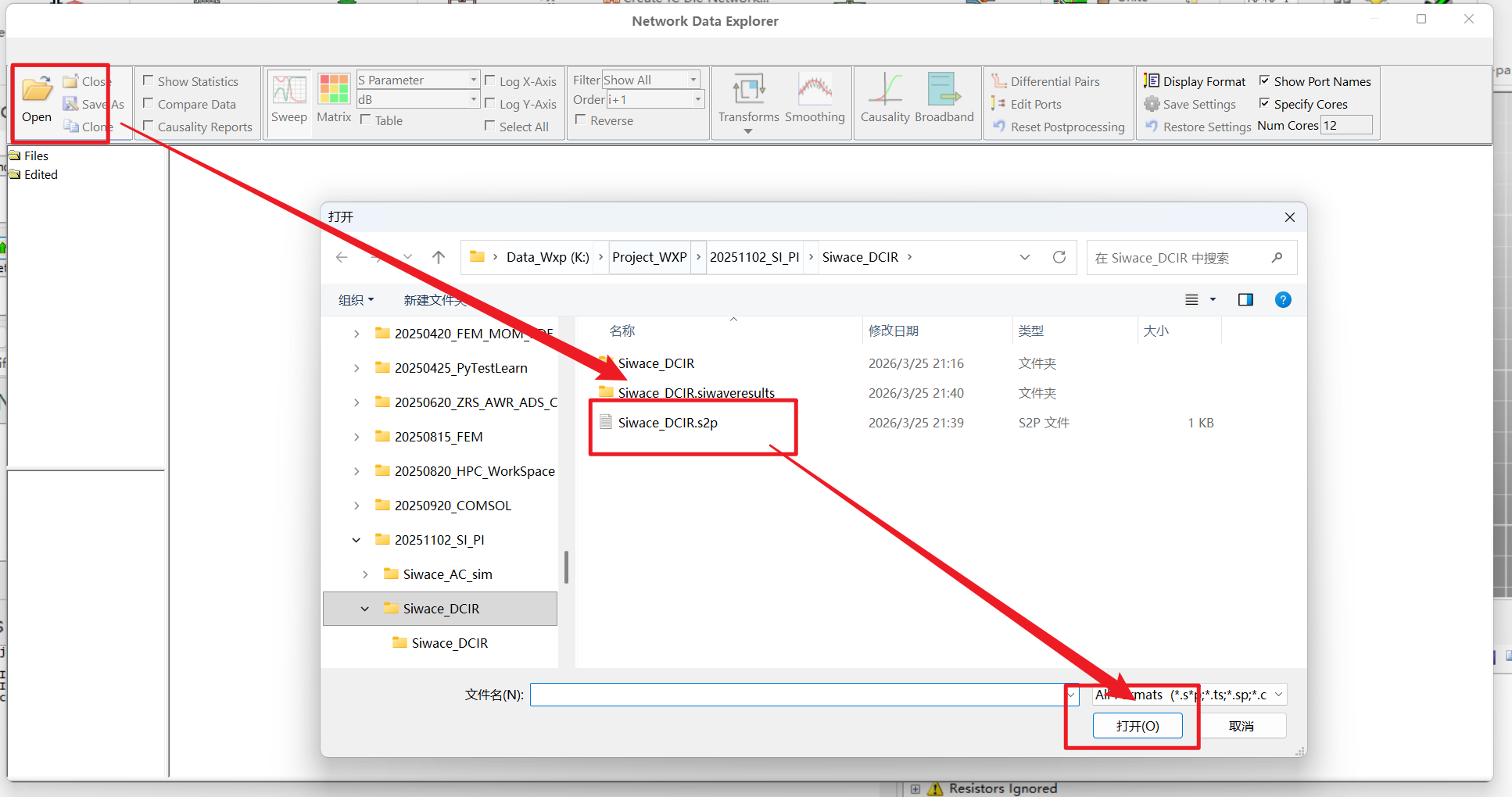

打开刚刚生成的s2p文件:

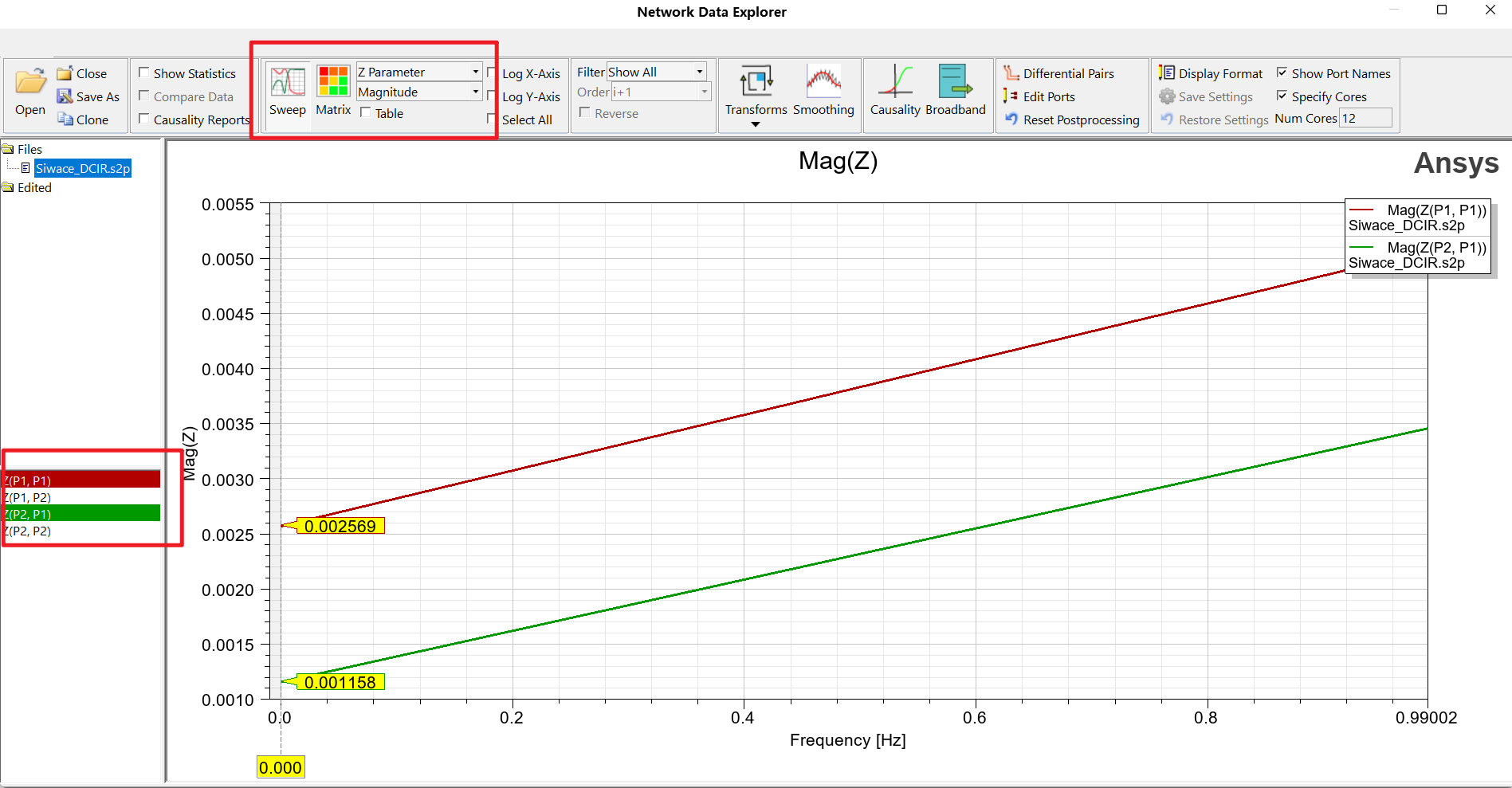

查看Z参数,并切换到幅度格式:

阻抗相减,为0.002569-0.001158=1.411mOhm。全部对比:

| 计算方法 | 结果 |

|---|---|

| Z11 − Z21 | 0.002569 − 0.001158 = 0.001411 Ω = 1.411 mΩ |

| TOP 直接计算 | 1.64185 mΩ |

| L10 直接计算 | 1.66443 mΩ |

| 对比项 | 数值 | 相对差异 |

|---|---|---|

| Z11 − Z21 vs TOP | −0.23085 mΩ | −14.06% |

| Z11 − Z21 vs L10 | −0.25343 mΩ | −15.23% |

| L10 vs TOP | +0.02258 mΩ | +1.38% |