目录

[一、ARM 处理器基本概念](#一、ARM 处理器基本概念)

[1. 什么是 ARM](#1. 什么是 ARM)

[2. ARM 与单片机(MCU)的区别](#2. ARM 与单片机(MCU)的区别)

[3. ARM Cortex 系列分类](#3. ARM Cortex 系列分类)

[二、ARM 处理器内部组成](#二、ARM 处理器内部组成)

[三、CPU / SOC / MCU / MPU 对比](#三、CPU / SOC / MCU / MPU 对比)

[四、ARM 7 种基本工作模式](#四、ARM 7 种基本工作模式)

[五、寄存器组概要(重点 CPSR/SPSR)](#五、寄存器组概要(重点 CPSR/SPSR))

[1. 通用寄存器](#1. 通用寄存器)

[2. 特殊寄存器](#2. 特殊寄存器)

[1. 栈结构](#1. 栈结构)

[1. 多核异构](#1. 多核异构)

[2. 常见术语](#2. 常见术语)

一、ARM 处理器基本概念

1. 什么是 ARM

ARM 即 Advanced RISC Machine,是一种精简指令集(RISC)处理器架构,本身不生产芯片,只对外授权架构设计。市面上的 IMX6ULL、STM32、高通骁龙等芯片,都是基于 ARM 架构设计的具体处理器。

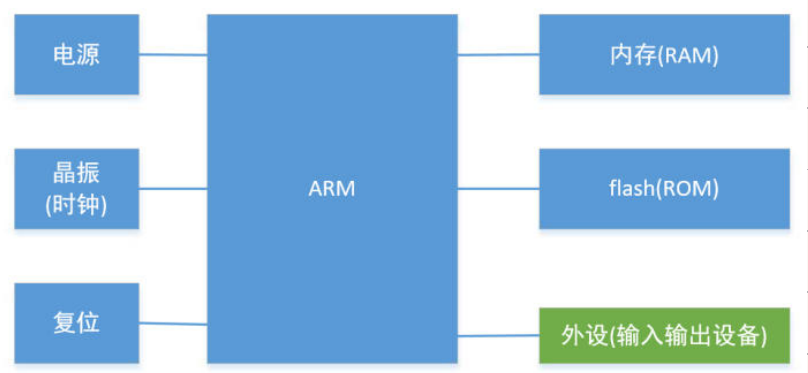

ARM最小系统:

2. ARM 与单片机(MCU)的区别

- MCU(单片机) :片上集成 CPU、小容量 RAM/ROM、通用外设,结构简单、成本低、功耗小,多用于简单控制场景,一般不带 MMU,无法运行大型操作系统。

- ARM 架构处理器:覆盖低、中、高端场景,低端可做单片机,高端型号集成 MMU、Cache、多核,性能强大,可运行 Linux、Android 等复杂系统,处理高速数据与多任务。

3. ARM Cortex 系列分类

ARM采用32位架构,具体系列可分为:

- Cortex-A:应用处理器,高性能、支持 MMU,用于手机、平板、高端嵌入式 Linux 开发板(如 IMX6ULL)。

- Cortex-M:微控制器,低功耗、实时性强,用于工控、家电、传感器节点(如 STM32)。

- Cortex-R:高实时性处理器,用于汽车电子、工业控制、硬盘控制器等对响应速度要求极高的场景。

4.RAM、ROM、FLASH的区别

| 特性 | RAM | ROM | Flash |

|---|---|---|---|

| 全称 | Random Access Memory | Read Only Memory | Flash Memory |

| 掉电数据 | 丢失 | 不丢失 | 不丢失 |

| 读写属性 | 可读可写,随机访问 | 出厂只读,几乎不可改 | 可读可擦写,按块 / 扇区操作 |

| 访问速度 | 极快(CPU 直接运行) | 较慢 | 中等(比 RAM 慢、比 ROM 快) |

| 成本 / 容量 | 贵,容量较小 | 极低,容量小 | 便宜,容量可做大 |

| 典型类型 | SRAM、DRAM(DDR) | Mask ROM、PROM、EPROM | NOR Flash、NAND Flash |

| 主要用途 | 运行程序、变量、堆栈、缓存 | 固化引导程序、出厂固定数据 | 存储固件、代码、文件、参数 |

| 嵌入式角色 | 程序运行空间 | 芯片内置 BootROM(启动用) | 存放整个系统镜像和应用程序 |

二、ARM 处理器内部组成

-

ALU 算术逻辑单元负责执行算术运算(加减乘除)与逻辑运算(与、或、非、异或、比较),是处理器的运算核心。

-

寄存器组

- 通用寄存器:R0~R12,用于临时存放数据、函数参数与局部变量。

- 特殊功能寄存器:

- PC(R15):程序计数器,指向即将执行的下一条指令地址。

- LR(R14):链接寄存器,保存函数调用或异常发生后的返回地址。

- SP(R13):栈指针,指向当前栈顶位置,管理栈的压入与弹出。

- CPSR:当前程序状态寄存器,保存标志位、运行模式、中断使能位。

- SPSR:备份程序状态寄存器,异常时保存 CPSR,返回时恢复。

-

流水线 将指令执行分为取指、译码、执行等阶段,实现多条指令并行处理,提高执行效率。ARM 常见三级 / 五级流水线,流水线冲突会影响执行效率。

-

Cache 高速缓存 分为指令缓存(I-Cache)与数据缓存(D-Cache),暂存高频使用的指令与数据,降低 CPU 访问内存的延迟。哈佛结构 :指令存储器与数据存储器分离,总线独立,可并行取指与读写数据,效率更高,现代 ARM 普遍采用。冯・诺依曼结构 :指令与数据共用同一存储空间与总线,结构简单,但吞吐率受限。

-

MMU 内存管理单元 实现虚拟地址到物理地址的映射,支持内存权限管理、分页机制,是运行 Linux 等多任务操作系统的必备硬件单元。

三、CPU / SOC / MCU / MPU 对比

| 名称 | 核心定义 | 典型特点 |

|---|---|---|

| CPU | 中央处理单元 | 仅负责运算与指令执行,无内存、无外设,需外部芯片配合 |

| MCU | 微控制器 | 单片集成 CPU + 小容量存储 + 外设,面向简单控制,无 MMU |

| MPU | 微处理器 | 高性能 CPU 核心,带 MMU,需外接内存与外设,可跑复杂 OS |

| SOC | 片上系统 | 在单芯片上集成 CPU、GPU、内存控制器、各类外设,完整系统 |

四、ARM 7 种基本工作模式

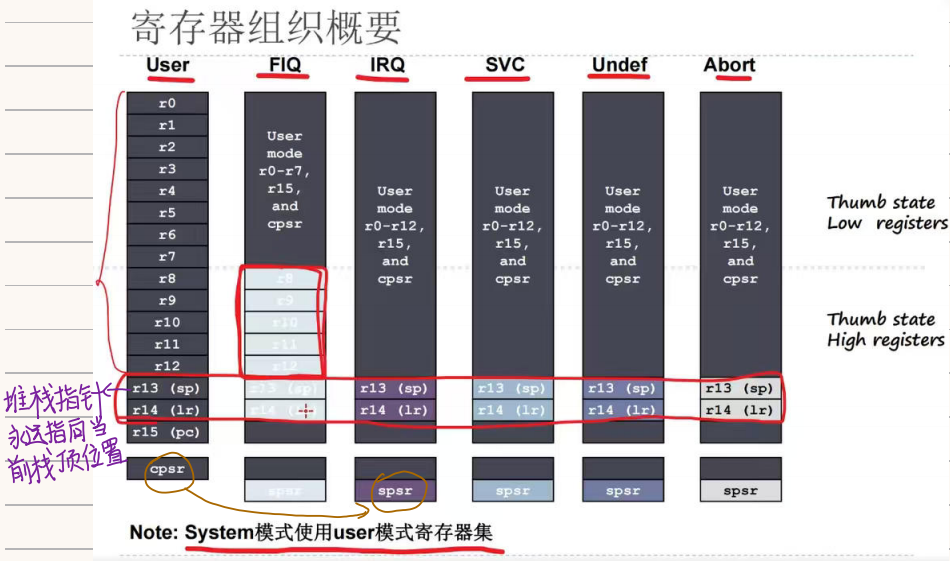

- 用户模式(User) :非特权模式(唯一的非特权模式),普通应用程序运行,受限访问系统资源。

- 系统模式(System) :特权模式,与用户模式共用寄存器,运行高权限用户任务。

- 管理模式(SVC):复位、软中断进入,操作系统内核与系统初始化使用。

- 外部中断模式(IRQ):处理通用外设中断,如 GPIO、UART、I2C 中断。

- 快速中断模式(FIQ):处理高速、紧急中断,有独立私有寄存器,延迟更低。

- 中止模式(Abort):处理地址 / 数据访问异常,如非法地址、未对齐访问。

- 未定义模式(Undefined):执行到处理器无法识别的指令时进入。

注意事项

- 除 User 外,其余 6 种均为特权模式,可自由访问系统资源与修改寄存器。

- 模式切换主要由异常、中断、指令触发。

- 只有特权模式拥有 SPSR,用户模式无 SPSR。

- 仅当特权模式满足条件时,user模式才能跳转过来,而其它任意模式随时都可以跳转到user模式。

五、寄存器组概要(重点 CPSR/SPSR)

1. 通用寄存器

R0~R12 为所有模式共用(FIQ 有部分私有寄存器),用于数据搬运、运算暂存、函数传参。

2. 特殊寄存器

- PC(R15):指向当前执行位置的下一条指令,ARM 指令多级流水线会导致 PC 值存在固定偏移。

- LR(R14):保存返回地址,函数返回或中断退出时依赖 LR 恢复执行流。

- SP(R13):每个模式拥有独立 SP,避免不同模式栈空间冲突。

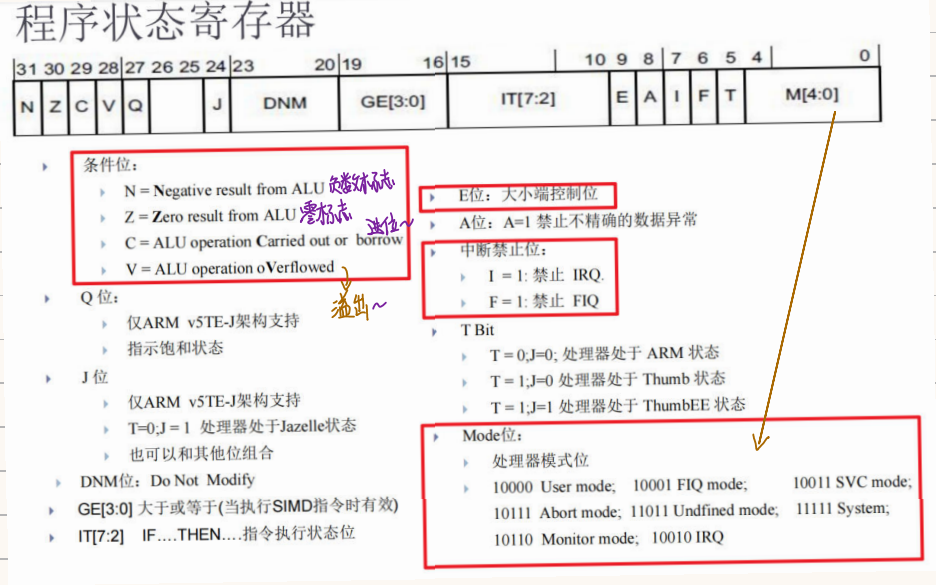

- CPSR(当前程序状态寄存器)

- 条件标志位:N、Z、C、V,反映运算结果。

- 中断禁止位:I、F,分别控制 IRQ、FIQ 使能。

- 模式位:M [4:0],决定处理器当前工作模式。

- **SPSR(备份状态寄存器)**异常发生时硬件自动将 CPSR 存入 SPSR,异常返回时从 SPSR 恢复 CPSR,保证现场不被破坏。

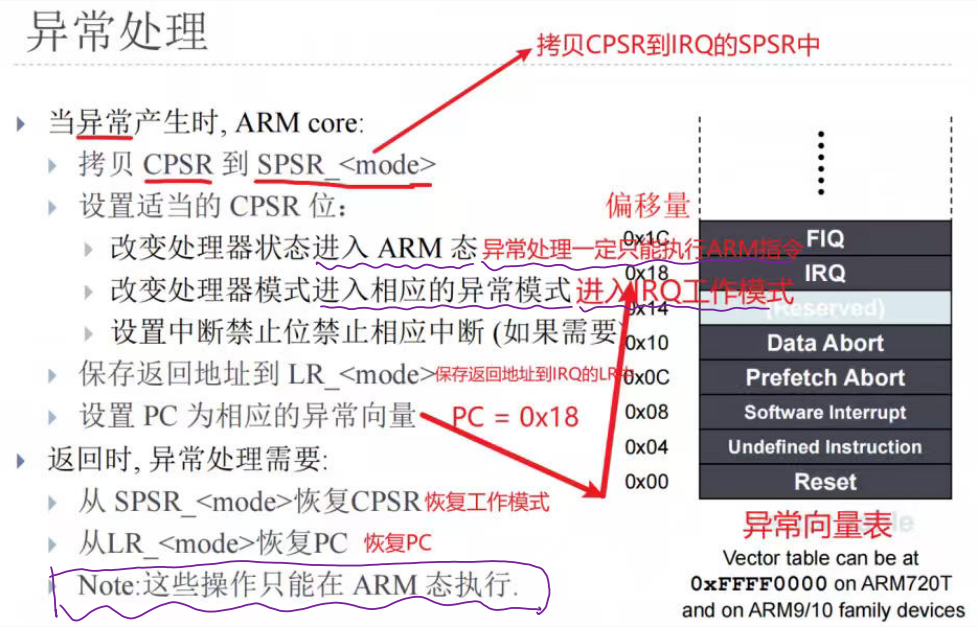

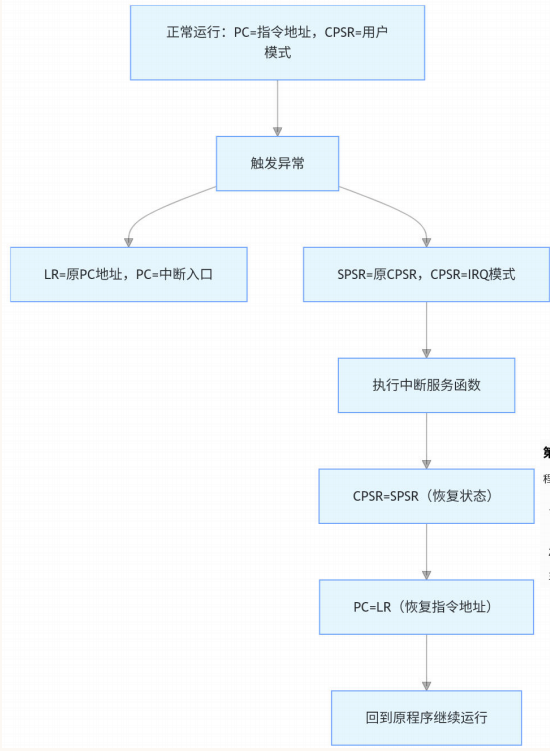

六、异常处理流程(重点)

异常包括中断、指令错误、内存访问错误、软中断等,是处理器响应外部 / 内部事件的核心机制。

完整处理流程

- 异常触发:外部中断、未定义指令、非法内存访问、软中断等事件发生。

- 硬件自动保存现场

- 当前 CPSR → 对应模式的 SPSR

- 下一条指令地址 → 对应模式的 LR

- 自动切换工作模式,进入对应的特权模式。

- 跳转到异常向量表,执行对应异常处理程序。

- 执行异常服务函数,完成中断 / 异常逻辑处理。

- 异常返回恢复现场

- SPSR → CPSR

- LR 修正后 → PC处理器回到异常前位置继续执行。

七、栈结构

1. 栈结构

栈用于保存函数返回地址、局部变量、中断现场,遵循先进后出 FILO。

栈的分类

- 按增长方向

- 增栈:压栈时 SP 向高地址增长

- 减栈:压栈时 SP 向低地址增长(ARM 默认)

- 按指针指向

- 满栈:SP 指向最后一个有效数据

- 空栈:SP 指向下一个可写入位置

ARM 常用组合:减栈 + 满栈

八、多核异构与相关术语

1. 多核异构

一颗 SOC 芯片内集成多种不同架构内核,例如:

- Cortex-A 系列:运行操作系统,负责复杂运算与人机交互。

- Cortex-R/M 系列:负责实时控制、低功耗外设采集。不同核心分工协作,兼顾性能、实时性与功耗。

2. 常见术语

- 架构版本:ARMv7、ARMv8-A/32/64 位

- 指令集:ARM 指令、Thumb 指令

- 制程工艺:nm 越小,功耗越低、集成度越高

- Cache 层级:L1、L2、L3 缓存

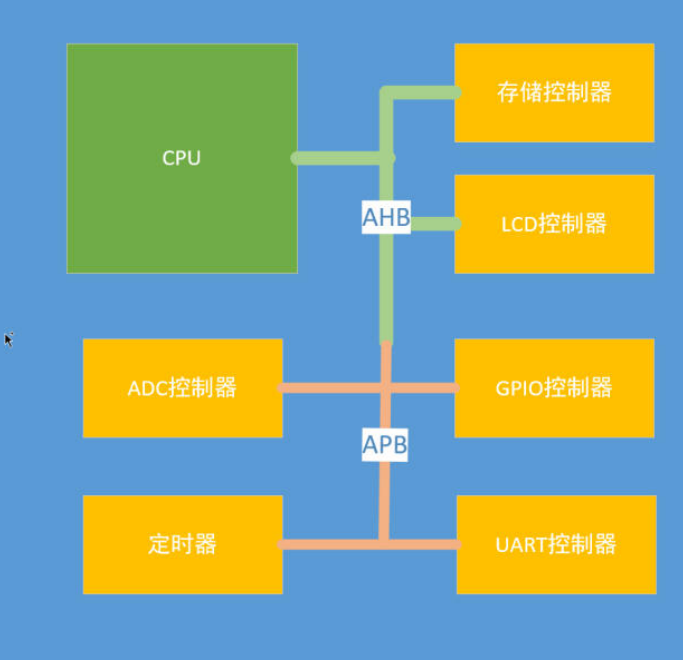

- 总线:AHB、APB 等片上通信总线

学习小结

今日系统学习了 ARM 架构基础:处理器概念、内部核心组件、工作模式、寄存器作用、异常完整流程、存储架构与栈机制,并区分了 CPU/SOC/MCU/MPU 差异。这些内容是后续学习 ARM 汇编、裸机驱动、Linux 移植与内核开发的核心理论基础。