文章目录

- 计算机系统基础61-81 知识点整理。

-

按字节编址时存储容量的区间计算方法 。因为题目说明内存是按字节编址 ,所以每个地址对应 1 个字节 ,某一段地址空间的容量应按"末地址 − 首地址 + 1 "来算,这里的 +1 很重要,因为首地址和末地址对应的存储单元都要计入。题中地址范围为 B3000H 到 DABFFH ,所以容量为

DABFFH − B3000H + 1 = 27C00H字节,把它换算成十进制是 162816B ,再除以1024得 159KB 。这道题蕴含的核心知识点就是:按字节编址时,地址差加 1 就是字节数,再换算成 KB ,因此正确答案是 B(159KB)。 -

Cache 三种地址映射方式的特点及优缺点 。全相联映射 表示主存中的任意一个块都可以放到 Cache 的任意一块中,因此灵活性最高、Cache 空间利用率也最高 ,但代价是地址比较电路复杂、查找成本高;直接相联映射 则规定主存块只能映射到某个满足固定关系的 Cache 块中,结构简单、速度快,但容易发生冲突;组相联映射 介于两者之间,综合了全相联和直接映射的优点。由此可知,A、C、D 的表述都是正确的,而 B 把"全相联映射的缺点"说成了 Cache 空间利用率低 ,这恰好说反了,因为全相联映射的空间利用率并不低,所以不正确的是 B。

-

三种常见 I/O 控制方式的特点比较 。程序查询方式 结构最简单,但 CPU 需要不断轮询外设状态,效率较低,所以 A 错;中断处理方式 下,CPU 不必一直原地等待外设,而是可以先去执行其他程序,等外设准备好后再通过中断通知 CPU 来处理,因此 B 正确 ;DMA 方式 则是在 CPU 初始化之后,由 DMA 控制器直接完成主存和外设之间的数据传输,传送过程中一般不需要 CPU 逐次介入,所以 C 错。同时,DMA 真正开始传送前,必须先向 CPU 或总线仲裁机构申请总线控制权 ,获准后才能占用总线传数据,因此 D 也错。题目蕴含的核心知识点就是:查询方式效率低,中断方式让 CPU 与外设并行工作,DMA 方式进一步减少 CPU 对数据传送过程的参与。

-

Cache 设置的根本作用 。Cache 是位于 CPU 和主存之间 的一种高速缓冲存储器,它并不是用来扩大主存容量,也不是用来增加 CPU 内部通用寄存器数量,而是利用程序访问的局部性原理 ,把 CPU 近期最可能访问的数据和指令暂时放在速度更快的存储器中,从而减少 CPU 等待主存的时间。也就是说,增加 Cache 的主要目的是缓解 CPU 速度快而主存速度相对较慢所造成的速度不匹配问题 ,所以题目蕴含的核心知识点是:Cache 解决的是 CPU 与主存之间的速度矛盾,而不是容量问题 ,正确答案是 A。

-

Cache---主存层次中的平均访问时间计算 。题目先给出主存比 Cache 慢 4 倍 ,且主存存取周期为 200ns ,所以可先求出 Cache 的访问时间为 200 ÷ 4 = 50ns ;再结合 Cache 命中率 H = 0.98 ,表示有 98% 的访问在 Cache 中完成,只有 2% 需要访问主存,因此系统平均访问时间可按"平均时间 = 命中率 × Cache 时间 + 失效率 × 主存时间 "计算,即 0.98 × 50 + 0.02 × 200 = 49 + 4 = 53ns 。这道题蕴含的核心知识点是:分级存储系统的平均访问时间由各层访问时间和命中率共同决定,命中率越高,平均访问时间越接近 Cache 的速度 ,所以正确答案是 B(53ns)。

-

软件可靠性的定义及其影响因素 。软件可靠性通常是指:软件在规定的条件 和规定的时间 内,不引起系统失效、能够正确完成规定功能的能力,因此 A 的表述基本正确;其中"规定的条件"确实包括软硬件运行环境以及软件的使用方式,B 也是对的;"规定的时间"可以体现在日历时间、运行时间、执行次数等角度,C 也符合可靠性分析的常见表述。错误的是 D ,因为软件可靠性不仅与软件缺陷 和输入情况 有关,还与系统的使用方式、运行环境、操作条件 密切相关,不可能"与系统的使用无关"。这道题蕴含的核心知识点是:软件可靠性是一个与缺陷、输入、环境和使用条件共同相关的综合概念 ,所以错误项是 D。

-

计算机性能评价指标与可靠性指标的基本含义 。常见的综合性能评价确实可以从工作量类、响应时间类、利用率类 等方面衡量,A 正确;除纯性能外,系统评价还常关注可靠性、可用性、可维护性 等质量指标,B 也正确;benchmark(基准程序)也是常用的性能测试方法,D 正确。错误的是 C ,因为 MTBF(平均故障间隔时间)越大,说明系统两次故障之间平均能稳定运行更久,系统才越可靠 ;题目把它说成"越小越可靠"正好说反了。这个题目蕴含的核心知识点是:性能指标和可靠性指标都属于系统评价内容,而可靠性中 MTBF 是越大越好,不是越小越好 ,所以答案是 C。

-

DMA(直接存储器访问)与其他 I/O 传送方式在"传送单位"上的区别 。DMA 的核心特点是:在 CPU 只进行初始化和结束处理的情况下,由 DMA 控制器 直接完成外设和主存之间的大批量数据传送,因此它最适合处理成批、连续 的数据交换。也正因为如此,DMA 方式通常不是按"位""字节"或"单个字"去组织整个传送任务,而是以数据块为单位 进行传送;相比之下,程序查询和中断方式更常体现为 CPU 对较小单位数据的逐次处理。题目蕴含的关键知识点就是:DMA 的优势在于块传送,适合高速、大批量 I/O ,所以正确答案是 C(数据块)。

-

程序计数器(PC)的作用 。CPU 在执行指令时,必须始终知道"下一条要到哪里去取指",因此需要有一个寄存器专门保存将要执行的下一条指令地址 ,这个寄存器就是 程序计数器 PC 。在顺序执行程序时,CPU 每取完一条指令后会自动修改 PC 的内容,使它指向下一条指令;如果遇到转移、调用、中断等情况,PC 也会被改成新的目标地址。相比之下,指令寄存器 保存的是当前指令内容,地址寄存器 主要用于暂存访存地址,指令译码器 负责分析指令含义,都不承担"始终指向下一条指令地址"的功能。因此题目蕴含的核心知识点是:PC 是控制程序执行顺序的关键寄存器,CPU 会自动更新它 ,所以正确答案是 B(程序计数器)。

-

n 位补码(含 1 位符号位)的表示范围 。采用 n 位补码表示整数时,最高位既表示符号又参与数值运算,因此它能表示的范围是 -2^(n-1) 到 2^(n-1)-1 :也就是说,最大的正数是

2^(n-1)-1,而最小的负数可以达到 -2^(n-1) 。这正是补码的一个重要特点------负数范围比正数多 1 个值 ,因为补码中没有单独的 "-0"。所以题目中"可以直接表示"的这个特殊数值就是 -2^(n-1) ,对应 D。 -

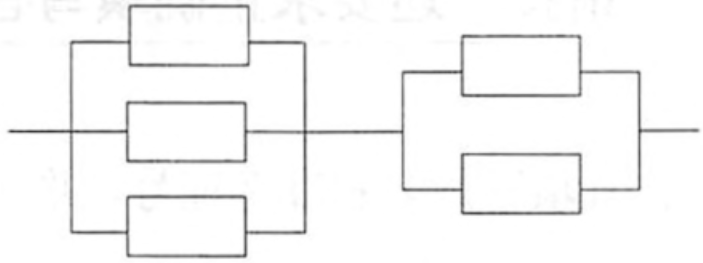

串联系统与并联系统可靠度的组合计算 。图中左边一组由 3 个部件并联 构成,右边一组由 2 个部件并联 构成,而这两组之间又是串联关系 。对于并联系统,只要其中至少有一个部件正常 ,该组就能工作,所以 3 个部件并联的可靠度为1-(1-R)^3,2 个部件并联的可靠度为1-(1-R)^2;而串联系统要求前后各部分都正常 系统才能正常工作,因此总可靠度等于两部分可靠度相乘,即[1-(1-R)^3][1-(1-R)^2]。这道题的关键知识点就是:并联用"1 减去全失效概率",串联用各部分可靠度相乘 ,所以正确答案是 C。 -

一位奇偶校验的检错能力和局限性 。一位奇偶校验的基本思想是:在原始数据后面附加 1 位校验位 ,使整个码字中"1"的个数保持奇数或偶数,从而在传输后通过重新统计"1"的个数来判断是否出错。它的特点是:当数据中有奇数个位出错时,校验结果会发生变化,因此可以检测出错误;但它只能检错,不能指出哪一位错了,所以无法纠错 ;而如果有偶数个位同时出错,奇偶性可能不变,就可能检测不出来 。因此题目中正确的表述是 C:若有奇数个数据位出错,则可以检测出该错误但无法纠正错误。

-

流水线执行方式提升的到底是什么性能指标 。流水线把一条指令分成若干阶段,让多条指令在不同阶段重叠执行 ,因此它的主要作用是提高系统吞吐率 、让单位时间内完成更多指令,同时也能提高各功能部件的利用率,所以 B、C、D 都是正确的;但流水线并不会缩短单条指令从开始到结束所经历的总过程 ,单条指令的执行时间通常并没有因此变短,甚至还可能因为流水寄存器、冒险处理等带来额外开销。因此题目中不正确的是 A ,核心知识点就是:流水线提高的是整体并行度和吞吐率,而不是单条指令的执行速度。

-

布尔表达式中的短路求值规则 。短路求值的核心思想是:一旦根据前面部分的结果就已经能够确定整个表达式的真值,后面的部分就不再计算。题中表达式是

a or ((c < d) and b),对于 or 运算来说,只要左边已经为 true ,整个表达式就一定为 true ,右边无论是什么都不用再算,因此当 a 为 true 时就可以发生短路计算。其余选项中,单独知道 b、c、d 的真假并不能直接确定整个表达式的值,因为右侧还涉及比较结果和与运算。题目蕴含的关键知识点就是:or 运算遇真即止,and 运算遇假即止 ,所以本题正确答案是 B(a 为 true)。 -

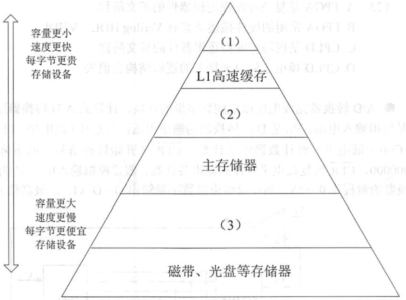

分层存储器结构中各层的位置关系及其特征 。分层存储体系从上到下遵循一个基本规律:越靠上,容量越小、速度越快、每字节成本越高;越靠下,容量越大、速度越慢、每字节成本越低 。因此在最顶层、比 L1 高速缓存 还快的一层应当是 寄存器 ,因为寄存器离 CPU 最近、速度最快;位于 L1 高速缓存 和主存储器 之间的通常是 L2 高速缓存 ;而在主存储器之下、磁带光盘等更慢的离线或近线存储之上的,则应是常见的磁盘存储器 。所以图中的 (1)、(2)、(3) 分别应为 寄存器、L2 高速缓存、磁盘存储器 ,对应 A。 -

组相联映射下主存地址位数 。先看主存地址位数:主存共有 4096 块 = 2¹² 块 ,每块 128 字节 = 2⁷B ,又因为是按字节编址 ,所以主存总容量为

2¹² × 2⁷ = 2¹⁹B,因此主存地址需要 19 位 ,所以第 76 题选 B。 -

"主存区号"位数的计算方法 。Cache 有 64 块 ,题目按这类教材中"主存区号 "的定义,是把主存按整个 Cache 容量 来划分区,每区含 64 块 ,所以主存可分成

4096 ÷ 64 = 64 = 2⁶个区,因此主存区号为 6 位 ,第 77 题选 C 。这道题的关键知识点就是:主存地址位数 = log₂(主存总字节数) ,而这类题里的主存区号通常按"主存按 Cache 总块数分区"来算。 -

总线带宽的计算方法 。总线带宽表示单位时间内总线能够传送的数据量,关键要分清时钟周期 和总线周期 不是一回事:题中总线时钟频率为 100MHz ,表示每秒有

100 × 10^6个时钟周期;但一个总线周期要占 2 个时钟周期 ,所以每秒真正能完成的总线周期数是100MHz ÷ 2 = 50MHz。又因为每个总线周期可并行传输 4 字节 ,所以总线带宽为50 × 10^6 × 4 = 200 × 10^6 B/s,即 200MB/s 。这道题蕴含的核心知识点就是:总线带宽 = 每个总线周期传输的数据量 × 每秒总线周期数 ,因此正确答案是 B。 -

I/O 数据传送方式中 CPU 参与程度的区别 。在程序查询方式 下,CPU 要不断查询设备状态并亲自完成数据传送;在中断方式 下,虽然设备准备好后会通知 CPU,但真正的数据读写仍需要 CPU 参与;而 DMA(直接存储器访问)方式 的特点是由 DMA 控制器 直接控制 I/O 设备与主存 之间的数据交换,数据传送过程不需要 CPU 逐次干预 ,CPU 只在开始前进行初始化、结束后进行处理。因此题目中"I/O 设备与存储设备进行数据交换不经过 CPU 来完成 "描述的正是 DMA 方式 ,所以正确答案是 C。

-

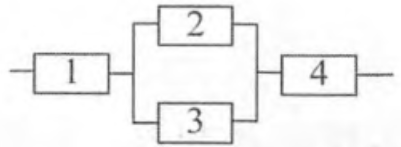

串联系统与并联系统(冗余系统)可靠度的组合计算 。图中部件 1、(2 与 3)、4 是串联关系 ,因此系统总可靠度等于各部分可靠度相乘;而部件 2 和 3 是冗余结构,属于并联关系 ,其合成可靠度应按"1 减去同时失效的概率 "来算,即1-(1-0.8)^2=0.96。于是整个系统的可靠度为0.9 × 0.96 × R4,题目要求系统可靠度不小于 0.85 ,所以应满足0.9 × 0.96 × R4 ≥ 0.85,解得R4 ≥ 0.85 / [0.9 × (1-(1-0.8)^2)] ≈ 0.984。因此这道题的核心知识点就是:串联取乘积,并联冗余用"1 减全失效概率" ,所以部件 4 的可靠度至少应满足选项 A 所对应的式子。 -

多级 Cache 设置的主要作用 。Cache 是位于 CPU 和主存之间的高速缓冲存储器,设置 L1、L2、L3 等多级 Cache 的目的,不是扩大主存或整个存储系统的容量,也不是提高访问外存的速度,而是利用程序访问的时间局部性和空间局部性 ,把 CPU 近期最可能用到的指令和数据提前保存在更快的存储层中,从而减少 CPU 访问主存的等待时间,提高取指和取数效率。所以题目蕴含的核心知识点是:多级 Cache 的本质是进一步缓解 CPU 与主存之间的速度差异,提高 CPU 访问主存数据或指令的效率 ,因此正确答案是 B。