4.8.3 Spectrum-Based ATPG

和基于逻辑仿真的ATPG相似,基于图谱的ATPG也是希望在fault-free电路中找到电路的特性从而帮助测试生成,但是不同的是,基于图谱的ATPG将时序逻辑电路视为一个黑盒子,这个黑盒子可以从它的输入输出识别和预测。

基于图谱的测试生成流程:

- test set里面是随机的测试向量

- 静态压缩滤除一些没必要的向量

- 用Hadamard transform方法做frequency decomposition

- 基于以上动作,生成测试向量

- 以basis vectors为基础,重复这个过程直到达到想要的故障覆盖率或者迭代次数到达上限

基于图谱的ATPG对于大多数的时序逻辑电路而言,能实现非常高的故障覆盖率,而且test set很小,而且执行速度还很快。

4.9 HYBRID DETERMINISTIC AND SIMULATION-BASED ATPG(两类ATPG方法融合)

两种ATPG方法的区别:

- deterministic ATPGs:适合用于control-dominant的电路

- simulation-based ATPGs:适合用于data-dominant的电路

一种很简单的两种方法结合的方式就是,先快速跑一遍simulation-based test generator(把好测的故障都从故障列表里面剔除),剩下难测的故障用deterministic test generator去提升故障覆盖率,比如CRIS-hybrid test generator用的就是这种方法。

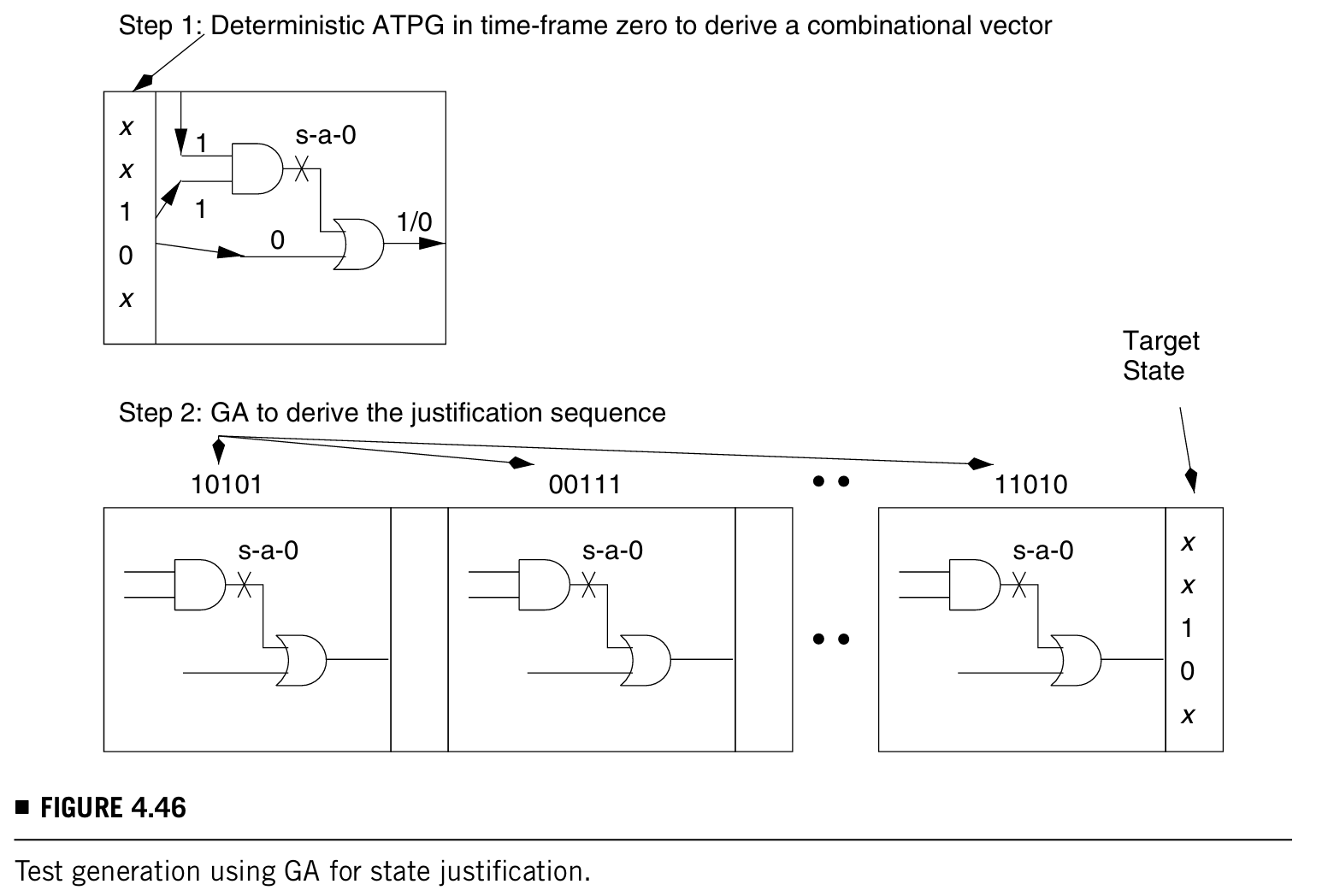

还有一种方法是GA--HITEC hybrid test generator,流程是:

- deterministic algorithms:for fault excitation and propagation

- GA:for state justification

- 如果上一步GA不成功,就用Deterministic procedures:for state justification

下图就分别展示了用Deterministic ATPG和GA完成测试向量生成的过程:

对于很多电路,GA-HITEC的故障覆盖率比单纯的deterministic HITEC更高。

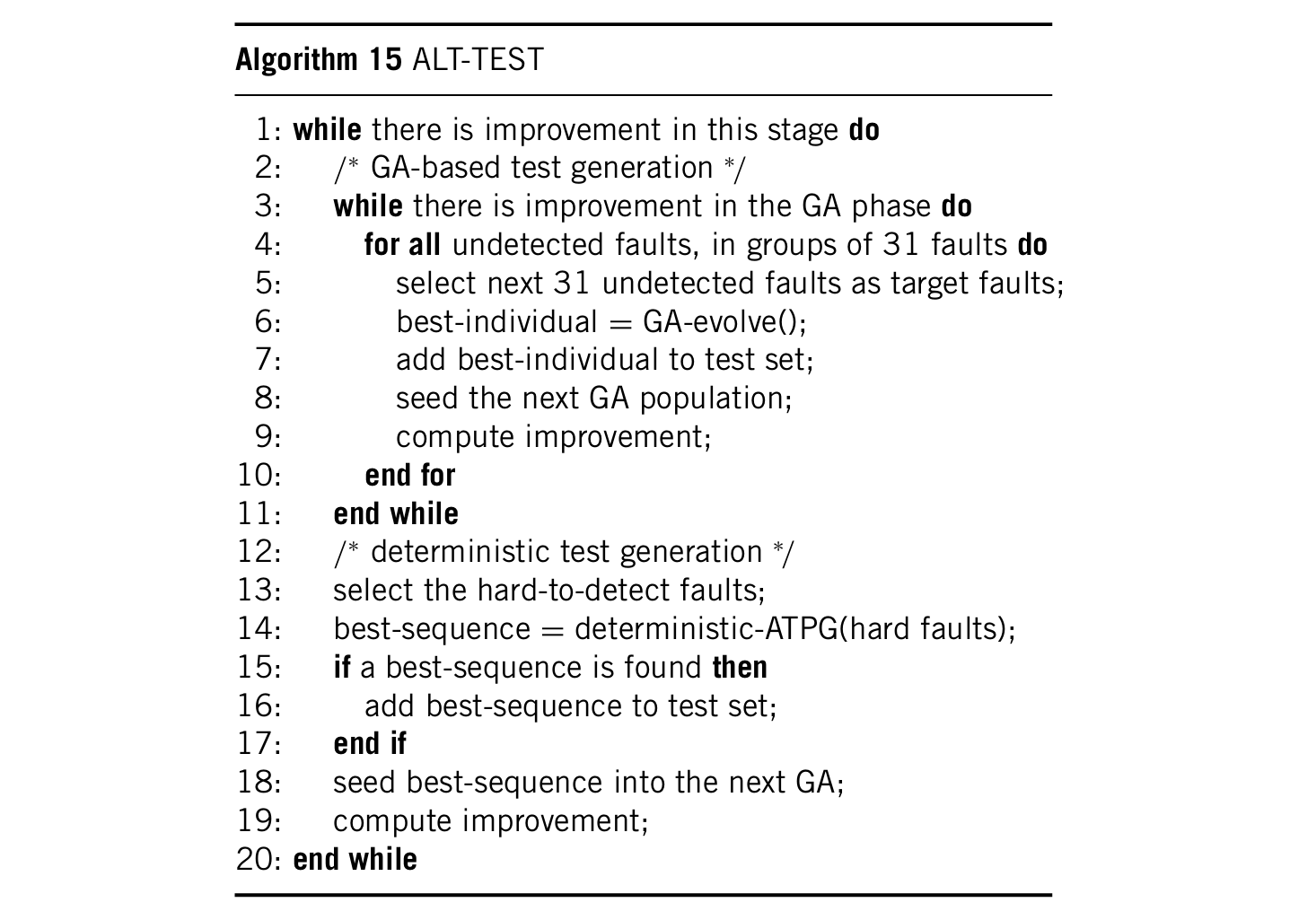

4.9.1 ALT-TEST Hybrid

ALT-TEST也是结合了GA-based test generator和deterministic engine,同样的,里面的deterministic test generator用的也是HITEC,但是和CRIS hybrid不同的是,ALT-TEST很少调用到deterministic test generator,只不过在执行的过程中不断地在GA-based和deterministic test generation之间切换。

在这个方法中deterministic test generator的作用有两个:

- 和上一个方法一样,就是测试一些难以检测到的故障

- 可以引导GA算法,开发更多电路状态,使GA在下一轮能检测到更多故障(主要是这个功能)

所以ALT-TEST测试生成的过程有3个阶段:

- GA先跑,尽可能多地发现fault list中的故障,直到没有或者很少的故障再被发现

- 然后用deterministic approach,针对undetected faults,最大化电路的visited states数量并且propagate fault effects to flip-flops

- 检测现有的故障并且访问新的电路states

以上流程的算法见下图算法15:

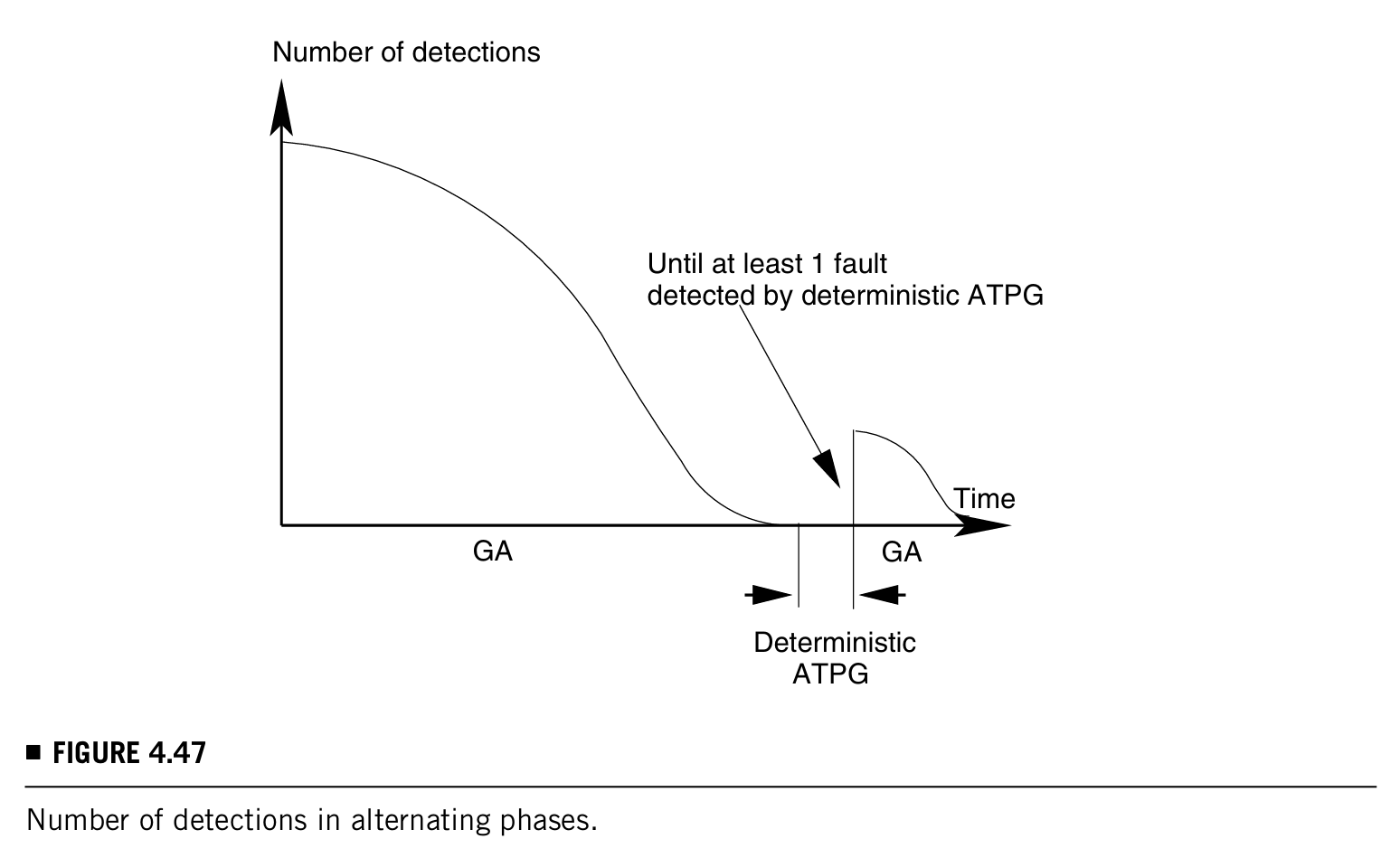

因为GA和deterministic phases不断切换,所以检测到的故障数量随着时间会经历周期性的跳跃,如下图:

ALT-TEST的3个阶段的fitness functions取决于下面的参数:

- P1 --- Number of faults detected

- P2 --- Number of flip-flops to which fault effects have arrived

- P3 --- Number of new states visited

- P4 --- Number of flip-flops set to their difficult-to-control values

三阶段带着不同的权重可以计算fitness:

- Stage 1---Fitness = 0.8P1 +0.1P2 +0.1(P3 +P4 )

- Stage 2---Fitness = 0.1P1 +0.45P2 +0.45(P3 +P4 )

- Stage 3---Fitness = 0.4P1 +0.2P2 +0.4(P3 +P4 )

对于许多电路,ALT-TEST能达到比GA-HITEC更高的故障覆盖率。