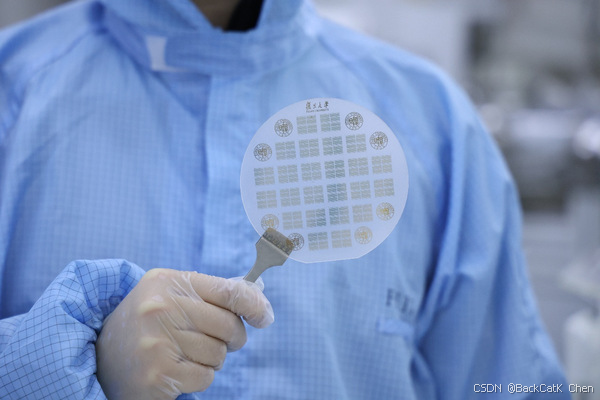

近日,复旦大学周鹏、包文中团队在《Nature》主刊发表重磅研究成果------全球首款基于二维半导体的32位RISC-V处理器"无极(WUJI)"正式问世。这款芯片的诞生,不仅打破了二维材料集成度的国际纪录,更标志着中国在芯片底层技术领域实现从"跟跑"到"领跑"的跨越,为后摩尔时代中国芯片摆脱设备封锁、实现自主可控提供了全新路径。

作为技术开发者,我们更关注这款芯片的核心技术细节、底层实现逻辑,以及它对半导体产业、开发者生态的实际影响。本文将从技术原理、核心参数、突破意义、落地前景四个维度,深度拆解无极芯片,帮大家理清这款"国产黑科技"的核心价值与技术亮点。

一、背景:硅基芯片的瓶颈与二维半导体的破局之路

在聊无极芯片之前,首先要明确一个核心前提:当前硅基芯片已逼近物理极限,摩尔定律逐渐失效,而EUV光刻机的技术封锁,进一步加剧了高端芯片的研发困境。

硅基芯片的核心瓶颈主要体现在三点:

-

量子隧穿效应凸显:当晶体管制程缩小至3nm及以下,电子会突破栅极束缚发生"隧穿",导致漏电率飙升、功耗失控,这是硅材料本身的物理特性,无法通过工艺优化彻底解决;

-

制程成本呈指数级增长:EUV光刻机单台造价超2亿美元,且被ASML垄断,国内企业难以获得,即便能突破制程,也面临设备卡脖子的问题;

-

集成度天花板显现:硅基晶体管的最小尺寸已接近原子级别,继续缩小制程的难度极大,集成度提升空间有限。

而二维半导体材料(如二硫化钼MoS₂)的出现,恰好破解了这一困境。与传统硅材料相比,二维材料具有原子级厚度、超高载流子迁移率、良好的柔性等优势,能够从根源上解决硅基芯片的漏电、发热问题,同时无需依赖EUV光刻机,成为后摩尔时代的核心技术方向。

此前,国际上二维半导体的最高集成度仅为115个晶体管,无法实现完整的处理器功能,而无极芯片的诞生,直接将这一纪录提升至5900个,实现了从"实验室样品"到"功能性处理器"的跨越。

二、无极芯片核心技术解析(开发者重点关注)

无极芯片的核心突破,在于"二维材料集成工艺+自主架构设计"的双重创新,以下从材料、集成度、架构、工艺四个核心维度,拆解其技术细节:

1. 核心材料:单层二硫化钼(MoS₂)的优势

无极芯片采用单层二硫化钼作为晶体管的沟道材料,厚度仅0.7nm(单原子层),这也是其突破硅基极限的核心基础。

与硅材料相比,二硫化钼的核心优势的体现在:

-

载流子迁移率更高:在室温下,二硫化钼的载流子迁移率可达1000 cm²/(V·s),远超硅材料(约600 cm²/(V·s)),意味着电子传输速度更快,芯片性能更强;

-

完美抑制短沟道效应:原子级厚度的沟道的能够有效束缚电子,避免量子隧穿,漏电率较硅基芯片降低90%以上,待机功耗大幅下降;

-

材料自主可控:二硫化钼在我国储量丰富,且国内已实现自主制备,无需依赖进口,从源头解决了材料卡脖子问题。

2. 集成度突破:5900个晶体管的实现逻辑

此前,二维半导体集成度难以提升的核心难点,在于二维材料的转移、接触、封装等工艺瓶颈------二维材料质地脆弱,转移过程中易破损、褶皱,且与金属电极的接触电阻过大,影响晶体管性能。

复旦团队通过两项关键技术,解决了这一难题:

(1) 原子级精准转移技术:采用"范德华外延转移"工艺,将单层二硫化钼精准转移至衬底上,避免材料破损,转移精度达到原子级别;

(2) 低接触电阻工艺:设计新型金属电极结构,降低二硫化钼与电极的接触电阻,提升晶体管的开关速度和驱动能力。

最终,无极芯片实现了5900个二维晶体管的集成,是此前国际最高纪录(115个)的51倍,能够完整实现32位运算、10亿条指令执行、GB级存储等微处理器核心功能,真正具备了实用价值。

3. 架构设计:RISC-V开源架构,自主无专利枷锁

无极芯片采用RISC-V开源指令集,设计了32位RISC-V处理器架构,这一选择既兼顾了性能,又实现了架构层面的自主可控。

相较于ARM、X86架构,RISC-V的核心优势在于:

-

开源免费:无需支付高额专利费,开发者可自由修改、优化架构,适配自身需求;

-

精简高效:指令集简洁,功耗更低,适合物联网、边缘计算、可穿戴设备等低功耗场景;

-

自主可控:摆脱对国外架构的依赖,结合国产二维材料和工艺,实现从架构到硬件的全链条自主。

从实际测试数据来看,无极芯片的指令执行效率达到1.2 DMIPS/MHz,与主流硅基RISC-V处理器相当,但功耗仅为其1/10,展现出极强的竞争力。

4. 制造工艺:无需EUV,兼容现有产线

这是无极芯片最具产业价值的突破------无需依赖EUV光刻机,采用现有硅基产线改造即可实现量产,大幅降低了产业化门槛。

其核心工艺路径为:采用柔性等离子刻蚀技术,结合AI算法优化工艺参数,在90nm硅基产线上,实现了等效3nm硅基芯片的性能。具体来说,70%的工序可直接复用现有硅基产线,仅需对刻蚀、封装等少数工序进行改造,改造成本远低于新建EUV产线。

这意味着,中芯国际、华虹等国内芯片制造企业,无需引入EUV光刻机,即可量产无极芯片相关产品,彻底绕开了设备封锁的困境。

三、对开发者与产业的实际影响

无极芯片的诞生,不仅是一项技术突破,更对半导体产业、开发者生态产生深远影响,尤其对国内开发者而言,带来了全新的机遇:

1. 开发者生态:开源架构+自主工艺,降低研发门槛

基于RISC-V开源架构,开发者可自由基于无极芯片的技术路线,开发适配物联网、边缘计算、航天电子等场景的应用程序和定制化芯片。同时,二维半导体的相关工艺技术(如材料转移、电极设计)将逐步开源,国内开发者可快速掌握核心技术,无需再依赖国外技术垄断。

此外,复旦团队已申请20余项发明专利,后续有望通过技术授权的方式,向企业和开发者开放,推动二维芯片相关技术的快速普及。

2. 产业落地:多场景适配,国产芯片迎来新赛道

无极芯片的性能和功耗优势,使其非常适合低功耗、高性能的场景,具体包括:

-

物联网设备:智能手表、传感器、无人机等,低功耗特性可大幅提升设备续航;

-

边缘计算:边缘服务器、工业控制设备,高性能+低功耗可降低运维成本;

-

航天电子:航天器上的核心芯片,高可靠性、抗辐射特性可适配太空环境;

-

AI边缘设备:小型AI终端、智能摄像头,可实现高效的本地计算,降低对云端的依赖。

目前,无极芯片已完成实验室验证,下一步将进入中试阶段,预计1-2年内可实现小规模量产,届时将为国内开发者提供全新的芯片选择。

3. 行业意义:后摩尔时代,中国掌握话语权

此前,全球半导体产业的发展路线,一直由欧美、日韩主导,硅基芯片的规则制定权掌握在国外企业手中。而无极芯片的诞生,标志着中国在二维半导体领域实现了"换道超车"------我们没有在硅基路线上继续追赶,而是直接布局下一代芯片技术,掌握了后摩尔时代的核心话语权。

对国内半导体产业而言,无极芯片的技术路线,将推动材料、设备、设计等全产业链的自主升级,逐步摆脱对国外设备和技术的依赖,实现芯片产业的全面自主可控。

四、总结与展望

无极芯片的诞生,是中国芯片产业从"跟跑"到"领跑"的重要里程碑,它的核心价值,不仅在于打破了二维半导体的集成度纪录,更在于提供了一条"无需EUV、全链自主、低成本量产"的全新路线,为后摩尔时代中国芯片的发展指明了方向。

对于开发者而言,二维半导体将成为未来几年的核心技术热点,掌握相关技术(如二维材料制备、RISC-V架构优化、集成工艺),将成为自身的核心竞争力。后续,随着无极芯片的产业化推进,相关的开发工具、技术文档、开源项目也将逐步完善,为开发者提供更多的实践机会。

当然,我们也需要清醒地认识到,无极芯片目前仍处于实验室向中试过渡的阶段,距离大规模量产、替代硅基芯片还有一段距离,后续还需要解决材料稳定性、封装工艺优化、成本控制等一系列问题。但不可否认的是,中国芯片已经在底层技术领域实现了重大突破,未来可期。