PCIe虚拟化是现代云计算基础设施的核心支撑技术。传统虚拟化中,Hypervisor(VMM)以软件模拟方式让虚拟机访问物理设备------每一次I/O操作都经过虚拟化软件层层转接,性能损耗高达30~50%。SR-IOV(Single Root I/O Virtualization)从根本上改变了这一范式:它允许单一物理设备在硬件层面分立为多个虚拟功能(Virtual Function),每个VF可被直接分配给虚拟机,实现接近原生硬件的性能。

本文结合业界最新实践,系统深入讲解PCIe虚拟化的完整技术栈:从SR-IOV的硬件架构与PF/VF协作模型,到IOMMU地址虚拟化(ATS/PASID/PRI),再到Linux VFIO用户态驱动框架与QEMU透传机制,最后剖析NFV/云场景下的实际应用与演进方向。

────────────────────────────────────────────────────────────

1. 传统虚拟化的性能困境

理解PCIe虚拟化,首先要理解传统虚拟化I/O路径的瓶颈在哪里。

1.1 软件模拟路径的性能损耗

传统Virtio/EMUL通道下,虚拟机I/O的数据路径是:

VM用户态进程

↓ (系统调用)

VM内核驱动(virtio-net)

↓ (Virtqueue共享内存)

Hypervisor / VMM(QEMU/KVM)

↓ (模拟寄存器访问)

物理网卡驱动

↓ (DMA描述符)

物理网卡

这条路径上,每一次MMIO(Memory-Mapped I/O)访问都需要陷入Hypervisor,由软件模拟执行。以10Gbps网络为例,每秒约150万个数据包,每个数据包都需要:

- VM Exit(虚拟机退出):从Guest模式切换到Host模式,~1000~5000 CPU周期

- Hypervisor模拟:MMIO读写模拟,~500~2000 CPU周期

- 上下文切换:内核态/用户态切换,~500 CPU周期

累计开销:每秒数百万CPU周期消耗在虚拟化软件上,真正用于数据处理的有效算力大打折扣。

1.2 虚拟化I/O的三种形态

|-------------------|--------|---------|---------|------------------|

| 虚拟化方式 | 性能 | 灵活性 | 迁移性 | 代表技术 |

| 软件模拟 | 低 | 高 | 好 | Virtio、e1000虚拟网卡 |

| 设备透传(Passthrough) | 极高 | 低 | 差 | VFIO直接分配 |

| 硬件虚拟化(SR-IOV) | 极高 | 中 | 较好 | SR-IOV VF分配 |

────────────────────────────────────────────────────────────

2. SR-IOV硬件架构:PF与VF的协作模型

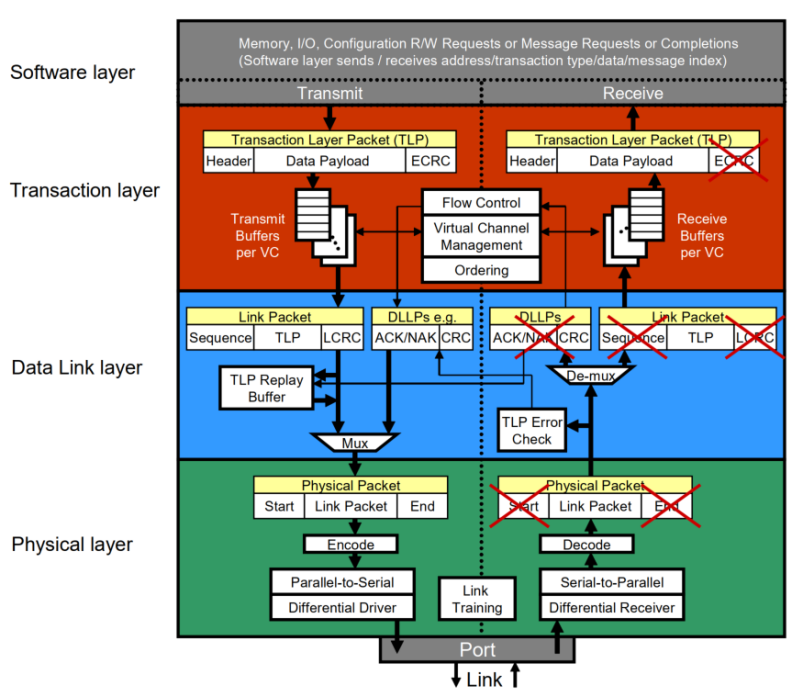

图:pcie-layer-overview.PNG

2.1 核心概念:PF与VF

SR-IOV在PCIe规范中定义了两种功能实体:

|--------|-------------------|------------|--------------|----------------------|

| 实体 | 全称 | 数量 | 配置空间 | 职责 |

| PF | Physical Function | 每设备1个 | 完整4KB Type0 | 管理控制:创建/销毁VF、配置设备能力 |

| VF | Virtual Function | 每设备1~256个 | 简化256B Type0 | 数据平面:直接分配给VM,承载I/O流量 |

PF是设备的"管理员":它拥有完整的PCIe配置空间,可以配置设备的任何功能,包括创建多少个VF。VF是"租户":轻量级、独立可枚举,但能力受限(只能访问自己被分配的资源)。

关键理解:PF和VF共享同一个物理硬件资源------同一块网卡芯片、同一组TX/RX队列硬件------但通过硬件隔离确保各VF之间互不干扰。

2.2 SR-IOV Extended Capability

SR-IOV能力结构位于PCIe配置空间扩展区(Capability ID = 0x10),包含以下核心寄存器:

|-------------|---------------------------------|-----------------------------------------------------------|

| 寄存器(偏移) | 名称 | 说明 |

| 0x00 | SR-IOV Capability ID | 固定值 0x10,标识SR-IOV能力 |

| 0x02 | SR-IOV Capability | VF Migration State、Bridge Model等 |

| 0x04 | SR-IOV Control | VF Enable(bit0):使能VF; VF MSE(bit1):VF Memory Space Enable |

| 0x06 | SR-IOV Status | RO字段,指示VF是否已使能 |

| 0x08 | Initial VFs | RO字段,设备出厂时支持的VF数量上限 |

| 0x0C | Total VFs | RO字段,设备固件/驱动支持的最大VF数量 |

| 0x10 | NumVFs | RW字段,软件配置的VF启用数量 |

| 0x12 | First VF Offset | 第一个VF相对于PF的Routing ID偏移量 |

| 0x14 | VF Stride | 相邻两个VF之间的Routing ID间隔 |

| 0x16 | VF Device ID | RO字段,VF的Device ID(区分于PF的Device ID) |

| 0x18 | Supported Page Size | RO字段,VF支持的页大小掩码 |

| 0x1C~0x38 | VF BAR0~BAR5 | RW字段,VF的基地址寄存器(分配VF地址空间) |

| 0x3C | VF Migration State Array Offset | 可选,用于VF Live Migration |

2.3 VF的BDF号计算与枚举

VF被分配独立的BDF(Bus/Device/Function)号,可被系统当作独立PCIe设备枚举。计算公式:

VF[i]_Bus = PF_Bus

VF[i]_Device = PF_Device + (FirstVFOffset + i * VFStride) >> 3

VF[i]_Function = (FirstVFOffset + i * VFStride) & 0x07

实际示例(Intel X710网卡):

PF BDF = 0000:3B:00.0

FirstVFOffset = 0x10

VFStride = 0x01

NumVFs = 63

VF[0] BDF = 0000:3B:10.0

VF[1] BDF = 0000:3B:10.1

VF[63] BDF = 0000:3B:4F.0

2.4 VF的地址空间分配

VF BAR(Base Address Register)的分配流程是SR-IOV配置中最精细的环节:

- PF驱动读取Total VFs和Supported Page Size,了解硬件能力

- PF驱动计算每个VF需要的地址空间大小(对齐到页面边界)

- 向NumVFs写入目标数量,启用VF

- 系统枚举所有VF,为每个VF BAR分配物理地址

- VF BAR的分配必须在PF BAR之后完成(资源嵌套关系)

- VF BAR与PF BAR共享设备的物理地址解码器(硬件约束)

──────────────────────────────────────────────────────────────────────

3. 地址虚拟化:让设备正确访问虚拟机内存

3.1 IOMMU:设备端地址翻译

在虚拟化环境中,虚拟机运行在虚拟地址空间(GVA/GPA),而设备DMA必须访问真实的物理地址(HPA)。IOMMU(Input/Output Memory Management Unit,VT-d或AMD-Vi)就是这个桥梁:

|------------|--------------------------|--------------|

| 组件 | 作用 | 位置 |

| MMU(CPU侧) | CPU虚拟地址 → 物理地址 | CPU芯片内 |

| IOMMU(设备侧) | 设备虚拟地址(IOVA) → 物理地址(HPA) | 北桥/芯片组或CPU集成 |

| IOVA | 设备视角的虚拟地址 | 设备驱动配置 |

IOMMU的核心价值:

- 地址翻译:让设备访问GPA映射的HPA,而不是任意物理内存(安全隔离)

- DMA保护:限制设备只能访问授权的内存区域,防止恶意设备越界访问

- 34-bit IOVA空间(x86):设备可以使用超过4GB的地址访问系统内存

- 直接操作:无需将数据先映射到低区再DMA(减少内存拷贝)

3.2 ATS:设备本地地址转换缓存

IOMMU每次都查询页表会引入延迟(~100ns/次)。ATS(Address Translation Service)让设备在本地缓存地址转换结果,类似CPU的TLB:

ATS工作流程(带缓存):

- 设备发起DMA,携带IOVA(设备本地虚拟地址)

- 设备先查本地ATC(Address Translation Cache):

- Cache Hit → 直接使用翻译后的HPA发起DMA

- Cache Miss → 继续下一步

- 设备向IOMMU发送ATS Translation Request

(携带IOVA + PASID) - IOMMU查询页表,返回翻译结果:

- Translated Address(HPA)

- S/D Bit(Translated/Dirty,用于追踪脏页)

- Page Size

- 设备缓存翻译结果到ATC

- 设备使用HPA完成DMA

当OS修改页表时,IOMMU发送ATS Invalidation Request,

设备收到后清除对应ATC条目,确保缓存一致性。

3.3 PASID:进程级地址空间标识

在多任务系统中,多个进程共享同一设备,设备需要区分"谁的内存"。PASID(Process Address Space ID)通过TLP Prefix携带进程标识:

PASID TLP Prefix格式(1 DW = 4 Bytes):

Byte 0: 0x02 (Prefix Type = PASID)

Byte 1: Flags

- bit 0: Execute Requested (ER)

- bit 1: Privilege Mode Requested (PMR)

Byte 2-3: PASID[19:0](20位进程标识,支持最多100万个并发进程)

工作模式:

- No PASID (PASID=0): 设备访问系统级地址空间

- PASID!=0: 设备访问特定进程的虚拟地址空间

- 执行权限由Flags中的ER和PMR位控制

PASID使能SVM(Shared Virtual Memory):CPU和设备共享同一套虚拟地址空间,设备代码可以直接用指针访问进程内存,无需固定地址或手动拷贝------这对GPU统一内存和AI加速器至关重要。

3.4 PRI:缺页处理机制

ATS要求被访问的页面已映射。但SVM场景下,设备可能访问尚未分配的内存(按需分配)。PRI(Page Request Interface)让设备主动请求OS分配页面:

PRI工作流程:

- 设备访问某IOVA,ATS Miss(页面未映射)

- 设备发送Page Request Message(携带PASID + IOVA + 请求类型)

- IOMMU接收请求,触发OS缺页中断

- OS内存管理:分配物理页,更新IOMMU页表

- OS返回Page Response Message(Success/Failure)

- 设备收到Success → 重新发起ATS Translation → 完成DMA

注意:PRI需要OS主动配合,不是所有操作系统都完整支持PRI。

────────────────────────────────────────────────────────────

4. Linux VFIO框架:用户态驱动的桥梁

4.1 VFIO架构

VFIO(Virtual Function I/O)是Linux内核的设备分配框架,核心思想:将设备直接暴露给用户态程序,避免内核介入。

VFIO架构分层:

用户态进程(QEMU / SPDK / DPDK / 用户程序)

↓ mmap / ioctl

VFIO内核驱动(/dev/vfio/vfio)

├── IOMMU Type1驱动(VT-d DMA重映射)

├── PCI驱动(/dev/vfio/pci)

└── 设备驱动(pci-stub / vfio-pci)

↓ DMA映射

IOMMU(VT-d)

↓

物理设备(PF或VF)

关键API:

VFIO_GROUP_SET_CONTAINER --- 将进程组绑定到IOMMU容器

VFIO_IOMMU_MAP_DMA --- 建立IOVA → HPA映射

VFIO_DEVICE_GET_INFO --- 获取设备信息(PF/VF/ BAR数量)

VFIO_DEVICE_GET_REGION_INFO --- 获取各BAR的地址/大小

VFIO_DEVICE_MAP_DMA --- 为设备DMA分配IOVA空间

VFIO_DEVICE_SET_IOMMU --- 指定IOMMU类型(Type1/Vendor)

4.2 QEMU/KVM透传VF给虚拟机

QEMU通过VFIO将VF直接分配给VM,完整流程:

QEMU命令行(VF透传示例):

qemu-system-x86_64 \

-enable-kvm \

-machine q35 \

-device vfio-pci,host=0000:3B:10.0,id=vf0 \

-device vfio-pci,host=0000:3B:10.1,id=vf1 \

...

内部流程:

- QEMU打开 /dev/vfio/vfio 主设备

- 通过ioctl将VM的进程组绑定到IOMMU容器

- 读取设备配置空间,建立IOVA映射

- 将BAR映射到QEMU虚拟地址空间

- VM内核加载vfio-pci驱动

- VM看到的就是一个原生PCIe设备(无需Virtio驱动)

4.3 VT-d DMA重映射:安全的基石

VT-d(Intel Virtualization Technology for Directed I/O)是IOMMU在x86上的实现,它为每个设备分配独立的域(Domain):

- 域隔离:每个VM/进程对应独立IOMMU域,域之间硬件隔离

- DMA重映射:设备发出的I/OVA通过页表翻译为HPA

- 中断重映射:设备中断也被IOMMU重映射到正确的中断向量

- 页面属性:RWX权限、DMA只读等精细控制

安全性验证(DMA隔离):确保分配给VM A的VF只能访问VM A的内存,访问VM B的内存会触发IOMMU fault,由Hypervisor处理。

────────────────────────────────────────────────────────────

5. 云/NFV场景的SR-IOV实践

5.1 vSwitch卸载:OVS-DPDK

在NFV场景下,vSwitch(虚拟交换机)是CPU密集型组件。传统OVS在Linux内核中运行,每个数据包都经过软交换,CPU开销巨大。SR-IOV + DPDK彻底改变了这一局面:

OVS-DPDK + SR-IOV架构:

物理网卡(支持SR-IOV)

├── PF:管理接口(ovs-vswitchd控制)

└── VF0 ──→ VM1(云主机)

VF1 ──→ VM2(云主机)

VF2 ──→ OVS-DPDK(vSwitch数据平面)

数据包路径(VM→VM,同主机):

VM1 TX → VF1 DMA → DPDK大页内存

↓

OVS-DPDK查流表 → 匹配action

↓

DPDK大页内存 → VF2 DMA → VM2 RX

关键收益:

- OVS完全运行在用户态(零内核参与)

- 数据包零拷贝(共享大页内存)

- 接近线速(10GE: ~9.8Gbps, 40GE: ~39Gbps)

5.2 AWS/阿里云/华为云的SR-IOV实践

主流云厂商均大规模部署SR-IOV:

- AWS Elastic Network Adapter (ENA):每个EC2实例分配一个VF,网络带宽从5Gbps提升到100Gbps

- 阿里云弹性网卡:基于SR-IOV实现虚拟机毫秒级网卡热迁移

- 华为云iMaster NCE:SR-IOV + OVS-DPDK实现100GE数据中心网络

- Azure Accelerated Networking:VM启动时自动分配VF,延迟从~90μs降到~10μs

5.3 GPU虚拟化:MIG与SR-IOV融合

GPU厂商的虚拟化方案与SR-IOV深度融合:

- NVIDIA A100 GPU:支持MIG(Multi-Instance GPU),将物理GPU切分为7个独立实例,每个实例等价于一个"VF"

- NVIDIA GRID vGPU:游戏/专业可视化的GPU虚拟化技术,底层依赖SR-IOV

- AMD MxGPU:基于SR-IOV,每个VF分配独立GPU硬件资源

- Intel Data Center GPU:支持GFX指派的SR-IOV虚拟化模式

────────────────────────────────────────────────────────────

6. 挑战与未来演进方向

6.1 Live Migration的难题

SR-IOV设备的虚拟机迁移(Live Migration)一直是业界难题:

- 设备状态迁移:VF的DMA队列、统计计数、流量控制状态无法直接导出

- 内存脏页追踪:DPDK大页内存由设备DMA直接访问,Hypervisor无法感知脏页

- 网络连接保持:TCP连接状态在迁移前后必须保持,SR-IOV透传使迁移窗口内需要切换路径

- 硬件差异:不同厂商网卡内部状态格式不统一,软件难以统一抽象

当前解决方案:

- VFIO-live-migration草案(Linux社区推进中):定义标准VF状态保存/恢复接口

- AWS ENA Express:通过硬件辅助连接迁移,解决TCP会话保持问题

- 混合路径迁移:迁移前将VF切换回软件路径,迁移完成后再切回VF(性能短暂下降)

6.2 云原生I/O的演进方向

随着云原生(Kubernetes、DPU、SmartNIC)的兴起,PCIe虚拟化也在演进:

- DPU(Data Processing Unit):将网络虚拟化、存储虚拟化下沉到DPU卡(本质上是带SR-IOV的高级网卡)

- CXL(Compute Express Link):PCIe 5.0/6.0的演进,支持CXL.mem/CXL.cache,实现CPU-GPU-DPU的统一内存寻址

- 零拷贝网络(RDMA over Converged Ethernet):RoCE v2依赖SR-IOV + ATS实现零拷贝高性能网络

- PCIe 6.0 PAM4:64 GT/s速率,DPU和智能网卡的新一代基础设施

────────────────────────────────────────────────────────────