单片机的I/O的几种模式

单片机I/O(通用输入输出)引脚的配置模式,主要可分为输入模式 和输出模式两大类,每类下又有几种具体形式,以适应不同外设和电路需求。

一、输入模式

此模式下,引脚用于读取外部信号(如按键、传感器电平)。为保证读取准确并避免引脚悬空,常需配合上拉或下拉电阻。

-

浮空输入:引脚既不接高电平,也不接低电平,完全由外部信号决定。若外部未连接或处于高阻态,引脚电平不确定,易受干扰。适合外部已有明确高低电平(如推挽输出引脚)或带强上拉/下拉的信号。

-

上拉输入 :芯片内部使能一个弱上拉电阻,将引脚默认拉高到高电平。当外部信号为低时,引脚读为0。适合连接低电平有效的器件(如按键接地)。可省去外接上拉电阻。

-

下拉输入 :芯片内部使能一个弱下拉电阻,将引脚默认拉低到低电平。当外部信号为高时,引脚读为1。适合连接高电平有效的器件。

-

模拟输入 :引脚信号不经过施密特触发器进行整形,直接连接到芯片内部的模数转换器(ADC) 。用于读取连续变化的模拟电压(如电位器、温度传感器输出)。注意:此模式下,数字读取指令(

GPIO_ReadInputDataBit)的结果无意义。

二、输出模式

此模式下,引脚由单片机内部控制,用于驱动外部器件(如LED、继电器)。

-

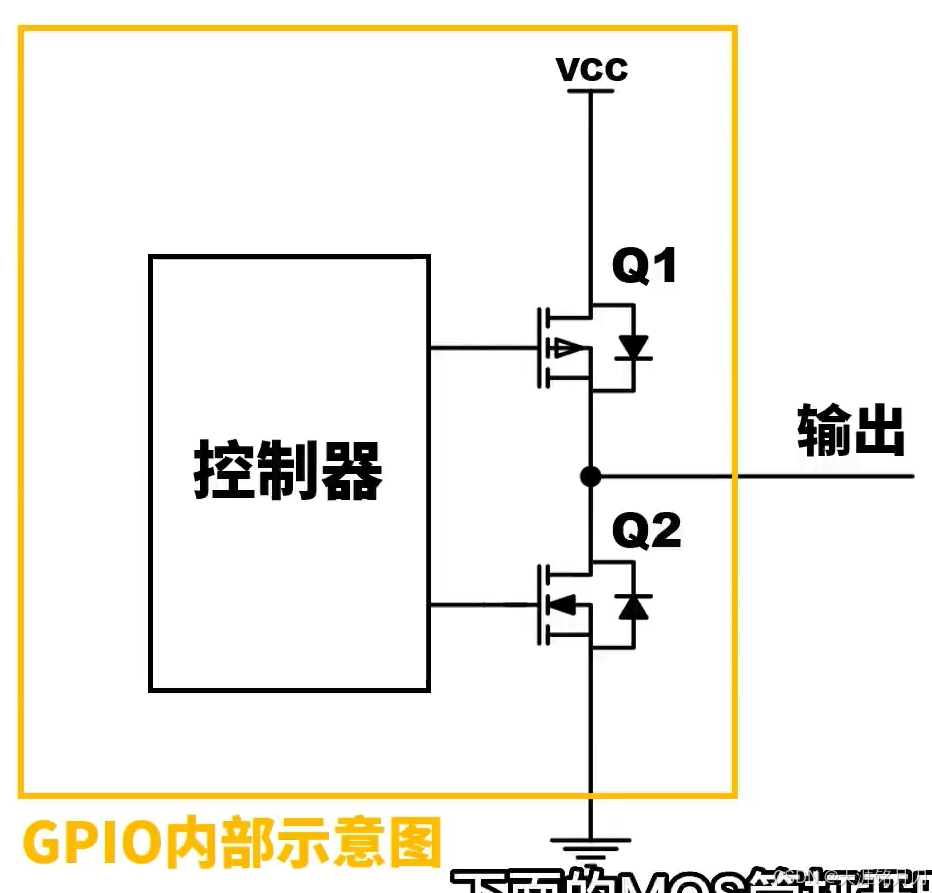

推挽输出 :引脚内部由两个互补的MOS管驱动,一个负责高电平,一个负责低电平。可输出高低电平,驱动能力强。最常见的模式。

- 适用场景:驱动LED、数码管、继电器,或与只接受明确高低电平的芯片通信(如SPI、I2C的部分控制线)。

-

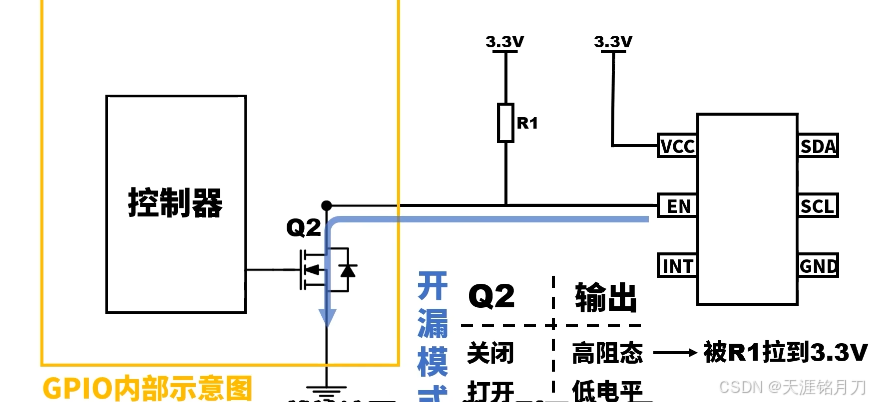

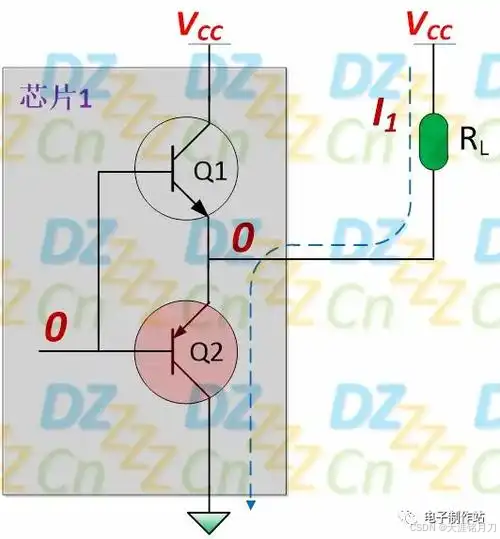

开漏输出 :引脚内部的高电平驱动MOS管被断开。输出高电平时,引脚必须外接上拉电阻才能得到高电平;输出低电平时,MOS管导通,引脚接地。若不加外部上拉,开漏输出只能输出低电平。

-

适用场景:

-

电平转换:需匹配不同电压(如3.3V单片机与5V外设),外接相应电压上拉即可。

-

线与逻辑:多个开漏输出引脚直接相连,当所有引脚都输出高阻(高电平未上拉)时,总线为高;任何一个输出低电平,总线即被拉低。常用于I2C总线。

-

-

上下拉电阻的选择

一、为什么要上拉?

以单片机和某芯片的串口通信为例。

通常,单片机的TX引脚在发送数据时,会被配置为推挽输出模式 ;某芯片的RX引脚必须被配置为空输入或带上拉/下拉的输入。

UART通信协议要求空闲为高电平 ,因此在无数据传输的空闲状态下,RX必须保持高电平。

如果TX为开漏输出,则必须配置上拉电阻!

二、如何确保"上拉"?

-

首选:启用内部上拉

这是最简洁、高效的方式。例如TI CC2340的GPIO支持内部上拉电阻配置。因此,最佳做法是在初始化代码中,将模组的RX引脚配置为"带上拉的输入模式"。

-

备选:添加外部上拉电阻

如果因某些原因无法启用内部上拉(例如引脚模式固定),就需要在电路板上,于模组的RX引脚与电源正极(如3.3V)之间,焊接一个外部上拉电阻。

三、上拉电阻的副作用?

在强电磁干扰环境下,加上拉(如10kΩ)有助于提高RX引脚的抗干扰能力。但TX引脚推挽输出本身就能主动输出高电平和低电平,无需依靠上拉电阻。通常不需要、也不建议再额外加上拉电阻。如果强行在推挽输出引脚上对电源正极接一个上拉电阻,会产生以下影响:

-

低电平被"抬高",可能导致逻辑错误

推挽输出低电平时,内部NMOS管导通,将引脚拉到GND。此时上拉电阻会从电源吸取电流,全部流过NMOS管。由于NMOS管有导通电阻(几十欧姆),这个电流会产生一个压降,使引脚的实际低电平电压升高(例如从0V升到0.3~0.5V)。如果电阻过小(如1kΩ),电流较大,低电平可能超过逻辑0的阈值(比如TTL的0.8V),导致后级电路无法正确识别低电平。

-

增加功耗

引脚输出低电平时,上拉电阻始终消耗功率(V2/RV2/R)。例如5V电源、1kΩ电阻,额外功耗25mW;若电池供电,会缩短续航。

-

可能损坏IO口

推挽输出驱动能力有限(通常几mA到几十mA)。如果上拉电阻太小,低电平电流过大,可能超过引脚最大灌电流规格,造成IO口烧毁。

当上拉电阻与RX串联的保护电阻阻值相同(例如都是100Ω-220Ω)时,在信号源驱动低电平(0V)的情况下:

-

匹配电阻之前的电压 (即上拉电阻与匹配电阻的连接点)不是接近于0 ,而是 VCC/2。

-

因为电流路径为 VCC → 上拉电阻R → 匹配电阻R → 信号源(0V),两个电阻串联分压,中间点电压正好是电源电压的一半。(RX引脚是浮空输入 ,这意味着它的内部阻抗极高(通常为几兆欧姆甚至更高),几乎没有任何电流可以流入引脚内部。所以,整个电流路径在到达RX引脚后就断开了,无法形成一条从VCC到GND的完整闭合回路,RX仅能检测电压)

-

接收端(引脚输入)由于阻抗极高,匹配电阻上无电流流过,因此引脚电压也等于VCC/2。

实际影响 :VCC/2很可能落在逻辑电平的"不确定区域"(例如TTL中0.8V以下为低,2V以上为高,5V电源时2.5V无效),导致接收端无法正确识别低电平。因此,上拉电阻的阻值必须远大于匹配电阻(例如上拉10kΩ、匹配22Ω),才能保证低电平时匹配电阻之前的电压接近0V。两者相同是不合理的设计。

四、上拉电阻的好处

对于UART通信,抗干扰的关键是降低RX引脚的直流阻抗 ,并且不影响TX的正常驱动。标准方案:

-

在RX线上拉一个电阻到VCC (例如1kΩ~10kΩ,强干扰取1k~4.7kΩ)

电阻一端接RX,另一端接电源正。这样:

-

空闲时,RX被稳定在高电平(UART空闲为高)。

-

干扰电流被电阻分流,噪声电压降低。

-

TX信号(来自对端设备的推挽输出)驱动能力足够,能轻松将RX拉低,不受上拉电阻影响(因为上拉电阻值远大于TX驱动管的导通电阻,分压很小)。

-

-

必要时同时并联小电容(如100pF~1nF,RX对地),构成低通滤波器,滤除高频尖峰。

-

TX线本身无需上拉(因为推挽输出,但可串联一个小电阻如22Ω~100Ω,用于抑制振铃,并限制意外短路电流)。

五、上拉电阻如何降低干扰?

干扰源 :在PCB走线或导线上感应出一个高频尖峰电流,假设为 1 μA(在强电磁干扰环境下很常见)。

RX输入引脚:原本的输入阻抗极高,视为开路。

干扰电流 InoiseInoise 没有其他低阻通路,只能流过电阻R。根据欧姆定律,在RX引脚上产生的噪声电压为:

Vnoise=Inoise×R

| 上拉电阻值 | 噪声电压 (1μA干扰) | 对逻辑电平的影响 (以5V TTL为例,VIL_max≈0.8V) |

|---|---|---|

| 悬空 (≈10MΩ) | 10V | ❌ 远超Vcc,必定误触发 |

| 100kΩ | 0.1V | ⚠️ 已接近噪声容限边缘,可能误判 |

| 10kΩ | 10mV | ✅ 远低于0.8V,可靠 |

| 1kΩ | 1mV | ✅✅ 极佳,几乎免疫 |

结论:电阻从100kΩ降到10kΩ,噪声电压从0.1V降到10mV------这就是"噪声电压降低"的量化体现。而在1kΩ时仅为1mV,抗干扰能力再提升10倍。

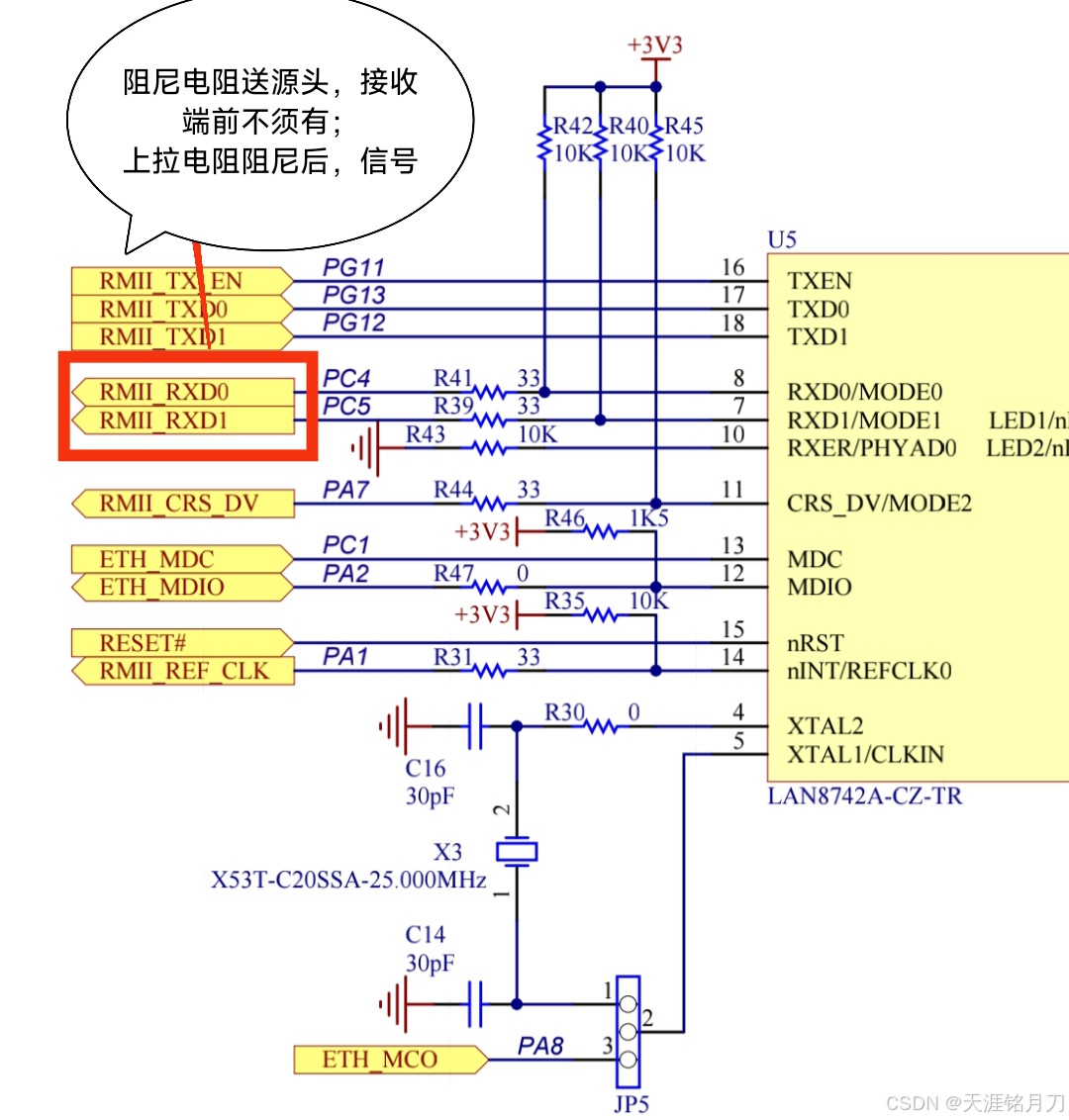

六、上拉电阻和阻尼电阻如何配合?

打油诗一首

阻尼电阻送源头,接收端前不虚有;

上拉电阻阻尼后,信号反射不再有。

(一)、阻尼电阻应该靠近GPIO输出端放置:

1. 抑制信号反射

-

信号从发送端(TX)出发,经过 PCB 走线或电缆到达接收端(RX)。

-

如果发送端输出阻抗很低(典型 MCU 输出阻抗约 25Ω~50Ω),而走线特性阻抗较高(如 100Ω~120Ω),会导致阻抗不匹配,产生反射。

-

串联阻尼电阻 (如 220Ω)加在发送端,可以增加发送端的输出阻抗,使其接近走线特性阻抗,从而吸收反射能量。

2. 放在接收端(RX)完全无效

-

如果电阻放在接收端,反射信号已经在走线上来回振荡,到达接收端时才会经过电阻。

-

此时电阻只能衰减信号幅度 ,但无法抑制已经发生的反射。

-

结果:接收端可能看到振铃、过冲,但信号已经畸变。

(二)、为什么不是上拉电阻更靠近?

如果让上拉电阻比阻尼电阻更靠近输出端,此时问题出现:

-

反射抑制失效:信号在到达阻尼电阻之前,经过上拉电阻节点时已经可能产生反射(上拉电阻到VCC的路径形成阻抗不连续点)。

-

上升沿变缓:阻尼电阻如果放在上拉电阻之后,它无法有效抑制从上拉电阻节点反射回来的信号。

-

VCC噪声耦合:靠近GPIO的大面积上拉电阻网络,在高速翻转时容易将电源噪声直接引入信号路径,而阻尼电阻无法过滤(因其在错误的一侧)。

总结

| 顺序 | 过冲抑制 | 反射抑制 | 电平稳定性 | 推荐场景 |

|---|---|---|---|---|

| 阻尼电阻 → 上拉电阻 | 优 | 优 | 良 | 所有高速/长线I/O |

| 上拉电阻 → 阻尼电阻 | 差 | 中 | 中 | 低速、极短走线(<5cm) |

场景对照表

| GPIO角色 | 阻尼电阻位置 | 上拉电阻位置 |

|---|---|---|

| 输出(如驱动LED、I2C 时钟) | 紧贴GPIO引脚 | 阻尼电阻之后,仍靠近MCU |

| 双向(如I2C数据线) | 紧贴GPIO引脚(主设备侧) | 总线任意,或在阻尼电阻之后 |

| 纯输入(如按键检测) | 靠近外部信号源 | 紧贴MCU引脚 |