0.Virtuoso 中的总框架

1. File & Launch 界面

1.1 Launch 界面

-

ADE Explorer基础级电路仿真环境,用于单测试台的电路分析(如 DC/AC/ 瞬态仿真),是模拟设计的入门级验证工具,和 Spectre 仿真器深度集成。

-

ADE Assembler高级仿真管理工具,可批量配置、运行和回归多组仿真测试,支持工艺角分析、蒙特卡洛分析,适合复杂设计的批量验证与数据管理。

-

Layout XL:基础连通性驱动版图,实现原理图与版图的交叉检查(LVS/DRC 联动),支持交互式布线与器件放置,是全定制模拟版图的主力工具。

-

Layout EXL:XL 的增强版,增加了电感知设计、仿真驱动布线、自动放置等辅助自动化能力,可大幅提升先进节点设计的效率。

-

Layout MXL:面向标准单元 / 数字模块的自动布局布线(APR)工具,支持自动 P&R、电源网络规划,适合大规模数字或混合信号模块的版图实现。

-

Pcell IDE参数化单元(Pcell)的开发与调试环境,工程师可通过它编写、测试和维护 SKILL 代码实现的参数化器件,适配不同工艺节点的设计需求。

-

**Configure Physical Hierarchy...**用于配置原理图与版图的层次对应关系,解决层次结构不匹配(如原理图扁平化但版图分层)的问题,确保 LVS 检查能正确识别设计层次。

-

Plugins管理 Virtuoso 的第三方插件与扩展,可加载自定义 SKILL 脚本、工艺相关工具或第三方 EDA 工具接口。

1.2 File界面

-

New...:用于新建库、单元或版图视图,是创建新设计的入口。 -

Open...:打开已有的库、单元或版图文件。 -

Open Schematic:可以快速打开当前版图对应的原理图视图,方便进行电路与版图的对照。 -

Close:关闭当前的版图编辑窗口。 -

Save:保存当前对版图所做的修改。 -

Save a Copy...(快捷键 F3):将当前设计另存为一个副本,常用于版本备份或分支开发。 -

Discard Edits...:放弃所有未保存的修改,将设计恢复到上次保存的状态。 -

Save Hierarchically:分层保存整个层次化设计,确保所有子单元的修改都能被保存。 -

Make Read Only(快捷键 Shift+2):将当前设计设置为只读模式,防止误修改,常用于冻结的流片版本。 -

Export Image...:将当前版图窗口的内容导出为图片格式,方便插入到设计文档或报告中。 -

Properties...(快捷键 Shift+Q):查看或修改当前单元、视图或对象的属性信息。 -

Summary:查看当前设计的统计信息,比如层数、器件数量、线网数量等。 -

Print.../Print Status...:用于打印版图,或查看打印任务的状态。 -

Bookmarks:管理版图中的书签,方便在大型设计中快速跳转到关键位置。 -

Set Default Application...:设置与文件关联的默认应用程序。 -

Close All:关闭当前打开的所有 Virtuoso 窗口。 -

Export Stream from VM:直接从内存中导出 GDSII 流文件,无需先保存到磁盘,适合大型设计,效率更高。Export Stream from VM 直出,不落地存工程文件 -

Export Oasis from VM:直接从内存中导出 OASIS 格式文件,OASIS 是比 GDSII 更紧凑的版图数据格式。 -

Load Physical View...:加载物理视图,常用于层次化设计管理或导入外部版图数据。

2. Edit 界面

在 Cadence Virtuoso Layout 中,ROD 全称是 Repetitive Object Database(重复对象数据库) ,它是一种结构化的参数化对象,常用于创建和管理需要重复生成、保持关联的版图图形(如传输线、差分线、渐变线、电感、阵列等)。

勾选「Create as ROD object」后,创建的图形会被作为一个 ROD 对象存储,而非普通的 polygon/path,核心优势如下:

-

参数可编辑:可通过 ROD 编辑器修改长度、宽度、间距、角度等参数,图形自动更新;

-

结构可关联:对象间保持拓扑关系(如差分对的两根线自动对齐、间距固定);

-

支持重生成:修改工艺或参数后,可一键刷新所有 ROD 对象,无需手动重画;

-

便于批量管理:可通过 SKILL 脚本批量修改、导出、删除 ROD 对象;

-

与普通图形的区别:ROD 对象本质是 "参数模板",而非固定图形。如果直接打散(un-rod),会失去参数化特性,变为普通图形,无法再通过 ROD 编辑器修改。

1.撤销/删除/拉伸/对齐等操作

-

Undo(快捷键U):撤销上一步操作,支持多级撤销,方便快速回退误操作。 -

Redo(快捷键Shift+U):恢复被撤销的操作。 -

Move(快捷键A):移动选中的版图对象(线、器件、过孔等)。 -

Copy(快捷键C):复制选中的对象,可多次粘贴。

可以copy 到用户需要的层,

Stretch(快捷键S):拉伸线、多边形等对象,常用于调整线长或修改形状。

当选择一个edge 的时候就是拉伸整个边缘,当选择一个object 的时候,就是移动,和移动命令一致。

-

Delete(快捷键Z):删除选中的对象。 -

Repeat Copy(快捷键H):按固定偏移重复复制对象,适合批量生成过孔、阵列等结构。 -

Quick Align:快速对齐多个选中对象,支持水平 / 垂直对齐、等间距分布等。

使用方法:先选择一个edge,点击后变成红色,然后继续鼠标点选择第二个edge,则会实现第一个edge 和第二个edge 对齐,但是该功能只会将需要对齐的object 沿着X或者Y 方向或者对齐的走线的方向对齐。

-

Flip:翻转选中对象,支持水平 / 垂直镜像,常用于器件引脚对称设计。 -

Rotate:旋转选中对象,支持 90°、180°、270° 等固定角度旋转。

2 Basic:

包含基础编辑工具,如修剪、延伸、合并、拆分图形等。

2.1 Merge(合并):

把多个相邻、同层的图形(如金属线、多边形)合并成一个整体对象,减少 DRC 报 "重复图形" 或 "非矩形路径" 的问题,也方便批量操作。

2.2 Yank(提取)& paste (粘贴):

从子单元(Instance)中 ** 提取(Yank out)** 一个对象,使其成为顶层设计中的独立对象,脱离原有的层次结构。 是跨层级复用 / 修改版图对象的核心组合,常用于从子单元提取对象到顶层修改,或复制实例内图形后再粘贴使用。

Yank 提取对象后,自动进入 "复制 / 粘贴缓冲区";按 Ctrl+V 或菜单 Edit → Paste;在目标位置点击,即可粘贴一份与 Yank 对象完全相同的副本。

2.3 Chop(切断 / 剥离):

与 Yank 相反,Chop用于 *断(Chop off)** 一个对象与它所属层次的关联,或剥离出一个对象的局部片段。它有两种常见用法:(1)可以像剪刀一样,把一个对象(线、多边形)的一部分 "剪" 出来,变成一个独立对象,原对象被截断。(2)当一根线穿过子单元边界时,Chop 可以在边界处将其切断,让线分成两部分。

chop 的参数

-

Snap Mode :设置切割时的对齐模式,当前为

orthogonal(正交模式),切割方向将强制为水平 / 垂直方向,避免斜向切割。 -

Remove chop:勾选后,切割完成后自动删除切割用的矩形工具,不会在版图中留下额外图形。

-

Chop array:勾选后,可同时对选中的阵列对象执行批量切割,一次性处理多个重复结构,大幅提升效率。

-

Pins and boundary to grid:勾选后,切割过程中引脚和模块边界会自动吸附到工艺网格上,保证对齐精度。

-

Pins to boundary:勾选后,引脚会自动吸附到模块边界,常用于切割软模块(Soft Block)时同步调整引脚位置。

-

Soft Block Pins to:软模块引脚的对齐规则:

-

Modified Edge:引脚对齐到切割后修改过的模块边缘。 -

Closest Edge:引脚对齐到距离最近的模块边缘。

-

-

All edges to manufacturing grid:勾选后,切割生成的所有图形边缘都会自动对齐到制造网格,避免出现非工艺网格的坐标,减少 DRC 报错。

3. Advanced:

提供高级编辑功能,如批量调整线宽、拐角优化、批量修改属性等。

3.1 Reshape(快捷键 Shift+R)

- 用于重塑多边形 / 路径线的形状,支持拖拽顶点、添加 / 删除边,是手动修改复杂图形的核心工具。

reshape 参数

-

Mode :当前设置为

rectangle(矩形模式)/line (线型模式),rectangle(矩形模式)表示以矩形边界为参考进行重塑;也可切换为其他模式,适配多边形、路径线等不同对象的重塑逻辑。 -

Snap Mode :当前设置为

orthogonal(正交模式),拖拽顶点时会强制对齐水平 / 垂直方向,避免生成斜向边,减少后续 DRC 违规。可以选择anyAngle / diagonal /orthogonal /L90XFirst/L90YFirst 等模式。

anyAngle:无角度限制,任意角度都可以,完全自由拖拽。

diagonal:强制走 45°/135° 等对角线方向,边只能是水平、垂直或 45° 斜向。

orthogonal:强制正交,边只能是水平或垂直方向,不允许斜向。

L90XFirst / L90YFirst:

-

L90XFirst:优先锁定 X 轴(水平方向),先动水平,再垂直,适合横向走线。 -

L90YFirst:优先锁定 Y 轴(垂直方向),先动垂直,再水平,适合纵向走线。

-

Pins and boundary to grid:重塑时引脚和模块边界会自动吸附到工艺制造网格,避免出现非网格坐标,保证工艺合规性。

-

Pins to boundary:引脚会自动吸附到模块边界,重塑软模块边界时,引脚会随边界同步调整位置,保持连接关系。

-

Modified Edge(当前选中):引脚对齐到被修改后的模块边缘,适合调整模块边界时保持引脚与边界的贴合。 -

Closest Edge:引脚对齐到距离最近的模块边缘,适合轻微调整边界时自动适配引脚位置。

**使用指南:**选择reshape 按钮后,可以选择一个需要修改的shape,

-

**Split(快捷键

Ctrl+S)**将一个对象(线、多边形、路径)按指定线 / 点分割成多个独立对象。 -

**Modify Corner...**专门用于修改图形的拐角,支持倒圆角、切斜角、设置拐角类型(如 45°/90°/ 圆弧)。

-

**Size...**按比例或指定偏移量放大 / 缩小对象,支持整体扩缩、单边扩缩(如仅加宽一侧)。

-

Attach/Detach用于将两个对象 "附着" 在一起,或解除附着关系。典型场景:把走线与过孔 / 引脚自动连接、解除走线与实例的绑定、批量修正连接关系。

-

**Move Origin(快捷键

Shift+H)**移动对象的坐标原点,常用于调整实例 / 图形的基准点,方便对齐或批量复制。 -

**Align...**高级对齐工具,支持按网格、边界、参考线、多个对象的边缘 / 中心对齐,可设置水平 / 垂直对齐、等间距分布。

-

**Slot...**在对象上创建开槽 / 开窗,常用于电源层散热、工艺兼容、电流路径优化。

-

Swap Components交换两个对象的位置 / 属性,常用于器件互换、引脚交换(如差分对引脚互换)。

-

Convert:用于对象类型转换,例如将线转换为多边形、文本转版图对象、或转换为工艺兼容的结构。 -

Hierarchy:层次化设计编辑工具,如打散 / 还原层次、修改子单元实例、跨层次编辑等。 -

Group:对象分组管理,可将多个对象组合为一个整体,方便批量操作与管理。 -

Fluid Pcell:可编程单元(Pcell)的编辑工具,支持修改 Pcell 参数、刷新实例等。 -

Select:高级选择工具,如按属性选择、按网络选择、按层选择等,快速批量筛选对象。 -

DRD Targets:DRD(Design Rule Driven)目标管理,用于设置和编辑 DRD 驱动的版图调整目标。 -

Wiring:布线相关工具,如推挤布线、绕线、批量连接引脚等,用于电源 / 信号网络的快速连接。 -

Edit Soft Blocks...:编辑软模块(Soft Block),支持修改模块边界、引脚位置等。 -

Component Types...:管理和编辑版图中器件的类型与属性,如修改器件模型、引脚定义等。

3. View 界面

-

Zoom In(快捷键Ctrl+Z):放大当前视图,聚焦局部细节。 -

Zoom Out(快捷键Shift+Z):缩小当前视图,查看更大范围的版图。 -

Zoom To Area:框选指定区域进行放大,常用于快速定位并查看特定局部。 -

Zoom To Grid(快捷键Ctrl+G):将视图缩放到与当前网格对齐的显示比例,方便基于网格的精确编辑。 -

Zoom To Selected(快捷键Ctrl+T):自动将选中的对象居中并适配到当前窗口,快速聚焦目标对象。 -

Zoom To Fit All(快捷键F):将整个版图完整适配到窗口中,快速查看整体布局。 -

Zoom To Fit Edit(快捷键Ctrl+X):将当前编辑的区域适配到窗口,聚焦正在操作的部分。 -

Magnifier:放大镜工具,可在不改变整体视图的情况下查看局部细节,常用于检查微小结构。 -

Dynamic Zoom:动态缩放功能,勾选后支持鼠标滚轮 / 拖拽平滑缩放视图,是默认开启的常用功能。 -

Pan:平移视图工具,可拖拽移动当前窗口的显示区域。 -

Redraw(快捷键Ctrl+R):刷新重绘当前视图,解决显示异常或延迟问题。 -

Area Display:区域显示设置,可自定义显示区域、设置裁剪视图,方便局部编辑。 -

Show Coordinates:在界面显示当前鼠标位置的坐标值,便于精确定位。 -

Show Angles:显示对象的角度信息,常用于非正交布线或特殊角度结构的编辑。 -

Show Selected Set:高亮显示当前选中的对象集合,便于确认选择范围。 -

Save/Restore:视图状态的保存与恢复,可保存多个常用视图位置,一键切换,方便在大型设计中快速跳转关键位置。 -

Background...:设置视图的背景颜色,可自定义为深色 / 浅色模式,优化视觉体验。

4. Creat 界面

-

Shape:创建基础几何图形,如矩形、多边形、路径线、圆等,是构建版图金属、有源区等结构的基础。具体信息请参加Virtuoso Creating Objects(6-1). -

Wiring:布线相关工具,用于创建和编辑信号 / 电源走线,支持不同线宽、角度的连线操作。 -

wire:可以画任意角度、斜线、45°、任意拐角

-

bus:一组平行多根线,总线、并行信号

-

point to point:两点之间直接连线,自动找最短路径

-

standard wire:只能水平 + 垂直正交走线,90° 拐角走线路径规整,自动拐直角,不能斜着画

-

Instance...(快捷键I):调用并放置库中的器件实例(如标准单元、IP 核、自定义模块),是层次化设计的核心操作。

Pin...:

创建版图引脚,用于定义端口位置、连接关系,实现与原理图网表的对应。

-

Mode :

Manual(手动模式,当前选中)/Auto(自动模式)-

Manual:手动指定 Pin 的位置、形状和名称,是最常用的模式; -

Auto:根据原理图 / 网表自动创建 Pin,适合 XL 模式下的端口同步。

-

-

Connectivity :

Strong(强连接,当前选中)/Weak(弱连接)-

Strong:Pin 会强制绑定到指定网络,LVS 检查时必须与该网络连接; -

Weak:仅做标记性端口,不强制绑定网络,多用于临时端口; -

Must Connect All Pins:勾选后,所有创建的 Pin 都必须连接到指定网络,避免悬空。

-

-

Terminal Names :输入 Pin 的名称,支持总线格式(如

data<7:0>); -

Keep First Name:勾选后,阵列 Pin 会以第一个名称为基准自动编号; -

Create Label:勾选后,自动为 Pin 生成文本标签,方便识别; -

Create as ROD Object:将 Pin 创建为 ROD(Reusable Object Definition)对象,方便复用; -

X Pitch / Y Pitch:设置阵列 Pin 的水平 / 垂直间距,配合总线名称批量生成多个端口;

-

Physical Only:勾选后,只创建物理端口,不关联逻辑网表,仅用于 DRC 检查。

-

Pin Figure :选择 Pin 的形状,当前为

rectangle(矩形,最常用),还支持polygon(多边形)、dot(点)、circle(圆形)、existing object(基于已有图形创建); -

Attach Pin to Overlapping Shape on Same Layer:勾选后,Pin 会自动附着到同层重叠的金属图形上,保持连接关系; -

Create Stacked Pin:勾选后,创建堆叠式 Pin,可设置多层金属和过孔,支持create vias选项自动生成过孔。 -

I/O Type :设置端口的电气类型,当前为

inputOutput(输入输出,通用类型),还支持input/output/switch/jumper/unused/tristate; -

Snap Mode :

orthogonal(正交模式,当前选中),创建 Pin 时强制对齐水平 / 垂直方向,也支持其他角度模式; -

Access Direction :设置端口的可访问方向,当前勾选

top/bottom/left/right四个方向,布线时可从任意方向连接; -

Signal Type :当前为

signal(信号类型),也可设置为power/ground/clock等,方便后续电源 / 信号的区分处理。 -

Label...(快捷键L):添加文本标签,用于标记网络名称、器件名称,辅助版图的可读性与网表匹配。 -

Via...(快捷键O):创建过孔,用于不同金属层之间的垂直连接,是电源 / 信号跨层布线的关键。创建Via的前提条件为 techfile 中将 VIA 定义; -

Multipart Path:创建多段路径线,可灵活设置不同段的线宽、拐角,常用于复杂走线或电源条设计。 -

Fluid Guard Ring...(快捷键Shift+G):创建可编辑的保护环(Guard Ring),用于隔离噪声、抗闩锁效应,支持自定义形状与参数。 -

MPP Guard Ring:基于多段路径的保护环创建工具,适合复杂轮廓的保护环设计。 -

Slot ...:创建开槽结构,常用于电源层散热、工艺兼容或特殊结构的版图实现。 -

P&R Objects:与布局布线相关的对象创建工具,如轨道、网格、约束区域等,用于配合自动布线流程。 -

Group:创建对象组,可将多个元素打包为一个整体,方便批量移动、复制和管理。 -

Microwave:微波 / 射频相关的专用版图创建工具,如传输线、谐振器等高频结构。 -

Soft Pins...:创建软引脚,用于模块间的虚拟连接或非物理端口定义。 -

Feed Through Terminal Pins...:创建穿通终端引脚,用于跨模块 / 跨层的连接,常用于电源分布或总线布线。

5. Verify 界面

-

Markers:管理验证标记点,用于查看 DRC/LVS 等检查的错误标记,支持跳转到错误位置、筛选标记类型、清除标记等操作,是定位和修复设计错误的入口。 -

Selection:用于在验证流程中筛选和管理需要检查的对象,可按层、按网络、按区域选择版图部分,支持局部 DRC/LVS 检查。 -

Application Readiness Checker...:应用就绪度检查工具,用于验证设计是否满足后续流程(如流片、导出 GDS、封装协同设计)的前置条件,检查内容包括 DRC 状态、网表一致性、模块完整性等。 -

Design...:设计级验证入口,通常包含 DRC(设计规则检查)、ERC(电气规则检查)等核心验证功能,用于检查版图是否符合工艺设计规则与电气要求。 -

Integrity...:版图完整性检查工具,用于验证版图的结构一致性,比如检查对象重叠、未闭合多边形、悬空走线、层次化设计实例的完整性等问题,提前发现潜在的结构错误。

6. Connectivity 界面

-

Pins:管理版图引脚,可查看、编辑引脚属性,或按引脚筛选、定位对象,用于核对端口连接关系。 -

Nets:管理版图中的网络(信号 / 电源地),可查看网络连接关系、高亮显示完整网络、筛选特定网络,是检查电源分布与信号走线的入口。 -

Short Locator...:短路定位工具,可自动查找并高亮版图中的短路点,支持筛选特定层 / 网络间的短路,快速定位 DRC/LVS 报出的短路错误。 -

Net Tracer:网络追踪工具,可高亮显示选中网络的完整路径,追踪走线、过孔和器件连接,排查开路、错连问题。 -

Extract Layout...:从版图中提取网表,生成与原理图网表对比的版图网表,是 LVS 验证的基础步骤。 -

Incomplete Nets:检查并列出版图中未完全连接的网络(如悬空引脚、未闭合走线),提前发现连接性问题。 -

XL Probe:XL(XLR)环境下的探针工具,可在版图中点击对象,同步在原理图中高亮对应部分,实现原理图 - 版图的交叉对照调试。 -

Generate:生成相关文件或对象,如根据网表生成引脚标签、生成电源 / 地网络的连接信息等。 -

Check and Update...:检查并更新版图与原理图的一致性,可同步网表修改、更新实例对应关系。 -

Check:执行连接性检查,如网络完整性、引脚匹配、电源地连接等,提前发现 LVS 会报出的问题。 -

Update:根据原理图或网表更新版图,如同步网络名称、引脚定义,修正不一致的连接信息。 -

Define Device Correspondence...:手动定义版图器件与原理图器件的对应关系,用于处理 LVS 无法自动匹配的特殊器件或层次化实例。 -

Backannotate:反向标注,将 LVS 或仿真的结果(如寄生参数、延迟信息)标注回版图或原理图中,辅助后续优化与验证。

7. Option 界面

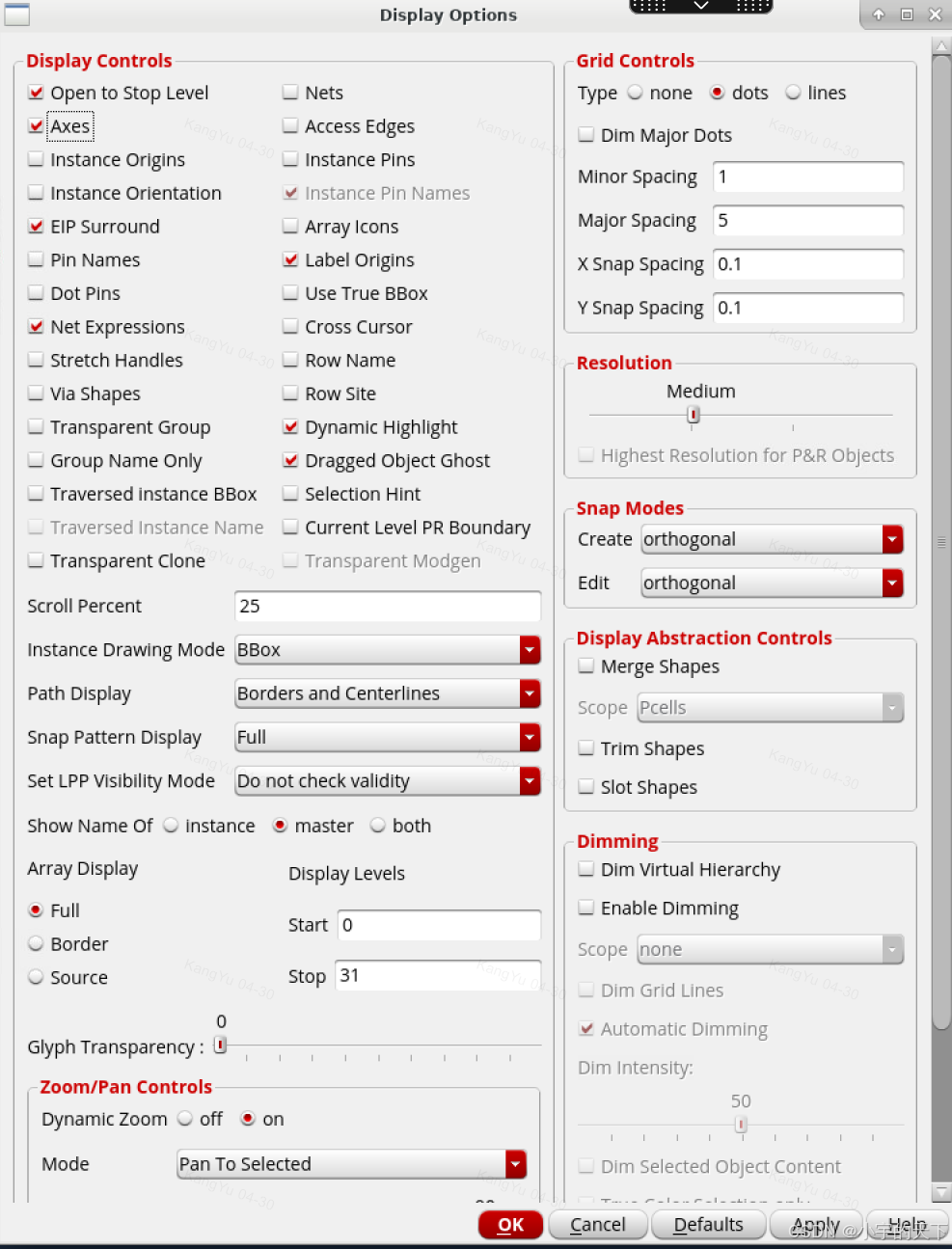

Display...(快捷键P):打开显示设置窗口,可自定义各层的颜色、线型、填充样式,以及对象(引脚、过孔、实例)的显示属性,是版图可视化风格的核心配置入口。

-

Editor...(快捷键Ctrl+Shift+X):编辑器全局偏好设置,可配置默认线宽、网格参数、单位精度、编辑行为(如自动对齐、吸附模式)等,适配个人编辑习惯。 -

Selection...:设置对象选择规则,如按层 / 类型筛选、多选模式、点击容差,优化复杂版图中的选择效率。 -

Magnifier...:放大镜工具的设置项,可调整放大倍数、窗口大小、显示模式,用于局部细节检查。 -

Multiple Patterning...:多重曝光工艺相关的显示与设置,用于处理先进工艺下的颜色分解、间距规则显示,支持 DP/TP/MP 等多图案设计。 -

DRD Edit...:设计规则驱动(DRD)编辑的设置,可配置 DRD 规则、约束条件与实时反馈行为,让编辑过程自动遵循工艺规则。 -

Highlight...:高亮设置,可自定义选中对象、网络、错误标记的高亮颜色与模式,方便区分不同状态的对象。 -

Net Tracer...:网络追踪工具的设置,可配置追踪时的显示效果(如高亮颜色、路径显示方式),辅助连接性检查。 -

Dynamic Display...:动态显示设置,控制缩放、平移时的显示刷新行为,平衡性能与可视化效果。 -

Transparency...:透明度设置,可调整不同对象 / 层的透明度,方便查看层次重叠的结构。 -

Smart Display...:智能显示设置,控制缩放比例变化时的显示细节切换,优化大型版图的显示性能。 -

Net Name Display...:网络名称显示设置,可配置标签的显示位置、大小、字体,方便查看网络信息。 -

Connectivity...:连接性相关的显示设置,控制引脚、过孔、走线的连接关系可视化,辅助检查开路 / 短路问题。

8. tools 界面

- Find/Replace... (Shift+S) 批量查找/替换版图对象(图形、标签、实例等),用于修改文本、筛选图形、清理冗余走线。

可以搭配复制粘贴移动等操作,利用find命令找到想要的object,做所有操作。

-

Area and Density Calculator... 计算图形面积、金属密度并生成报告,满足Foundry金属密度规则、统计dummy覆盖率。

-

Create Measurement (D) 创建距离/角度/面积测量标记,用于测量线宽、线距、走线长度,验证DRC间距。

-

Clear All Measurements (Shift+D) 删除当前单元内所有测量标记,清理临时测量痕迹。

-

Clear All Measurements In Hierarchy (Ctrl+Shift+K) 递归删除当前单元及所有子单元内的测量标记,批量清理层次化设计中的测量数据。

-

Enter Points ... 交互式输入坐标点,用于精准定位图形顶点、创建多边形路径。精确寻找对应的坐标信息。

-

Remaster Instances... 更新实例主单元(master),同步所有调用实例的修改,确保子单元变更生效。

-

核心用途 :批量将当前设计中引用的某个

Lib/Cell/View实例,替换为另一个目标Lib/Cell/View,常用于:-

工艺节点迁移(如从 180nm 转 45nm,替换器件库)

-

标准单元库更新

-

复用设计时替换模块引用

-

-

左侧「Search for」 :填写要被替换的旧主单元信息(库、单元、视图名),匹配当前设计中所有引用该单元的实例。

-

右侧「Update to」 :填写替换后的新主单元信息,可通过「Browse」按钮快速选择目标库 / 单元 / 视图。

-

Check Termina(Check Terminals):勾选后会自动校验新旧单元的端口(Pin/Port)是否匹配,避免替换后产生端口不匹配的错误。

- Create Pins From Labels... 从版图中的文本标签自动生成引脚,快速完成LVS所需的Pin创建。是快速将版图中的文本标签批量转换为 LVS 合规端口的核心工具,常用于原理图转版图、导入第三方网表后的端口生成场景。

| 选项 | 说明 |

|---|---|

| Objects Within | 选择标签的作用范围: • Cellview:对整个当前单元视图生效 • Selected Instances:仅对选中的实例生效 |

| Object Type | 选择要识别的文本对象类型: • Label:仅识别版图标签 • Text Display:仅识别文本显示对象 • Both:同时识别两种文本对象(当前勾选) |

| Objects | 选择处理对象范围: • All:处理所有符合条件的标签(当前勾选) • Selected:仅处理手动选中的标签 |

| Attach Label To Pin | 勾选后,会将原文本标签自动绑定到生成的端口上,便于后续编辑和识别 |

| Define With | 端口定义依据: • Layer:按文本所在图层生成端口(当前勾选,最常用) • Text:按文本内容属性生成端口 |

- Tap (T) 创建电源/地tap结构,用于衬底偏置、ESD保护设计;

Cadence Virtuoso 版图编辑器里的 Tap(点选 / 拾取)设置窗口,用于配置你用鼠标点选版图对象时,软件的识别规则和交互行为。

-

Export Label... 导出版图中的文本标签及坐标,用于外部脚本批量处理。

-

Layer Generation... 按工艺规则生成衍生层(如via、cut层),实现过孔自动生成、工艺层派生。

Layer Generation 允许通过基础层的布尔运算自动生成新的工艺层,常见运算包括:

-

AND:交集运算,生成两个图层的重叠区域 -

OR:并集运算,合并两个图层的所有区域 -

NOT:补集运算,生成图层的反向区域 -

AND NOT:差集运算,生成 A 图层中不与 B 图层重叠的区域

- Technology Database Graph 查看工艺文件的层/约束关系图,用于调试工艺文件、排查层依赖、验证DRC规则。

用于可视化查看和管理当前项目加载的 PDK / 工艺库层级关系,是排查工艺文件加载、库引用问题的核心工具。

-

Effective(当前已勾选):显示生效状态的工艺库,即实际被 Virtuoso 加载并生效的配置(含继承、合并后的最终状态)。 -

As Defined:显示原始定义的工艺库,即 PDK 文件中原始声明的层级结构,不包含运行时的合并 / 继承逻辑。

- Pad Opening Info... 查看焊盘开窗信息,用于封装前验证开窗层是否正确。

-

Bond Pad 图层设置

-

Layer/Purpose:指定焊盘开窗所在的图层(当前为geLayer drawing) -

Search Depth:设置实例层级搜索深度(当前为 0,仅在当前 cellview 内搜索) -

Dimension:按尺寸过滤焊盘(当前为> 0,即所有非零尺寸的焊盘)

-

-

Region 区域过滤:可指定矩形 / 多边形区域,仅统计区域内的焊盘

-

Label/Name 标签设置:

-

Object Type:选择标签类型(Label/Text Display/Both,当前勾选Label) -

Layer/Purpose:指定标签所在图层(与焊盘图层同为geLayer drawing) -

Highlight:高亮显示所有匹配的焊盘 / 标签

-

Sort 排序:

1st PAD coords:指定排序基准坐标(当前为(0 0))Sort Direction:排序方向(当前为Clockwise,顺时针)

| 模式 | 说明 |

|---|---|

Generate Report(当前勾选) |

生成 Bond Pad 的统计报告,输出坐标、尺寸、标签等信息 |

Generate Labels |

自动为焊盘生成文本标签 |

Promote Label To Top |

将子实例中的焊盘标签提升到顶层版图 |

-

Express Pcell Manager... 管理参数化单元(Pcell),编辑Pcell参数、更新实例、批量修改配置。

-

Cover Obstructions Manager... 管理布线阻塞/覆盖区域,设置布线禁止区、配置金属填充避让规则。

-

Abstract Generation... 生成版图抽象(Abstract),为顶层布局布线提供简化版图模型。

-

Dynamic Abstract Generation for Pcells 为Pcell动态生成简化抽象模型,用于顶层布线的快速评估。

-

Create shapes from Width Spacing Pattern... 根据线宽/间距模式批量生成重复图形,用于金属密度填充、工艺验证结构生成。

| 选项 | 作用说明 |

|---|---|

| Layer | 指定要生成图形的目标图层(如 metal1/metal2 等),需与工艺文件定义一致 |

| WSP | 关联线间距规划配置文件 / 设置,决定图形生成的间距、宽度等规则 |

| Fig Group name | 生成图形的组名,默认 wspShapeGenerator_fg,勾选 Append 可追加到已有图形组 |

| Generate Region Only | 仅在指定区域内生成图形,常用于局部版图填充 / 规则适配 |

| Browse region Mapping... | 导入区域映射配置文件,定义不同区域的图形生成规则 |

- Voltage Dependent Rules 配置电压相关的DRC/布线规则,高压工艺中按电压等级设置不同间距/宽度约束

9. Window 界面

-

Assistants:辅助工具管理,可开启 / 关闭各类辅助面板(如 DRC 错误列表、网表浏览器、属性窗口),快速调出或隐藏常用工具。 -

Toolbars:工具栏设置,自定义界面顶部 / 侧边的快捷工具栏,可添加、移除或调整工具按钮,适配个人操作习惯。 -

Workspaces:工作区管理,保存、加载或切换不同的界面布局预设(如布线模式、验证模式、调试模式),一键恢复常用工作环境。 -

Tabs:标签页管理,设置窗口标签的显示方式、分组或合并选项卡,方便在多个设计窗口间切换。 -

Copy Window:复制当前窗口,创建一个与当前设计视图相同的独立窗口,便于同时查看设计的不同部分或对比修改前后的效果。

10. Floorplan 界面

-

Generate Physical Hierarchy...:生成物理层次结构,将逻辑层次映射为物理分区,为模块级布局布线提供基础。 -

Auto Generate Hierarchy...:自动生成物理层次,根据网表和约束自动创建分区,提升大规模设计的规划效率。 -

Reinitialize...:重新初始化 Floorplan,重置物理规划参数,常用于设计早期调整尺寸、宽高比或 I/O 分布。 -

I/O Placer:I/O 引脚布局工具,用于规划芯片周边的输入输出引脚位置、间距与顺序,适配封装需求。 -

Block Place:宏模块 / IP 块布局工具,手动或自动放置大型硬宏、IP 模块,优化布线通道与时序路径。 -

Soft Block Update:软模块更新工具,同步软模块的边界、引脚位置或形状修改,确保与顶层 Floorplan 的一致性。 -

Pin Planner...:引脚规划器,集中管理模块 / IP 的引脚位置,优化引脚分布以减少布线拥塞。 -

Pin Optimization...:引脚优化工具,自动调整引脚位置,减少跨模块走线长度,改善时序与布线资源占用。 -

Pin Checker...:引脚检查工具,验证引脚间距、方向与 DRC / 封装规则的合规性,提前发现潜在问题。 -

Pin Group Guides:引脚分组引导工具,为总线、差分对或电源引脚设置分组约束,指导自动布局布线。 -

Pin Tool...:通用引脚编辑工具,支持手动创建、移动、修改引脚属性,适配特殊布局需求。 -

Load Physical View...:加载物理视图,导入模块或 IP 的物理版图数据,用于协同规划与布线。 -

Connectivity:连接性检查工具,验证模块间、引脚间的连接关系,确保逻辑与物理的一致性。 -

Label Update...:标签更新工具,同步引脚、模块或网络的文本标签,便于后续调试与文档生成。 -

Block Annotations...:模块注释工具,添加模块边界、约束区域或文本说明,辅助团队协作与设计沟通。 -

Floorplan Global Options...:Floorplan 全局设置,配置芯片尺寸、宽高比、布线层、电源环 / 地环参数等核心物理规划约束。

11. Place界面

-

Pin Placement...:引脚布局工具,用于自动或手动放置模块 / 芯片的 I/O 引脚,优化引脚分布以减少布线拥塞、匹配封装需求。 -

Update Placement Status:更新布局状态,刷新并同步当前布局的状态信息(如已放置 / 未放置单元、拥塞情况),为后续优化或布线提供准确数据。 -

Snap Pins...:引脚吸附工具,将引脚自动对齐到指定网格、轨道或模块边界,确保引脚位置符合工艺规则与布线要求。 -

Custom Digital:自定义数字布局子菜单,包含手动放置、局部优化、约束驱动布局等高级功能,适配特殊模块或关键路径的布局需求。 -

Modgen:模块生成子菜单,用于生成标准单元阵列、寄存器堆、存储器等结构化模块,支持参数化配置与快速实例化。

12. Route 界面

-

Design Setup...:布线前的设计设置,用于配置布线层、间距规则、电源 / 地网络、约束条件等基础参数,是整个布线流程的前提。 -

Route Flow:布线流程管理,提供从全局布线到详细布线的完整自动化流程,支持按步骤执行或一键式运行。 -

Routability Check:可布性检查工具,提前分析设计的布线资源、拥塞情况与 DRC 冲突,预判布线瓶颈并给出优化建议。 -

Power Routing...:电源布线工具,用于创建和优化电源 / 地网络(如电源环、电源条、过孔阵列),是电源完整性设计的核心入口。 -

Automatic Routing:自动布线子菜单,包含全局布线、详细布线、差分对布线、总线布线等功能,实现信号网络的自动连接。 -

Optimization:布线优化工具,用于调整线长、减少串扰、改善时序与电源噪声,同时修复布线过程中产生的 DRC / 时序违规。 -

Fix Violations:违规修复工具,自动处理布线产生的 DRC 错误、天线效应、时序违例等问题,减少手动调试成本。 -

Tie Shield:接地 / 电源保护工具,为高速信号添加屏蔽线,减少串扰与电磁干扰,提升信号完整性。 -

Delete Routing:布线删除工具,可按网络、区域或类型选择性删除布线,支持部分重布线与迭代优化。 -

Routing Scripts...:布线脚本管理,用于加载、编辑或运行自定义布线脚本,实现自动化流程与特殊布线需求。

13. Concurrent 界面

1. Initialize...

- 作用:初始化设计分区环境,为当前设计启用分区协同模式。

- 用途:创建 / 加载分区配置,为后续定义分区做准备。

2. Define Design Partition...

- 作用:手动定义分区边界、分配分区归属(谁负责哪个分区)。

- 用途:把整个版图划分为多个矩形 / 自定义区域,分配给不同工程师并行开发。

3. Merge...

- 作用:合并多个分区的修改,将不同工程师的编辑结果同步到主设计。

- 用途:多人编辑完成后,把所有分区的修改合并为完整版图。

4. Layout Configuration...

- 作用:配置分区的显示和行为,比如分区边框颜色、可见性、锁定状态。

- 用途:区分不同分区,避免多人编辑时误操作其他分区。

5. Clear All Design Partitions...

- 作用:清除所有分区定义,恢复为无分区的单一体设计。

- 用途:分区协同完成后,清理分区信息,方便后续独立编辑。

6. View Design Partition Definition...

- 作用:查看当前所有分区的定义、边界和归属信息。

- 用途:核对分区划分,避免分区重叠或遗漏。

7. Submit for Merge / Recall...

- 作用:将当前分区的修改提交到主设计,或从主设计中召回更新。

- 用途:分区完成后提交修改,或同步其他工程师的更新。

9. Reset Design Partition View...

- 作用:重置分区视图,刷新分区的显示和状态。

- 用途:解决分区显示异常、同步延迟的问题。

10. Import Peer Design Partition...

-

作用:导入其他工程师提交的分区修改,与本地设计合并。

-

用途:多人协同时,接收并整合其他分区的修改。

14. Design Manager 界面

-

**Check Out...**对选中的库、单元或视图执行 "签出" 操作。签出后,该设计文件将从只读状态变为可编辑状态,同时锁定该版本,防止其他用户同时修改,是多人协作的基础操作。

-

**Check In...**对已修改并签出的设计执行 "签入" 操作。签入时会保存修改、更新版本号,并将文件恢复为只读状态,供其他用户访问最新版本。可添加版本注释,便于后续追溯变更原因。

-

**Cancel CheckOut...**撤销签出操作,放弃当前所有修改,将文件恢复到签出前的只读状态,不会生成新的版本。适合误操作或修改失败时的回退。

-

**Tag...**为特定版本的设计添加标签(Tag),例如 "Release v1.0""流片版" 等,方便后续快速定位和追溯关键版本,是版本管理中重要的标记手段。

-

**Update...**从版本库同步其他用户的签入更新,更新本地的设计文件。可选择更新单个单元、整个库或指定层次,确保本地环境与团队主库保持同步。

-

**Diff...**对比两个版本的设计差异,可查看原理图、版图或网表的变更细节,常用于代码评审、变更确认或问题排查。

-

**History...**查看设计文件的完整版本历史,包括每次签入 / 签出的用户、时间、修改注释和版本号,支持回溯任意历史版本。

-

Manage Hierarchy用于对设计的层次结构进行管理,支持批量签入 / 签出整个层次化设计、设置层次依赖关系,以及处理跨层次的版本同步问题,是大规模 SoC / 混合信号设计中必不可少的功能。

15 Palette 界面

如下功能,请选择在Palette的任意位置邮件,既可以调出下面的功能;

1. MPT Support

-

全称:Multi-Part/Color Technology Support(多色图层支持,ICADV12.3+ 特性)

-

作用:启用后,层列表会显示带颜色(mask1/2/3...)和锁定状态的 LPP,支持绘制带独立颜色、锁定属性的图形,常用于复杂工艺、定制化显示资源管理。

-

图中已勾选,说明当前会话已开启 MPT 模式。但是基本上打开没什么影响,可以在设计中直接关闭。

2. Desynchronize Window

-

作用:解除窗口上下文同步。同工艺文件的版图窗口默认共享同一 Palette 上下文,解除同步后,当前窗口的层显示 / 设置不再与其他窗口联动,可独立控制。

-

下方的

PDk_XMC_DTC_2P0是当前绑定的工艺 / PDK 上下文名称。

3. Layer Set(带子菜单)

-

作用:层集合管理核心入口,支持创建 / 保存 / 导入 / 导出层分组,是你之前问到的 LayerSet 的主要操作入口。

-

常用子命令:

-

Save / Save As:保存 / 另存层集合

-

Reload:重载层集合配置

-

Import / Export:跨工程 / 电脑共享层集合文件

-

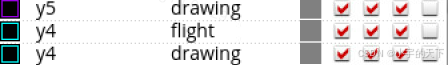

4. Edit Valid Layers

- 作用:编辑层的有效性状态,在列表中显示

v(valid)列,可临时标记层为有效 / 无效,常用于调试工艺文件、过滤非法 LPP。

5. Edit Layer Set Members

- 作用:编辑当前激活层集合的成员,显示

m(member)列,勾选 / 取消勾选即可快速将 LPP 加入 / 移出当前层集合,是创建自定义 LayerSet 的核心步骤。

6. Discard Edit

- 作用:撤销对层集合成员 / 有效性的所有未保存修改,恢复到上次保存的状态,图中该选项为灰色,说明当前无未提交的编辑操作。

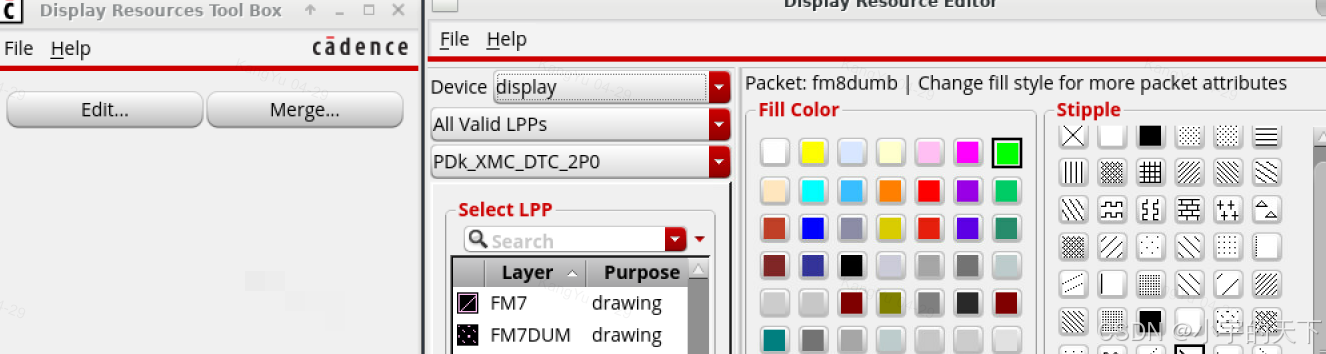

7. Edit Display Resources...

-

作用:打开显示资源编辑器,修改层的颜色、点纹、线型等显示样式,对应修改

display.drf相关配置。 -

备注:可以在该位置对层的颜色和填充形式进行修改和变更。另外一种修改层颜色和填充形式的方式为,在如下界面。

8. Load / Save(带子菜单)

-

作用:加载 / 保存显示上下文,支持三种格式:

-

LSW Info 文件:旧版 LSW 的配置文件

-

Techfile:直接读写工艺文件中的显示配置

-

GDS Number 文件:导入 / 导出 GDS 层号映射

-

-

常用于批量同步层显示设置、跨 PDK 复用配置。

9. Show Tools(带子菜单)

- 作用:显示 / 隐藏 Palette 的工具栏(如 LayerSet、Scope、Edit、Control Buttons 等),可自定义界面布局,减少冗余工具栏占用。

10. Options...

- 作用:打开 Palette 全局设置表单,配置层集合激活模式、搜索行为、列显示规则、MPT 模式等高级参数。

11. Bindkeys...

- 作用:打开快捷键编辑器,自定义 Palette 相关操作的快捷键(如切换层集合、开关可见性),提升操作效率。