ARMv7-A架构通过协处理器机制扩展处理器功能,其中CP15是最核心的系统控制协处理器。以下是完整的技术详解。

一、协处理器体系结构概述

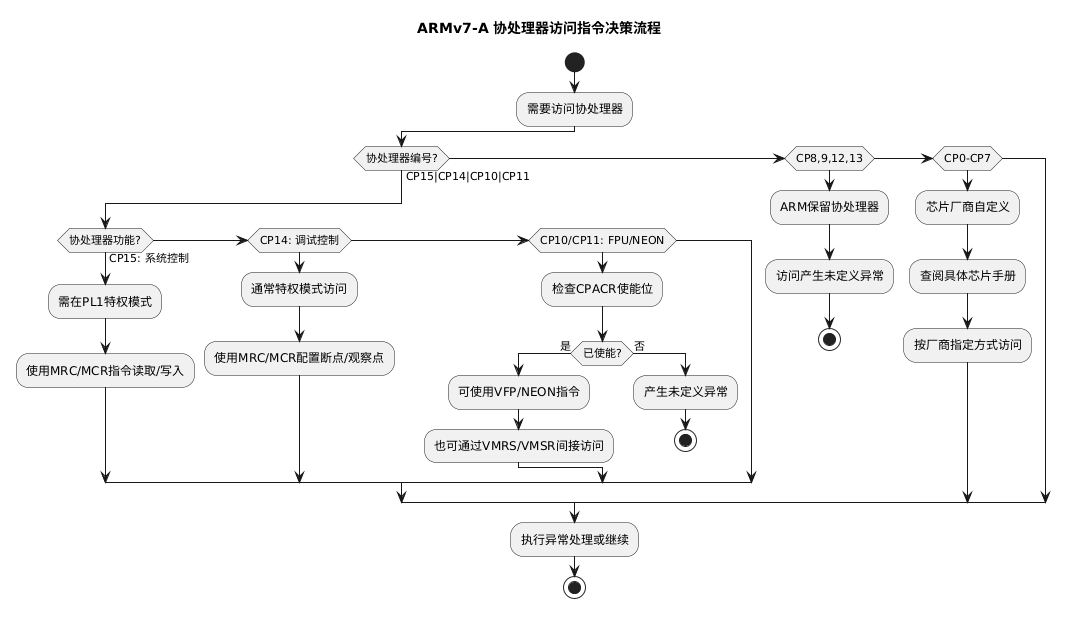

ARMv7-A架构支持最多16个协处理器,编号为CP0-CP15。各协处理器的功能分配如下:

| 协处理器 | 功能描述 | 访问权限 |

|---|---|---|

| CP15 | 系统控制协处理器 | 特权模式(PL1) |

| CP14 | 调试控制、Thumb执行环境、Jazelle Java加速 | 特权模式 |

| CP10, CP11 | 浮点运算(VFP)和高级SIMD(NEON)支持 | 可配置 |

| CP8, CP9, CP12, CP13 | ARM保留,供将来使用 | 访问产生未定义异常 |

| CP0-CP7 | 厂商自定义功能 | 由实现定义 |

协处理器访问控制:通过CP15的CPACR(Coprocessor Access Control Register)寄存器控制CP0-CP13在不同特权级的访问权限:

0b00:拒绝所有访问0b01:仅PL1特权模式可访问0b11:所有特权级均可访问

CP15:系统控制协处理器(核心)

CP15是最重要的系统控制协处理器,负责管理ARMv7-A处理器的核心系统资源。掌握CP15是进行底层系统开发、操作系统移植和性能优化的基础。

CP14:调试与执行环境控制

CP14主要用于调试功能、Thumb执行环境和Java Jazelle技术控制。

主要功能:

- 硬件调试控制:断点单元(Breakpoint Unit)、观察点单元(Watchpoint Unit)配置

- Thumb执行环境(ThumbEE)控制

- Jazelle DBX:Java字节码直接执行支持

由于调试功能通常通过JTAG/SWD等调试接口配置,直接操作CP14的场景较少。

CP10与CP11:浮点与SIMD协处理器

CP10和CP11共同工作,提供ARMv7-A的浮点运算和向量处理能力。

| 协处理器 | 功能 | 关键特性 |

|---|---|---|

| CP10 | 浮点单元控制 | 控制FPU状态和配置 |

| CP11 | NEON SIMD引擎 | 高级单指令多数据流扩展 |

技术特性:

- VFPv3:单精度/双精度浮点运算

- NEON:128位SIMD指令,并行处理图像、音频等数据

- 通过CPACR(CP15 c1)控制CP10/CP11访问权限

使能NEON/FPU

; 使能CP10和CP11访问

MRC p15, 0, r0, c1, c0, 2 ; 读CPACR

ORR r0, r0, #(0xF << 20) ; CP10/CP11设为0b11(完全访问)

MCR p15, 0, r0, c1, c0, 2 ; 写回CPACR

; 使能VFP单元

MOV r0, #0x40000000

VMSR FPEXC, r0 ; VFP使能(协处理器指令)保留协处理器(CP8,9,12,13)

CP8、CP9、CP12、CP13被ARM保留用于未来扩展使用 。访问这些协处理器会产生未定义异常(Undefined Instruction Exception)。

CP0-CP7:厂商自定义协处理器

CP0-CP7可以由芯片厂商自定义功能。常见用途包括:

- 额外的内存管理/保护功能

- 电源管理和时钟控制

- 特定外设控制寄存器映射

实际功能取决于具体芯片实现,需查阅特定芯片技术手册。

二、CP15系统控制协处理器详解

CP15是最重要的系统控制协处理器,负责管理ARMv7-A处理器的核心系统资源。掌握CP15是进行底层系统开发、操作系统移植和性能优化的基础。

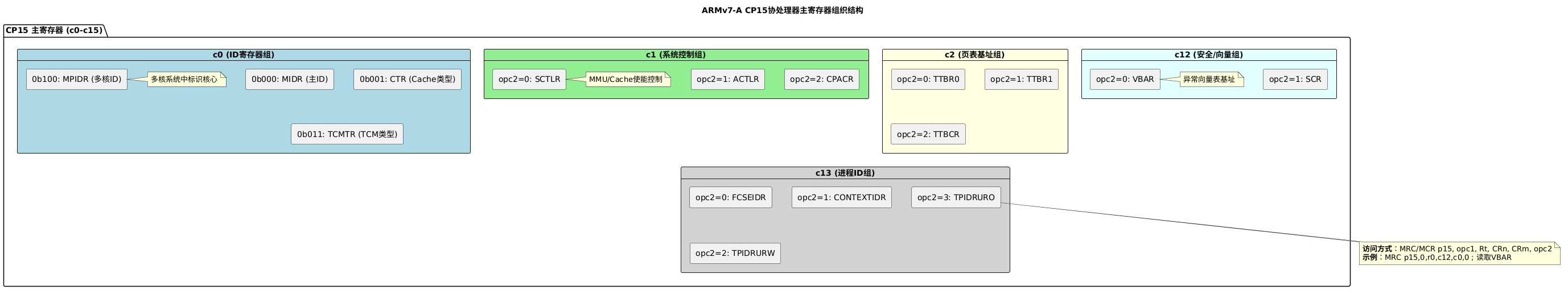

2.1 CP15寄存器组织架构

CP15提供了16个32位主寄存器 (c0-c15),每个主寄存器可能对应多个物理寄存器,通过{CRn, opc1, CRm, opc2}四元组唯一标识。

ARMv7-A架构通过四元组 {CRn, opc1, CRm, opc2}唯一标识CP15协处理器内部的每个物理寄存器。这种分层编码设计扩展了可访问寄存器的数量,使ARM能够在有限的指令编码空间内支持丰富的系统控制功能。

| 字段 | 名称 | 位数 | 取值范围 | 功能描述 |

|---|---|---|---|---|

| CRn | 主寄存器编号 | 4位 | 0-15 | 标识主要功能组,对应c0-c15 |

| opc1 | 操作码1 | 3位 | 0-7 | 不同安全状态或模式的寄存器变体 |

| CRm | 辅助寄存器编号 | 4位 | 0-15 | 同一功能组内的细分寄存器 |

| opc2 | 操作码2 | 3位 | 0-7 | 进一步细分同一个CRn/CRm组合 |

这相当于一个四维数组访问 :register[CRn][opc1][CRm][opc2]。

指令中的位置:

MRC p15, <opc1>, <Rt>, <CRn>, <CRm>, <opc2>

MCR p15, <opc1>, <Rt>, <CRn>, <CRm>, <opc2>常见寄存器的四元编码

- 主ID寄存器组 (CRn=c0)

| 寄存器 | CRn | opc1 | CRm | opc2 | 功能 |

|---|---|---|---|---|---|

| MIDR | 0 | 0 | 0 | 0 | 主ID寄存器 |

| MPIDR | 0 | 0 | 0 | 5 | 多核处理器ID |

| CTR | 0 | 0 | 0 | 1 | Cache类型寄存器 |

| TCMTR | 0 | 0 | 0 | 2 | TCM类型寄存器 |

| TLBR | 0 | 0 | 0 | 3 | TLB类型寄存器 |

- 系统控制寄存器组 (CRn=c1)

| 寄存器 | CRn | opc1 | CRm | opc2 | 功能 |

|---|---|---|---|---|---|

| SCTLR | 1 | 0 | 0 | 0 | 系统控制寄存器 |

| ACTLR | 1 | 0 | 0 | 1 | 辅助控制寄存器 |

| CPACR | 1 | 0 | 0 | 2 | 协处理器访问控制 |

- 内存管理单元寄存器组 (CRn=c2)

| 寄存器 | CRn | opc1 | CRm | opc2 | 功能 |

|---|---|---|---|---|---|

| TTBR0 | 2 | 0 | 0 | 0 | 页表基址寄存器0 |

| TTBR1 | 2 | 0 | 0 | 1 | 页表基址寄存器1 |

| TTBCR | 2 | 0 | 0 | 2 | 页表控制寄存器 |

- 异常和向量表寄存器组 (CRn=c12)

| 寄存器 | CRn | opc1 | CRm | opc2 | 功能 |

|---|---|---|---|---|---|

| VBAR | 12 | 0 | 0 | 0 | 向量表基址寄存器 |

| SCR | 12 | 0 | 0 | 1 | 安全配置寄存器 |

| HVBAR | 12 | 4 | 0 | 0 | 虚拟化向量表基址(Hyp模式) |

MVBAR (Monitor Vector Base Address Register) :对于安全监视器(Secure Monitor)模式,使用opc1=0、CRm=0、opc2=1访问SCR,使用opc1=0、CRm=6、opc2=0访问MVBAR。

; 安全监视器模式访问示例

MRC p15, 0, r0, c12, c6, 0 ; 读MVBAR

MCR p15, 0, r0, c12, c6, 0 ; 写MVBAR2.2 CP15主寄存器功能总览

主寄存器c0-c15的功能分配:

| 主寄存器 | 功能域 | 关键物理寄存器示例 |

|---|---|---|

| c0 | ID寄存器 | MIDR(主ID), MPIDR(多核ID), TCMTR, TLBR |

| c1 | 系统控制 | SCTLR(系统控制), ACTLR(辅助控制), CPACR(协处理器访问) |

| c2 | 内存保护/页表基址 | TTBR0, TTBR1(页表基址), TTBCR(页表控制) |

| c3 | 域访问控制 | DACR |

| c5, c6 | 内存系统错误 | DFSR/IFSR(异常状态), DFAR/IFAR(异常地址) |

| c7 | Cache维护 | 各种Cache操作寄存器(I/D-Cache使能/清零) |

| c8 | TLB维护 | TLB操作寄存器 |

| c9 | 性能监视/缓存控制 | PMU寄存器, L2Cache控制 |

| c10 | 内存重映射/TLB控制 | PRRR, NMRR(内存属性重映射) |

| c11 | TCM/DMA | TCM区域配置 |

| c12 | 安全扩展/向量表 | VBAR(异常向量基址), SCR(安全配置) |

| c13 | 进程/上下文ID | CONTEXTIDR, TPIDRURW, TPIDRURO |

| c14 | 通用定时器 | CNTFRQ, CNTPCT |

| c15 | 实现定义 | CBAR(外设配置基址,厂商实现) |

2.3 关键寄存器详解

1. MIDR - 主ID寄存器(Main ID Register)

只读寄存器,标识处理器核类型和版本:

MRC p15, 0, r0, c0, c0, 0 ; 读取MIDR到r02. SCTLR - 系统控制寄存器(System Control Register)

最重要的控制寄存器,控制MMU、Cache、对齐检查等:

关键控制位:

| 位域 | 名称 | 功能 |

|---|---|---|

| bit0 | M | MMU使能 |

| bit1 | A | 对齐检查使能 |

| bit2 | C | D-Cache使能 |

| bit3 | B | 大小端配置 |

| bit11 | Z | 分支预测使能 |

| bit12 | I | I-Cache使能 |

; 典型配置:启用MMU和Cache

MRC p15, 0, r0, c1, c0, 0 ; 读取SCTLR

ORR r0, r0, #0x1 ; 设置M位(MMU)

ORR r0, r0, #0x4 ; 设置C位(D-Cache)

ORR r0, r0, #0x1000 ; 设置I位(I-Cache)

MCR p15, 0, r0, c1, c0, 0 ; 写回SCTLR3. TTBR0/TTBR1 - 页表基址寄存器

存储一级页表基地址,用于MMU地址转换:

; 设置TTBR0

LDR r0, =page_table_base ; 获取页表基址

MCR p15, 0, r0, c2, c0, 0 ; 写入TTBR0

; 设置TTBR1

MCR p15, 0, r0, c2, c0, 1 ; 写入TTBR1(需指定opc2=1)TTBCR - 页表控制寄存器:

| 位域 | 功能 |

|---|---|

| bit31 (EAE) | 地址扩展使能(0=32位,1=40位LPAE) |

| bits[2:0] (N) | 控制TTBR0页表大小和TTBR0/TTBR1使用策略 |

N=0:仅使用TTBR0N>0:地址高位为0使用TTBR0,否则使用TTBR1

4. VBAR - 向量表基址寄存器(Vector Base Address Register)

用于重定位异常向量表:

; 设置向量表基址(需32字节对齐)

LDR r0, =exception_table_base

MCR p15, 0, r0, c12, c0, 0 ; 写入VBAR5. CPACR - 协处理器访问控制寄存器

控制CP10-CP11(浮点/NEON)和CP14的访问:

; 使能FPU/NEON访问(PL0和PL1均可访问)

MRC p15, 0, r0, c1, c0, 2 ; 读取CPACR

ORR r0, r0, #(0xF << 20) ; 设置cp10/cp11为0b11

MCR p15, 0, r0, c1, c0, 2 ; 写回CPACR2.4 访问流程

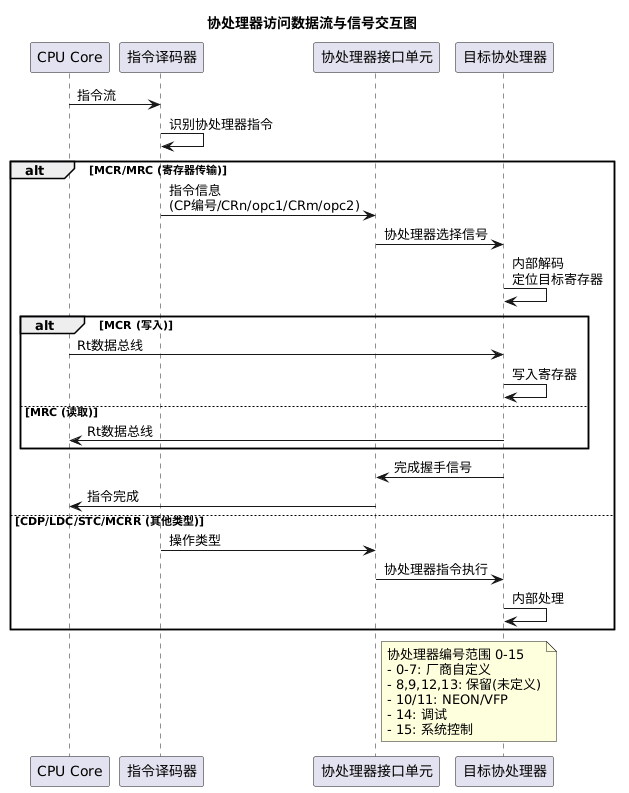

三、CP15协处理器访问指令

ARM支持五类协处理器指令:

| 指令类型 | 功能 | 示例 |

|---|---|---|

| MCR | ARM寄存器 → 协处理器寄存器 | MCR p15, 0, r0, c1, c0, 0 |

| MRC | 协处理器寄存器 → ARM寄存器 | MRC p15, 0, r0, c0, c0, 0 |

| MCRR/MRRC | ARM双寄存器传输(64位) | 用于64位寄存器访问 |

| LDC/STC | 内存 ↔ 协处理器 | 批量数据传输 |

| CDP | 协处理器数据处理 | 内部运算指令 |

变体后缀"2"(如MCR2)是无条件执行版本,条件码域固定,用于调试场景。

3.1 MRC - 从协处理器读数据到ARM寄存器

指令格式:

MRC{cond} p15, <opc1>, <Rt>, <CRn>, <CRm>{, <opc2>}字段说明:

| 参数 | 描述 | 取值范围 |

|---|---|---|

cond |

执行条件(可选) | EQ, NE, 等条件码 |

p15 |

CP15协处理器标识 | 固定 |

opc1 |

协处理器操作码 | 0-7 |

Rt |

ARM目标寄存器 | R0-R14(不能是PC) |

CRn |

CP15主寄存器 | c0-c15 |

CRm |

辅助寄存器 | c0-c15,无附加信息时设为c0 |

opc2 |

二级操作码 | 0-7,默认为0 |

示例:

; 读主ID寄存器

MRC p15, 0, r0, c0, c0, 0

; 读系统控制寄存器

MRC p15, 0, r0, c1, c0, 0

; 读MPIDR(多核ID)

MRC p15, 0, r0, c0, c0, 5

; 读VBAR

MRC p15, 0, r0, c12, c0, 0

; 读CBAR(Cortex-A7特有,访问GIC基址)

MRC p15, 4, r0, c15, c3, 0 ; opc1=4,在Hyp模式下访问3.2 MCR - 从ARM寄存器写数据到协处理器

指令格式:

MCR{cond} p15, <opc1>, <Rt>, <CRn>, <CRm>{, <opc2>}示例:

; 写SCTLR(系统控制寄存器)

MCR p15, 0, r0, c1, c0, 0

; 写VBAR(向量表重定位)

LDR r0, =0x80010000

MCR p15, 0, r0, c12, c0, 0

; 写TTBR0(页表基址)

MCR p15, 0, r0, c2, c0, 0

; 刷新TLB

MCR p15, 0, r0, c8, c7, 0 ; 无效化TLB3.3 带"2"后缀的协处理器指令变体

ARMv7-A还提供了带2后缀的协处理器指令版本(MRC2/MCR2等),它们使用无条件执行编码(cond域固定为0b1111):

| 指令 | 编码特征 | 限制 |

|---|---|---|

| MRC2 | 无条件执行 | cp10/cp11访问未定义 |

| MCR2 | 无条件执行 | cp10/cp11访问未定义 |

| MRRC2 | 64位传输 | 用于双字传输 |

| MCRR2 | 64位传输 | 用于双字传输 |

实际用途:MRC2/MCR2主要用于调试场景和Hyp模式下访问CP14调试寄存器。

四、VMSA vs PMSA

ARMv7-A的内存系统架构分为两种:

| 架构 | 全称 | 核心组件 | 典型应用 |

|---|---|---|---|

| VMSA | Virtual Memory System Architecture | MMU + 页表 | 运行Linux/Android |

| PMSA | Protected Memory System Architecture | MPU | 裸机/RTOS |

VMSA下CP15寄存器侧重 :TTBR0/1, TTBCR, DFSR/DFAR等

PMSA下CP15寄存器侧重:MPU区域配置寄存器

五、重要使用场景

5.1 系统启动初始化序列

典型ARMv7-A处理器启动时的CP15初始化流程:

; 第1步:读取处理器ID验证

MRC p15, 0, r0, c0, c0, 0

LDR r1, =0x410FC090 ; 特定处理器ID

CMP r0, r1

; 第2步:禁用MMU和Cache

MRC p15, 0, r0, c1, c0, 0

BIC r0, r0, #0x1 ; 清除M位(MMU)

BIC r0, r0, #0x4 ; 清除C位(D-Cache)

BIC r0, r0, #0x1000 ; 清除I位(I-Cache)

MCR p15, 0, r0, c1, c0, 0

; 第3步:设置向量表重定位

LDR r0, =_vector_start

MCR p15, 0, r0, c12, c0, 0

; 第4步:设置页表(如果使用MMU)

; 初始化页表内存 ...

LDR r0, =page_table_base

MCR p15, 0, r0, c2, c0, 0

MCR p15, 0, r0, c2, c0, 1 ; TTBR1同基址5.2 上下文切换时的CP15保存/恢复

多任务操作系统中,需要保存/恢复的CP15关键状态:

; 保存当前任务状态

MRC p15, 0, r0, c13, c0, 1 ; 读CONTEXTIDR

STR r0, [sp, #OFF_ID]

MRC p15, 0, r0, c13, c0, 2 ; 读TPIDRURW

STR r0, [sp, #OFF_TPIDR]

; 恢复新任务状态

LDR r0, [sp, #OFF_ID]

MCR p15, 0, r0, c13, c0, 1

LDR r0, [sp, #OFF_TPIDR]

MCR p15, 0, r0, c13, c0, 25.3 Cache/TLB维护操作

CP15的c7和c8寄存器用于Cache和TLB维护:

; 清零整个D-Cache

MOV r0, #0

MCR p15, 0, r0, c7, c5, 0 ; 清零I-Cache

MCR p15, 0, r0, c7, c10, 4 ; DSB指令等效

; 无效化TLB(多核系统)

MCR p15, 0, r0, c8, c3, 0 ; TLB无效化所有ASID(Inner Shareable)

; 数据同步屏障

MCR p15, 0, r0, c7, c10, 5 ; DMB

MCR p15, 0, r0, c7, c10, 4 ; DSB六、限制与注意事项

- 特权级限制:CP15大多数字段必须在PL1或更高特权模式访问;用户态(PL0)访问会产生未定义异常。

- 指令限制 :所有

CDP、LDC、STC、MCRR、MRRC指令访问CP15都会产生未定义异常。 - ARMv7-R差异:ARMv7-R使用PMSA而非VMSA,CP15寄存器定义有所不同。

- 安全扩展影响:启用TrustZone安全扩展时,安全世界(secure world)和非安全世界(non‑secure world)拥有独立的CP15状态的某些部分。

- VBAR对齐要求:VBAR寄存器要求向量表地址32字节对齐。

七、总结

CP15协处理器是ARMv7-A系统控制的核心,通过MRC/MCR指令提供对MMU、Cache、TLB、异常处理等关键功能的配置能力。

核心要点:

- 寄存器由

{CRn, opc1, CRm, opc2}四元组唯一识别 - MRC/MCR是最常用的访问指令

- 系统启动时必须配置SCTLR、TTBR、VBAR等关键寄存器

- 多核系统需注意MPIDR区分核心、TLB无效化需指定shareability