5.3.4 Delay Fault Testing

上面讨论的BIST pattern生成技术主要针对的是structural faults(比如说stuck-at faults和bridging faults),用one-pattern vectors就行,对于delay faults这种需要two-pattern vectors的故障,上面的方法就覆盖不到了。

structural fault用到的向量是exhaustive one-pattern set of 2^n。在n-input CUT中检测延迟故障就需要exhaustive two-pattern set of 2^n(2^n −1),那就意味着要用到2n或者更多stages的test pattern generator (TPG),有2n stages的maximum-length LFSR叫做double-length LFSR。

LFSR可以用2^2n-1个向量exhaustively检测CUT,但是仍然存在一个因为设计中的冒险发生的潜在问题造成测试无效:

- 当电路的一个或多个输入发生变化的时候,可能会造成测试无效或冒险

- 在at-speed BIST中能耗可能会超出芯片或者封装的能耗等级,平均能耗的升高可能会造成芯片发热,而且升高的峰值功率可能会造成与噪声相关的失效

这个问题,生成single-input change (SIC)或者one-transition patterns(应该是指跳变沿只有一个的pattern)可以解决。

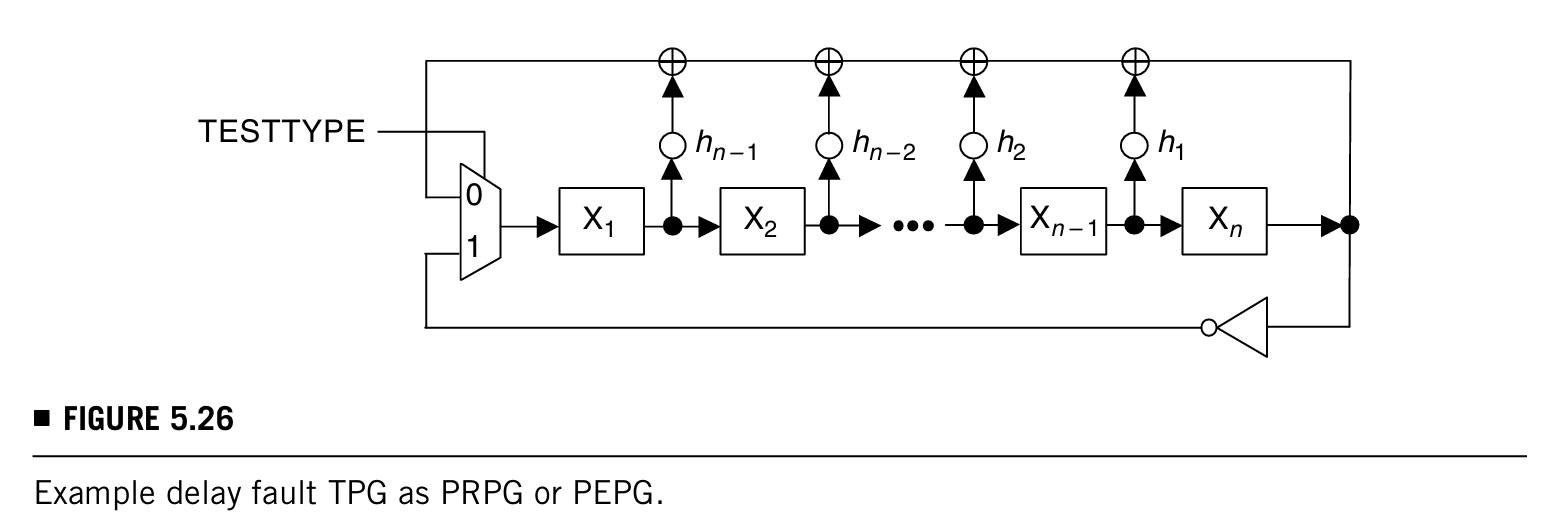

由a binary counter和maximum-length LFSR组成的Gray code counter,另外还有Johnson counter和ring counter都是因此目的被广泛应用,一个n-input CUT的delay fault TPG例子如下图:

标准的maximum-length LFSR可以循环2^n-1个states,n-bit Johnson counter可以生成2n个one-transition patterns,通过合适地控制TESTTYPE这个控制信号,这个delay fault TPG可以为delay fault testing生成2n(2^n-1)个one-transition patterns,为stuck fault testing生成2^n-1个patterns。

5.3.5 Summary

虽然exhaustive和pseudo-exhaustive testing有很多优点,但是pseudo-random testing仍然是BIST pattern generation最实际和最常用的一种技术,但又因为它的故障覆盖率较低,所以对于关乎生命或者重要人物的应用,需要想办法提升故障覆盖率,比如:

- 插入测试点

- 内嵌deterministic patterns

这些会在5.6节中详细描述。

5.4 OUTPUT RESPONSE ANALYSIS

之前我们讨论的逻辑和故障仿真都是输出响应从电路出来和测试机对比,但是BIST操作下,不可能实现on-chip, on-board, or in-system的位对位的比较了,这时候就得用上output response analysis技术,把输出响应压缩成一个signature和golden signature对比,这个操作可以embedded on-chip,也可以stored off-chip。

讲到压缩,要分清楚两个概念:

- Compaction(有损的):极大地降低原始电路的响应位数,有些信息会丢失。

- Compression(无损的):也可以降低原始电路的响应位数,但是没有信息会丢失,原始的输出响应可以从compressed sequence重新生成出来。

因为output response analysis技术输出的响应会丢失信息,所以它的响应也被叫做output response compaction。但是其实现在学术界对这两个词的使用也没有严格区分。

这一节讲三种output response compaction技术:

- ones count testing

- transition count testing

- signature analysis:讲的最细,因为用的最广泛

在应用compaction时,需要注意两个问题:

- faulty和fault-free的signatures应该是不同的,如果相同那么就是有些故障没有检测出来,这叫error masking,错误的输出响应就是正确的响应的alias

- output responses中不能含有unknown (X)值(用到5.2中的X-bounding技术)

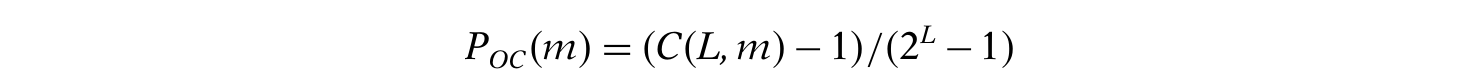

5.4.1 Ones Count Testing

假设CUT只有一个输出,而且这个输出是一串L比特的stream。让fault-free output R0位为{r0 r1 r2...rL-1},The ones count test技术只需要一个计数器得到这个stream中的1的个数。比如R0 ={0101100},OC(R0) = 3,如果fault f1出现,使R1 ={1100110},那么OC(R1 )= 4;如果fault f2出现,使R2 ={0101010},那么OC(R2)= 3,这种故障就检测不出来了。

让fault-free signature为m,有C(L,m)种可能的方式在L个比特的stream中出现m个1,假设所有的faulty sequences出现在输出响应的概率是相同的,那么有m个1的ones count testing的aliasing probability或者叫masking probability就可以用下式表达:

比如m =OC(R0) = 3,L = 7,那么Poc(m) = 34/127 = 0.27。

下图展示的就是ones count test circuit用T个pattern测试CUT的例子,The number of stages in the counter design大于等于log 2(L +1):

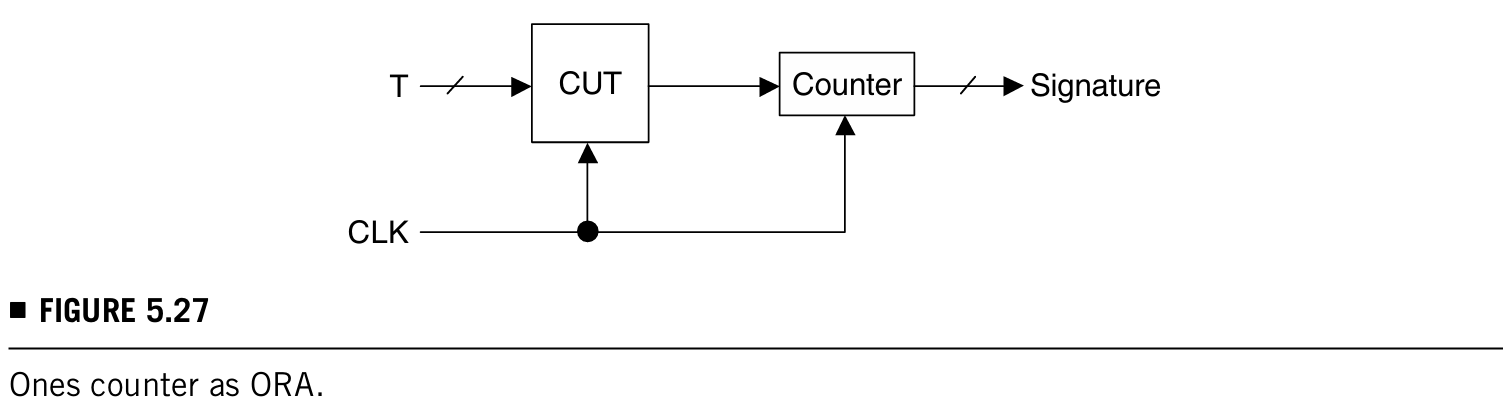

5.4.2 Transition Count Testing

这个理论和ones count testing异曲同工,不同的是,这里的signature指的是0-to-1和1-to-0的跳变,这个技术的框架图如下,就是在ones counter的基础上加了一个D flip-flop 和an XOR gate:

同样的用上面的例子,比如R0 ={0101100},TC(R0) = 4,假设D flip-flop的初始状态r−1是0,如果fault f1出现,使R1 ={1100110},那么OC(R1 )= 4,这种故障就检测不出来了;如果fault f2出现,使R2 ={0101010},那么OC(R2)= 6。

让fault-free signature为m,L比特的序列R0如果初始状态r0 = 0,那么就有L-1种可能的跳变,如果序列中有m个跳变那么序列就有C(L-1,m)种可能,但是初始态r0也有可能是1,那么就一共有2C(L-1,m)种可能,假设所有的faulty sequences出现在输出响应的概率是相同的,那么有m个跳变的transition count testing的aliasing probability或者叫masking probability就可以用下式表达:

还是用之前的例子,比如m =TC(R0) = 4,L = 7,那么PTc(m) = 29/127 = 0.23。

The number of stages in the counter design大于等于log 2(L +1)。

5.4.3 Signature Analysis

Signature analysis是当今response compaction中最流行的技术,它的框架是基于循环冗余校验cyclic redundancy checking (CRC)被发展出来的,后来1977年把它商业化提名为signature analysis,这一节讨论两种signature analysis架构:

- serial signature analysis:压缩单输出CUT的响应

- parallel signature analysis:压缩多输出CUT的响应

5.4.3.1 Serial Signature Analysis

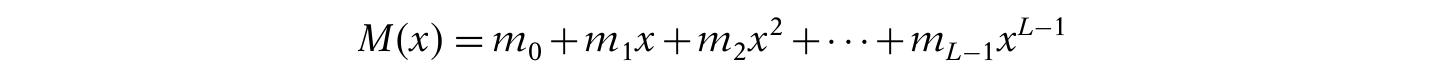

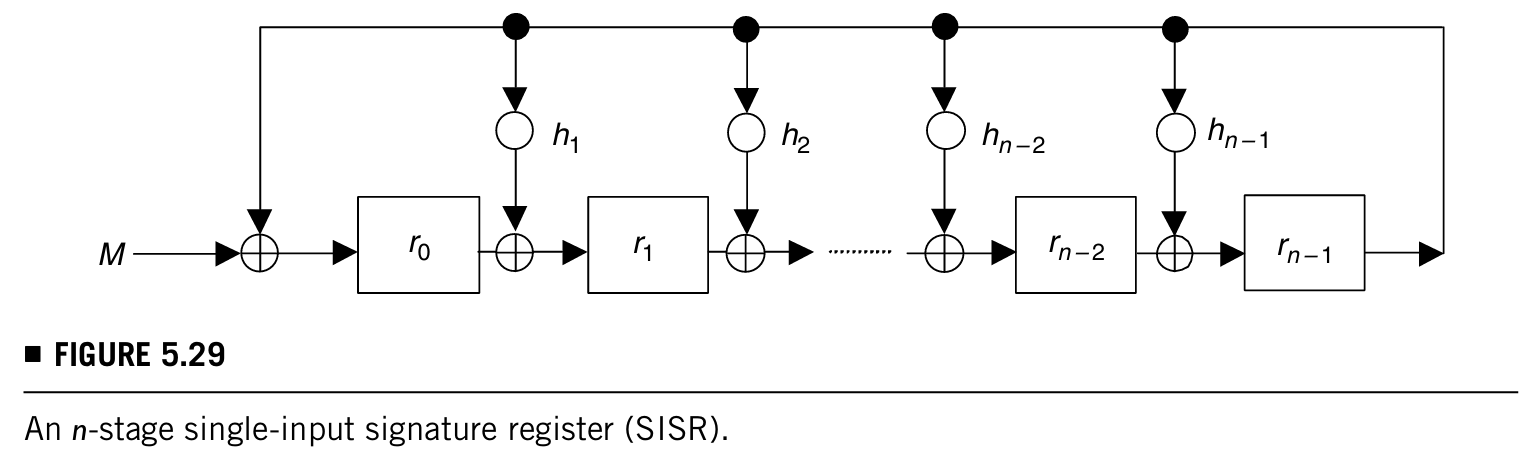

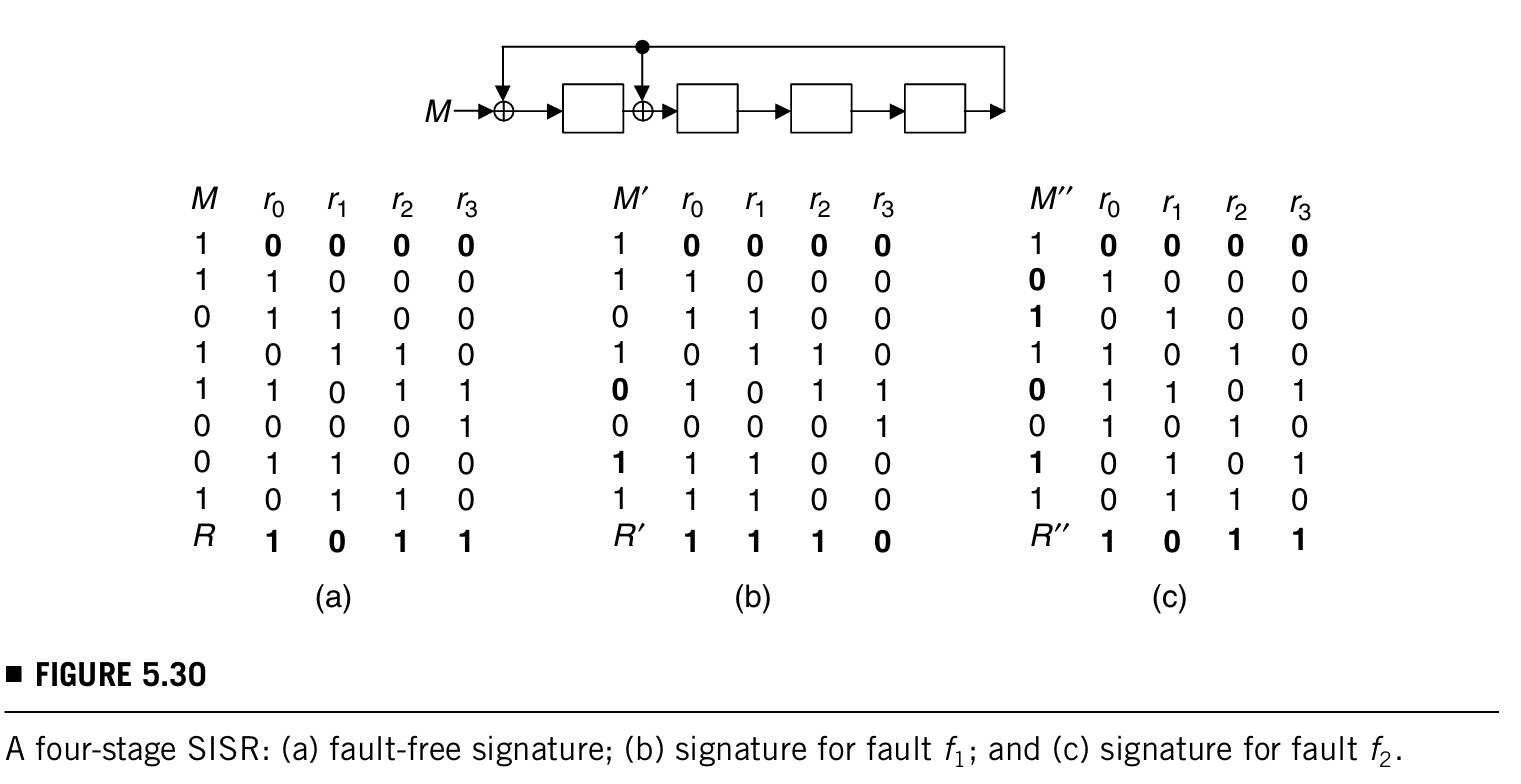

下图展示的是一个n-stage single-input signature register (SISR),在输入额外加上了XOR gate,将L比特的输出序列M压缩到modular LFSR,M = {m0 m1 m2 ...mL−1},并且有如下定义:

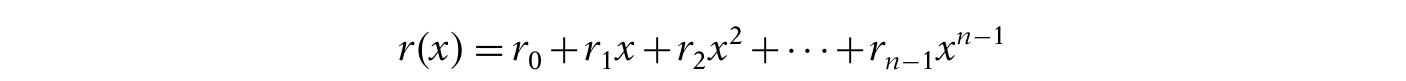

SISR的内容(或者说是余数)R就是{r0 r1 r2...rn−1},或者可以用下式表达:

SISR本质上就是一个CRC code generator或者说是cyclic code checker。如果说modular LFSR的特征多项式是f(x),那么SISR的多项式就可以被表示成:

SISR的最后状态也就是signature是多项式余数r(x),以下图为例,一个four-stage SISR,并且f(x)= 1 + x + x^4:

假设M = {10011011},那么M(x) = 1 + x^3 + x^4 + x^6 + x^7,用多项式除法就可以得到q(x) = x^2 + x^3和r(x) = 1 + x^2 + x^3或者R = {1011},余项{1011}就是从上图a中SISR(以{0000}为starting pattern (seed))发展出来的signature。

看图b,假设故障f1的错误输出流为M' = {11001011},或者表达成M(x) = 1 + x + x^4 + x^6 + x^7,用多项式除法就可以得到q'(x) = x^2 + x^3和r'(x) = 1 + x + x^2或者R' = {1110},因为最后的signature是R' = {1110},与fault-free signature R = {1011}不同,所以f1能被检测到。

看图c,故障f2,一样的推导方法,R'' = {1011},和fault-free signature相同,所以f2检测不出来。

像上面图c这种故障检测不出来的情况就是SISR的fault detection or aliasing问题,可以用一个非故障序列M和故障序列的M'的error sequence E或者叫error polynomial E(x)很好的理解:E = M'+M或者表达为:

如果E(x)不能除开f(x),那么这个故障就能被检测到,如果能除开,那么这个故障就不能被检测到,具体的看原文解析。

假设SISR包含了n个stages,对于给定的L比特的序列,L>n的话,就会有2^(L-n)种可能的n-bit signature,其中一个就是正确的signature,因为在L-bit的数据流中有2^L-1种错误的序列,那么对于用n-stage SISR的serial signature analysis (SSA) 而言,它的aliasing probability可以用下式表达:

如果L远远大于n,那么P_SSA(n)约等于2^-n,比如说n = 20的时候,P_SSA(n) < 2^-20 = 0.0001%。

5.4.3.2 Parallel Signature Analysis

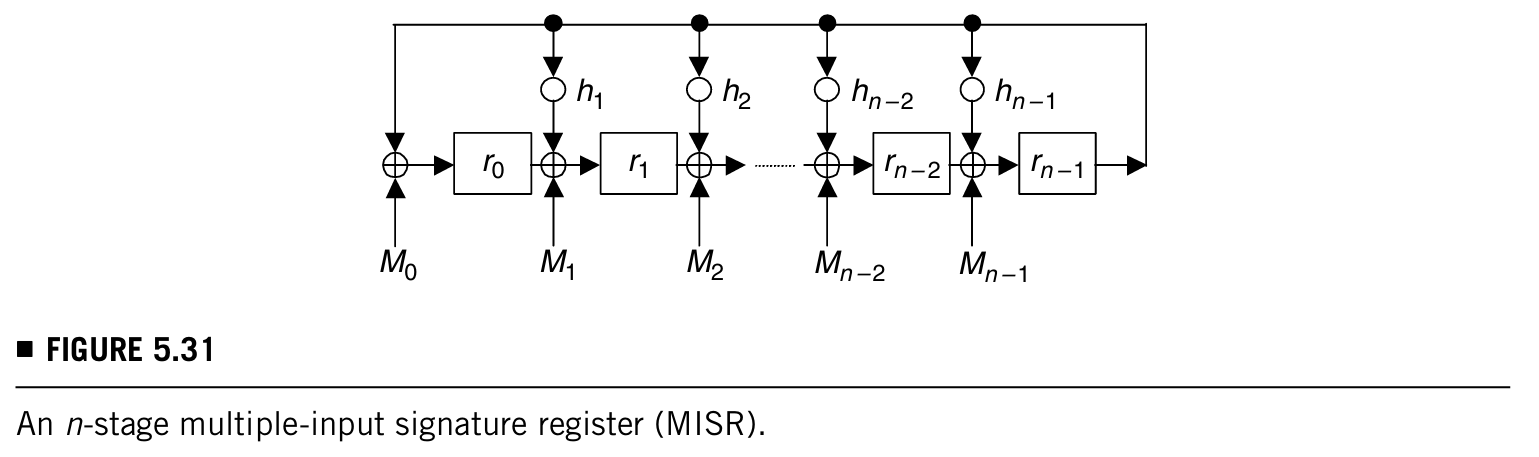

ones count testing、transition count testing、serial signature analysis存在一个共同的问题,就是当测试一个m输出的CUT的时候,会有额外的硬件花费。降低硬件花费的一个方法就是用一个m选1的多选器,但是问题是会增加测试时间,时间会乘m倍,那么就考虑用下图的n-stage multiple-input signature register (MISR):

MISR用了额外的XOR gates将L比特的输出序列M0到Mn-1同时压缩进了modular LFSR。

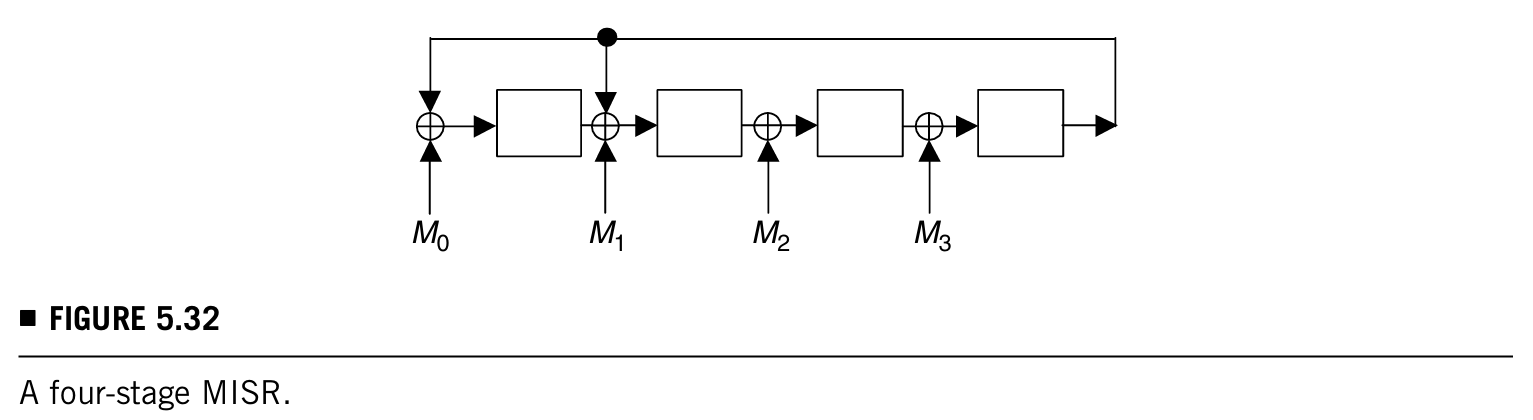

考虑下图four-stage MISR的例子:

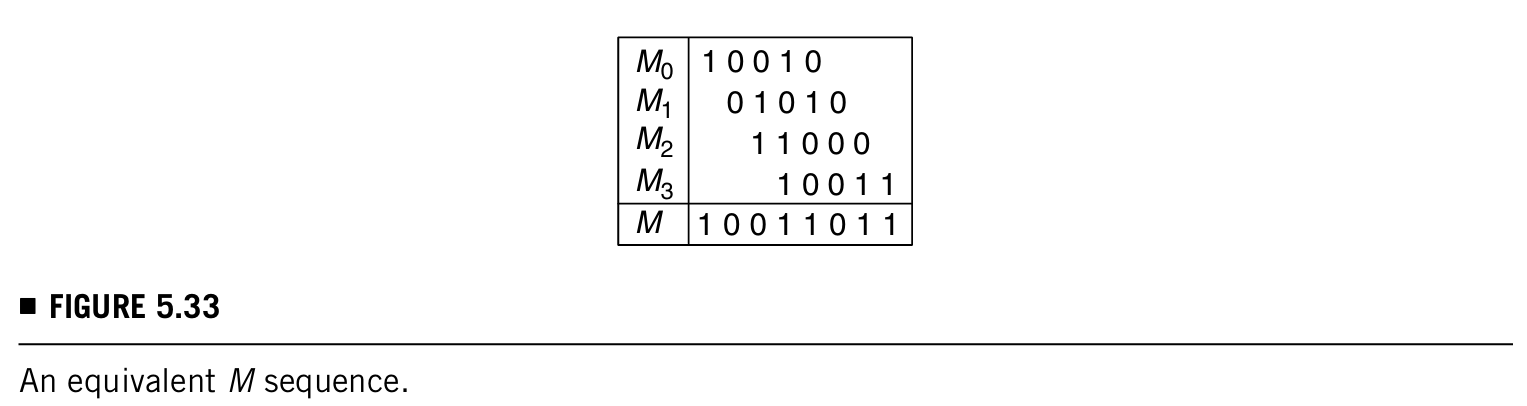

f(x) = 1+x+x^4,让M0 = {10010},M1 = {01010},M2 = {11000},M3 = {10011},那么MISR的signature R就是{1011},用上面M(x)的公式得到M = {10011011},像下图这样计算得到:

这和图5.30a中SISR的结果一样,R = {1011}。

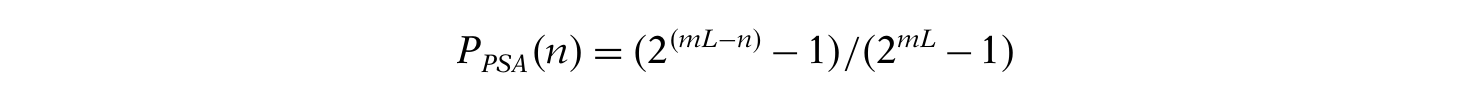

在n-stage MISR中mL比特的序列待压缩,L > n ≥ m ≥ 2,那么parallel signature analysis (PSA)的aliasing probability表达为下式:

如果L远远大于n,那么P_PSA(n)约等于2^-n,比如说n = 20的时候,P_PSA(n) < 2^-20 = 0.0001%,也就是暗示说当L远远大于n,P_PSA(n)的大小主要依赖于n。那么也就是如果要降低aliasing probability有两种方式:

- 增加MISR的阶数n

- 用相同的MISR但是用不同的f(x)可能会有用