接触fpga一段时间,也能写点跑点吧......试试系统地康康呢~这个需要耐心但是回报巨大的工作。正原子&&小梅哥

15_语法篇:Verilog高级知识点_哔哩哔哩_bilibili

1Verilog基础

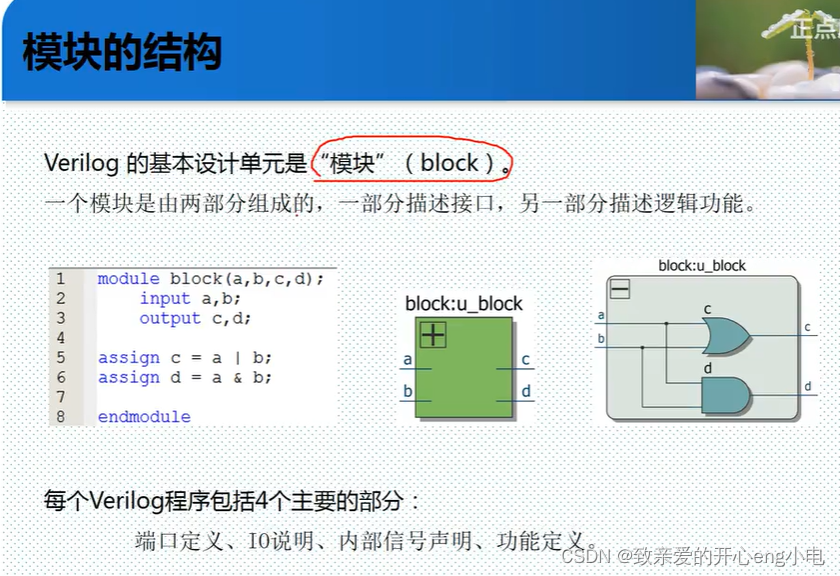

Verilog程序框架:模块的结构

类比:c语言的基础单位是函数

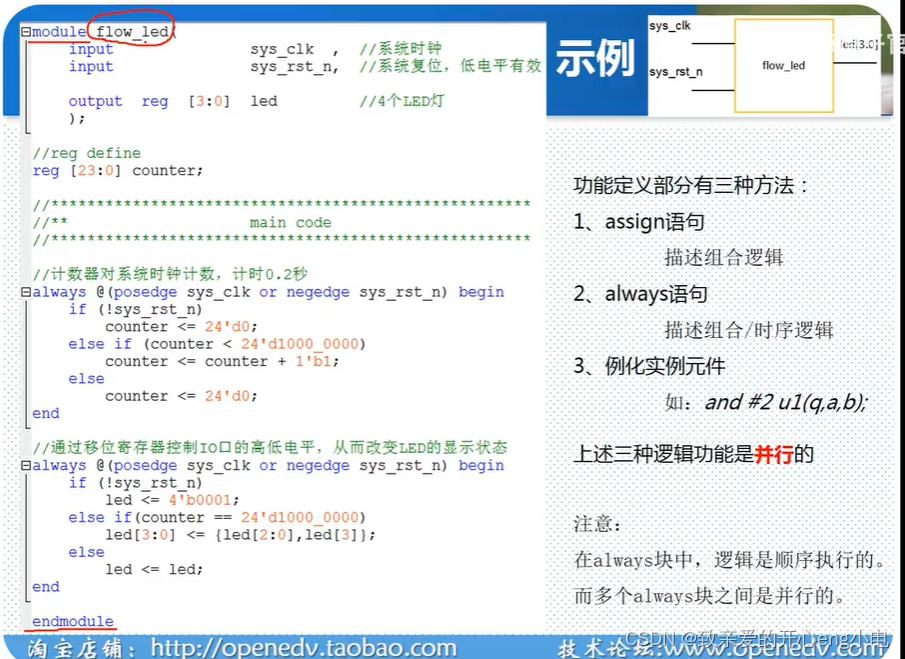

一个流水灯实验的example

counter即是内部信号声明

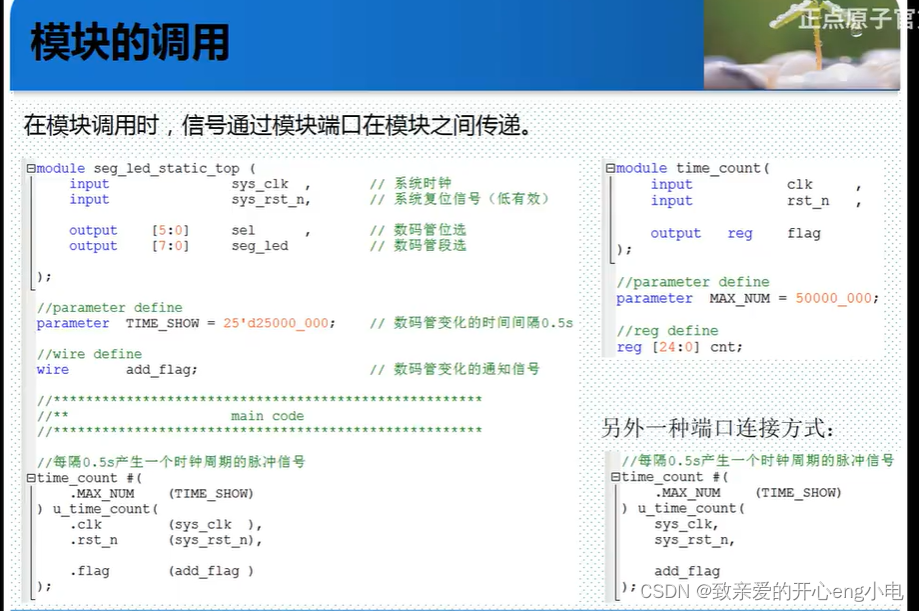

模块的调用

例化中的参数传递问题

在Verilog中,#(.PARAM_NAME(VALUE))是一种参数化实例化(parameterized instantiation)语法,用于在实例化模块时传递参数。具体来说,它用于在实例化某个模块时,覆盖该模块中定义的默认参数值。

假设我们有一个模块Timer,其定义如下:

module Timer #(parameter MAX_NUM = 100) (

input wire clk,

input wire reset,

output reg [7:0] count

);

always @(posedge clk or posedge reset) begin

if (reset)

count <= 0;

else if (count < MAX_NUM )

count <= count + 1;

else

count <= 0;

end

endmodule

在这个模块中,MAX_NUM是一个参数,默认值为100。如果我们在实例化这个模块时,希望将MAX_NUM的值改为某个不同的值,例如TIME_SHOW,我们可以使用参数化实例化语法来实现。

module TopModule (

input wire clk,

input wire reset,

output wire [7:0] timer_count

);

// Parameterized instantiation

Timer #(.MAX_NUM(TIME_SHOW)) timer_instance (

.clk(clk),

.reset(reset),

.count(timer_count)

);

endmodule

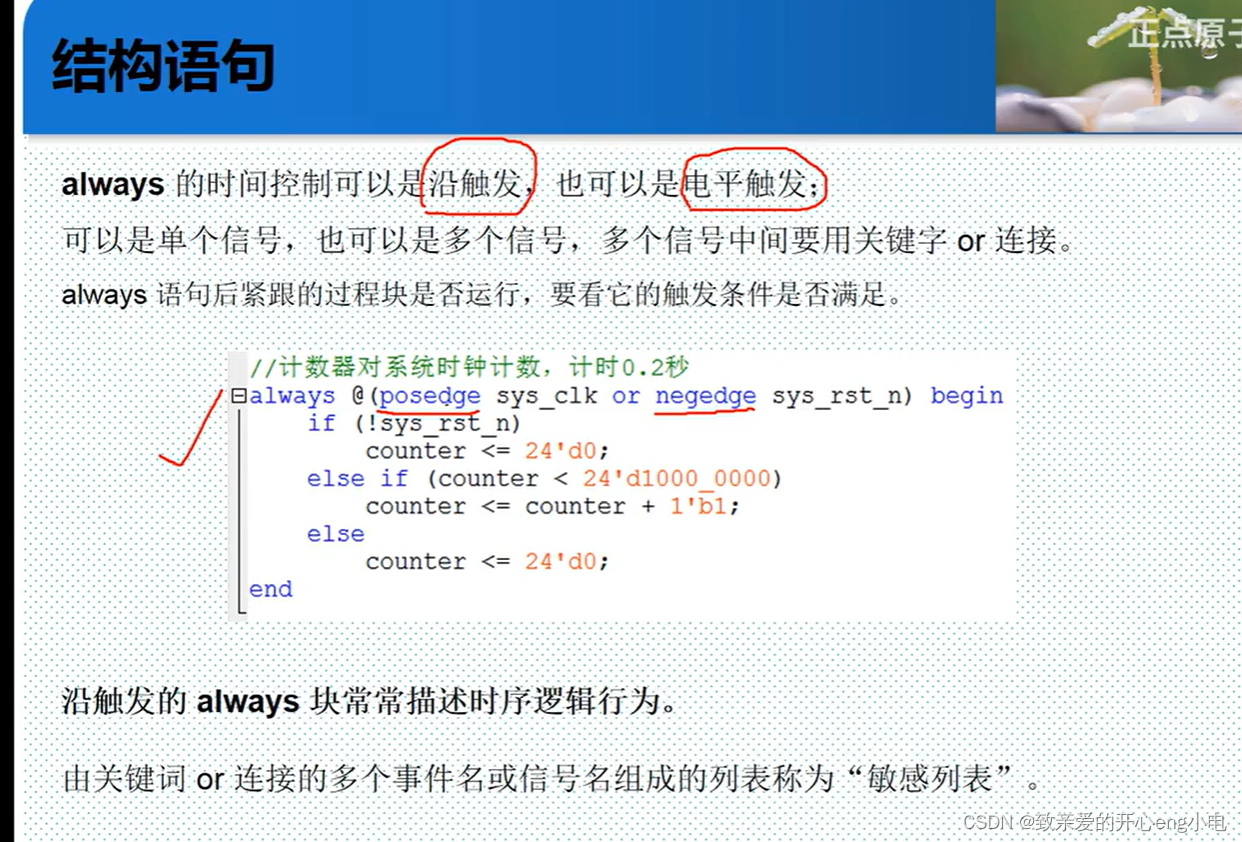

结构语句

initial

#20:延时20个单位的时间

延时了20个单位后又延时了10个单位又延时了30个单位......

timescale

时间单位是通过timescale指令设置的。在你的Verilog文件中添加适当的timescale指令,可以明确定义时间单位和时间精度,从而确定延时语句(如#20)的具体含义。

`timescale 1ns / 1ps指令设置时间单位为1纳秒,时间精度为1皮秒。

#10表示延时10纳秒。

always

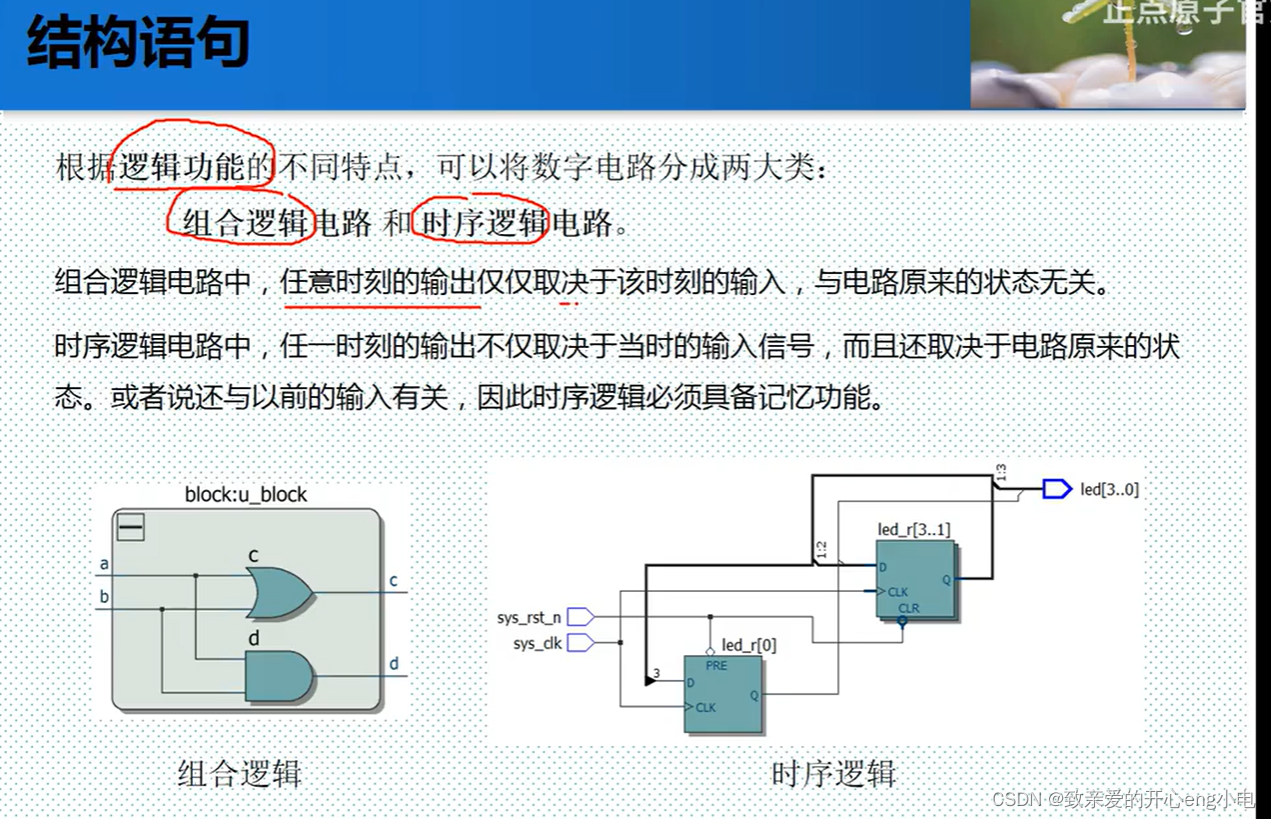

组合逻辑vs时序逻辑

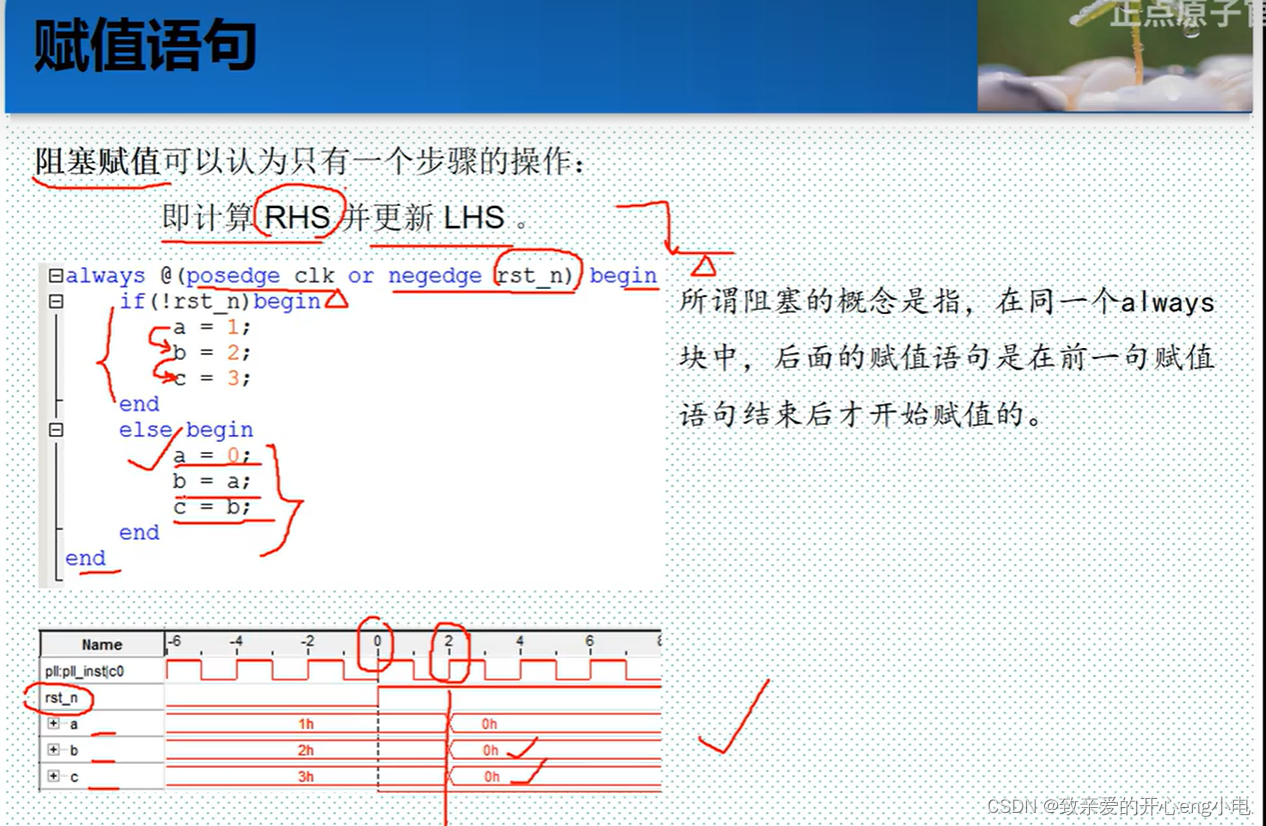

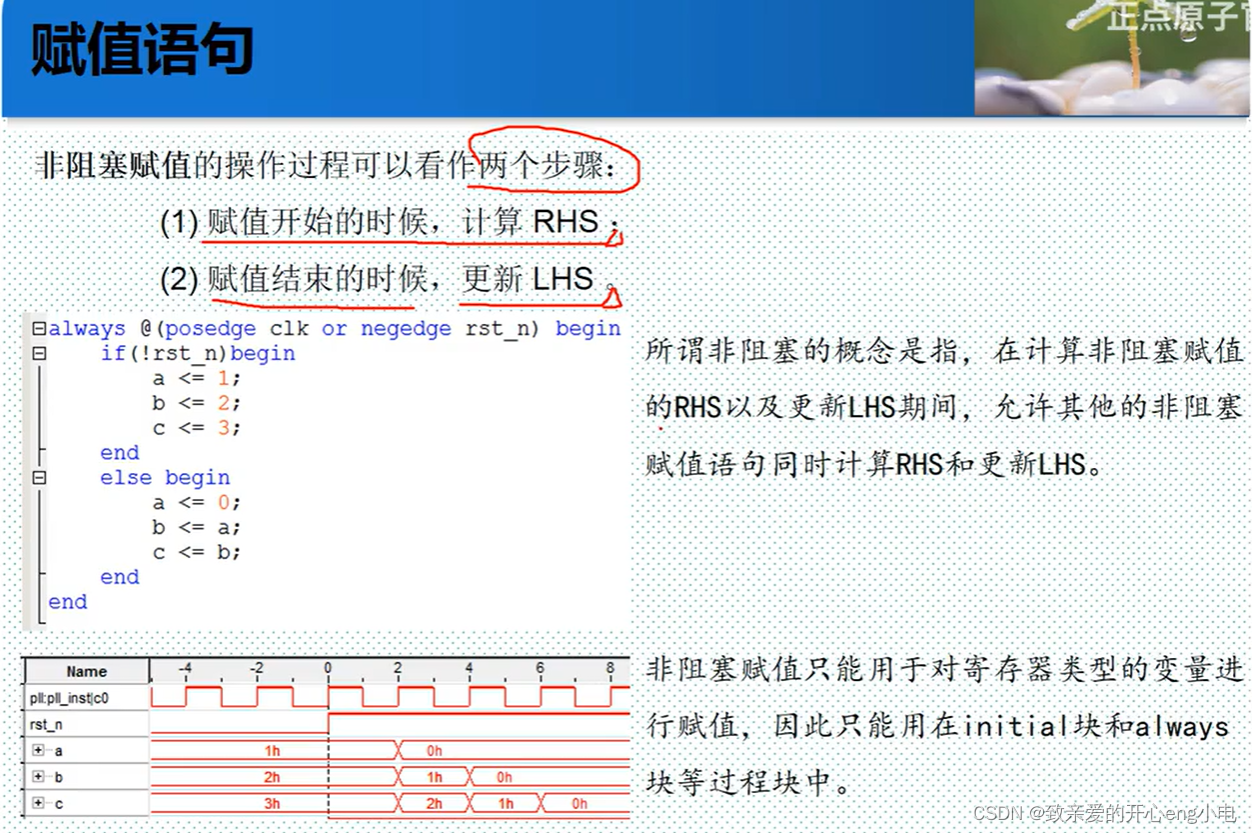

赋值语句:阻塞语句和非阻塞语句

条件语句

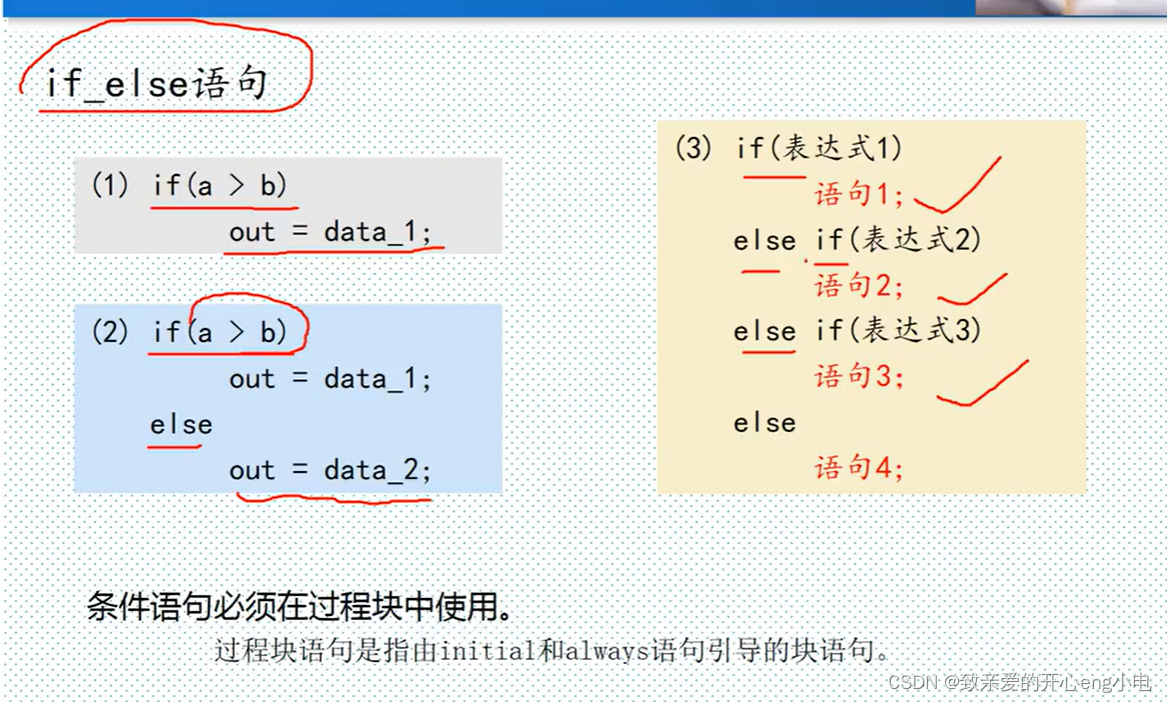

if else

case

'bx:默认32位

状态机

状态机的概念

状态机是Verilog中很常见的一种语法结构。

首先,我们在什么时候需要用状态机捏?一个密码锁的example:

状态机的模型

moore状态机是mealy状态机的一个特例

状态机的设计

八股文。写就有分。

example:推荐独热码

latch:会导致电路毛刺很多

产生latch的原因:1case情况没给完全2if没有对应的else

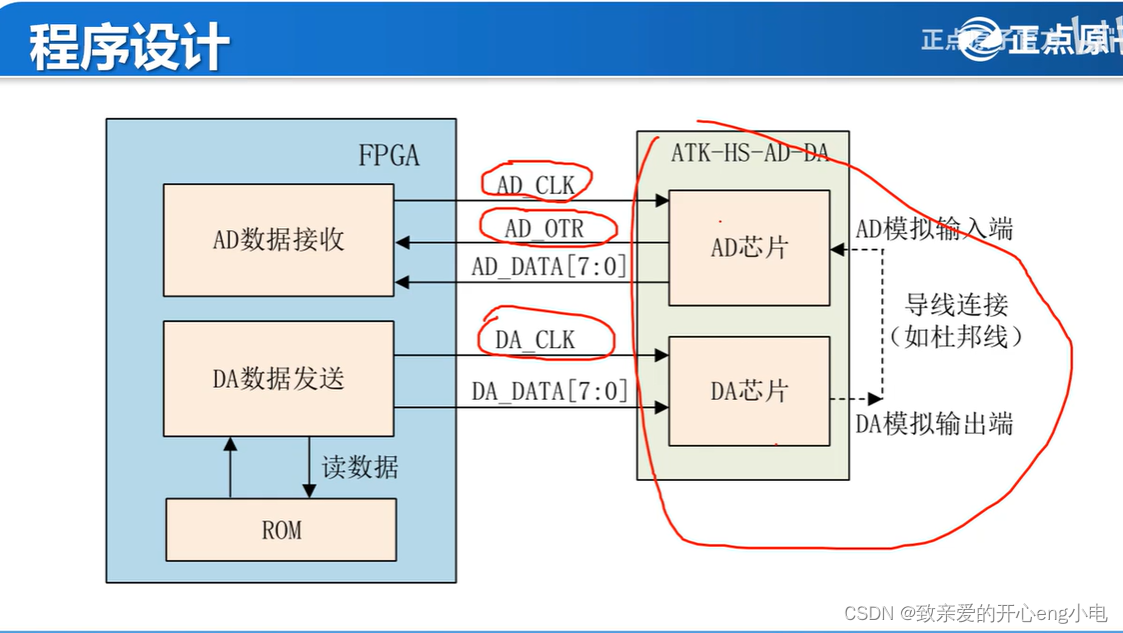

2ADDA

AD_OTR:指示位,模拟量超出量程了!

3串口通讯发送原理