看了一周PL端的大程序,甚是复杂。

所以来学学时序方面的基础知识。不然都不知道时序约束怎么通过。

参考内容:

正点原子FPGA静态时序分析与时序约束_V2.2.pdf

《Xilinx FPGA权威设计指南 ------Vivado 2014集成开发环境》

概念

时钟

时钟抖动

时钟偏差

Uncertainty

同步/异步电路

建立时间/保持时间

发起沿/捕获沿

1.时钟:理想的时钟模型是一个占空比为50%的方波。实际电路中输入给FPGA的晶振时钟是正弦波。

实际晶振产生的正弦波存在一些时钟抖动。

2.时钟抖动(Clock Jitter):相对于理想时钟沿,实际时钟存在不随时间积累的、时而超前、时而滞后的偏移。(时钟脉冲宽度发生暂时变化,T cycle 即Period或大或小)

3.时钟偏差(Clock Skew):同一个时钟域内的时钟信号到达数字电路各个部分(一般指寄存器)所用的时间差异

走线延时;组合逻辑;

时钟域;时钟树;

时序分析

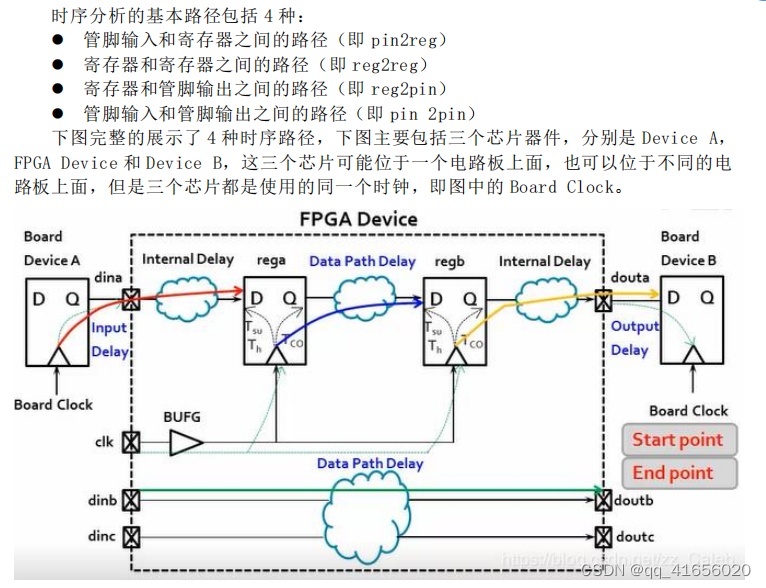

时序分析的基本路径

管脚输入和寄存器之间的路径(即 pin2reg):

从 device A 的时钟到 FPGA 的第一级寄存器的输入端口,这个部分包括 3 个延迟,分别是 Tco( 时钟到寄存器输出延时 ),Input Delay(PCB 板子的输入走线延迟)和 Internal Delay(FPGA 内部的输入走线延迟)。

寄存器和寄存器之间的路径(即 reg2reg):

两个同步元件之间的路径(rega 到 regb 蓝色),这个部分包括 2 个延迟,分别是 Tco( 时钟到寄存器输出延时 )和 Data Path Delay(FPGA 内部的组合逻辑和数据走线延 迟)。

寄存器和管脚输出之间的路径(即 reg2pin):

最后一级寄存器到 device B 数据端口的路径(黄色),这个部分包括 3 个延迟,分别是 Tco( 时钟到寄存器输出延时 ),Internal Delay(FPGA 内部的输入走线延迟)和 Output Delay(PCB 板子的输出走线延迟)。

管脚输入和管脚输出之间的路径(即 pin 2pin):

端口到端口的路径(dinb 到 dinb 绿色),这个部分包括 1 个延迟,即 Data Path Delay(FPGA 内部的组合逻辑和数据走线延迟)。

时序分析的基本公式

数据到达时间:数据在发送沿发送后,经过T会到达接收寄存器的数据端口。

时钟到达时间:时钟到达接收寄存器的时钟端口(发送数据的下一个采样沿开始)。

建立时间的裕量(Setup Slack):正值------说明建立关系合格;负值------不合格,会导致采样出错。

数据到达时间 = 启动沿时间 + Tclk1 + Tco + Tdata(reg2)

数据锁存/读取时间 = 锁存沿时间 + Tclk2 - Tsu

建立裕量 = 数据锁存时间 - 数据到达时间

保持时间的裕量(Hold Slack):正值------保持关系合格;负值------保持关系不满足,会导致采样出错。

数据保持时间 = 启动沿 + Tclk1 + Tco + Tdata + 数据周期时间

数据锁存时间 = 锁存沿 + Tclk2 + Th

保持裕量 = 数据保持时间 - 数据锁存时间

多周期路径(Multicycle Paths)检查

有时:数据不需要在下一个时钟周期就稳定下来,可能在数据发送后的几个时钟周期之后才起作用;一些数据经过的路径较复杂,延时较大,无法在下一个时钟周期稳定下来,必须要在数据发送后数个时钟周期之后才能被采用。

e.g 乘法器

在多周期路径的建立时间(Setup Time)检查中,时序分析软件会按照用户指定的周期数延长Data Required Time,放松对相应数据路径的时序约束,从而得到正确的时序余量计算结 果;

在保持时间(Hold Time)检查中,时序分析软件也会相应地延长Data Required Time,不再按照单周期路径的分析方式执行(不再采用launch edge最近的时钟沿,而是采用latch edge最近的时钟沿),这就需要用户指定保持时间对应的多周期个数。

多周期路径是为了解决信号传播太慢的问题,慢到一个周期都不够,所以要把Setup Time的检查往后推几个周期------ 扩大Setup Time检查的时间窗口 。而 Hold Time检查信号是否传播得太快 ,如果把检查时刻往后推,就缩小了Hold Time检查的时间窗口。

FPGA器件时序模型

PVT

基本单元 & paths

PVT:指芯片工艺(Process)、电压(Voltage)、温度(Temperature)。

不同的PVT参数,芯片的时序模型是有差异的。

一般时序分析会涉及到三种情况:

最好的条件------速度最快时;BCF(fast process,lowest temp,high voltage)

最坏的条件------速度最慢是;WCS(slow process, high temp,lowest voltage)

典型的条件------介于两者;TYP(typical process,nominal temp,nominal voltage)

时序分析工具通过Worst corner来保证建立时间的时序,通过Best corner来保证保持时间的时序。

由于一般情况下设计以建立时间违例为主,所以时序分析工具默认使用slow corner。

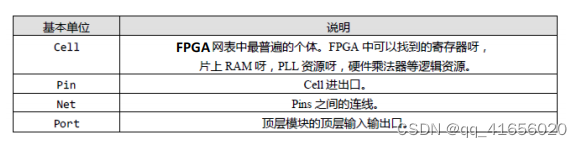

基本单元与paths

FPGA开发工具需要读入布局布线后的网表才能进行时序分析。网表是由以下一系列的基本单元构成的:

Cells:器件的基本结构单元(如,LUTs,Reg,IO单元,PLL,存储器块,etc)

Pins:Cell的输入输出端口(不包括器件的输入输出引脚)

Nets:同一个Cell中,从输入pin到输出pin经过的逻辑。(网表中连接两个相邻Cell的连线不被看做Net,而被看作同一个点,等价于Cell的pin------等价于FPGA器件中的一段布线逻辑)

Ports:顶层逻辑的输入输出端口,对应已经分配的器件引脚

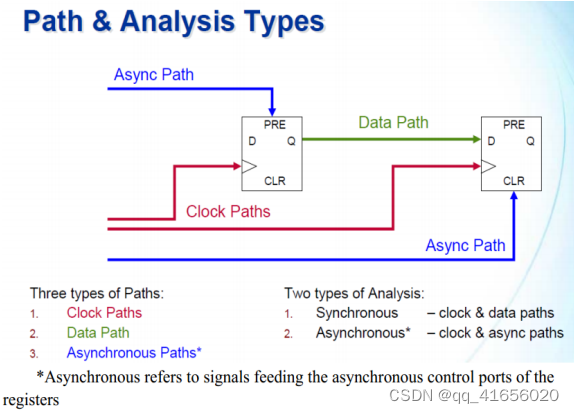

Paths:

Clock paths------从clock port或内部生成的clock pin到寄存器Cell的时钟输入Pin

Data paths------从输入port到寄存器Cell的数据输入pin,或从寄存器Cell的数据输出pin到另一个寄存器Cell的数据输入pin

Asynchronous paths------从输入port到寄存器Cell的异步输入pin,或从寄存器Cell的数据输出pin到另一个寄存器Cell的异步输入pin

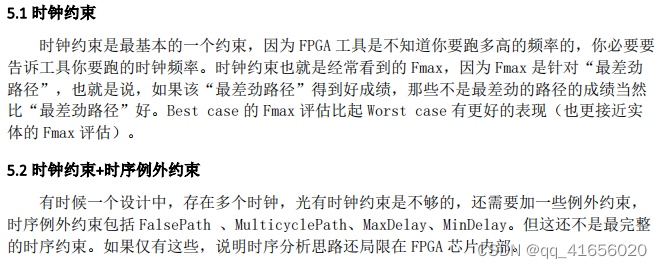

时序约束的方法

时钟约束

时钟约束 + 时序例外约束

时钟约束 + 时序例外约束 + IO约束

Vivado时序分析设计

Edit Timing Constrains编辑时序约束按钮

create_clock(clk:时钟周期、占空比)

(差分时钟只约束p端)

set_clock_uncertainty设置时钟不确定性(该clk全部时钟间路径的裕量)

set_false_path设置为伪路径(时序分析工具不再分析这些路径,这种约束我们称之为exceptions)

set_input_delay set_output_delay指定输入输出延迟值

时钟:

基本时钟

虚拟时钟

生成时钟 create_generated_clock (分频 -divide_by2\;倍频-multiply_by 2\ )

create_clock -name {clk} -period 20.000 -waveform { 0.000 10.000 } [get_ports {clk}]

名称 周期 第一个上升沿&下降沿

约束PLL输出时钟:(vivado中工具会自动约束)

约束组合逻辑IO接口:set_max_delay det_min_delay

约束异步时钟组set_clock_groups -asynchronous ...

时序分析的优先级

约束越明确,优先级越高

时序优化:在长的路径中插入一些寄存器,简化逻辑运算;把相关的逻辑约束在一个区域中;etc

那么时序约束不通过(出现违例)要怎么解决呢?