Chapter 6 Frequency Response of Amplifiers

这一节我们学习单极和差分运放的频率响应.

6.1 General Considerations

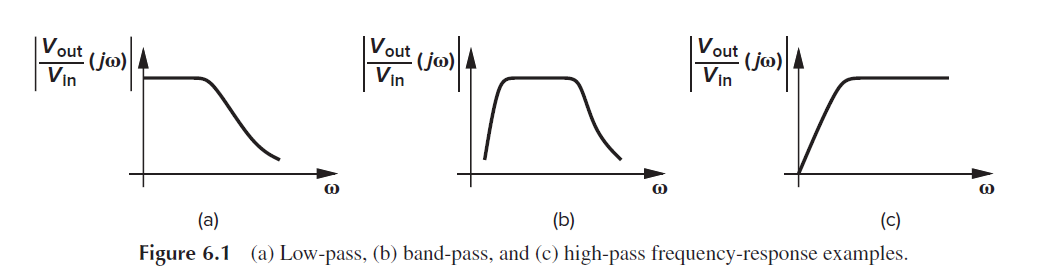

我们关心magnitude vs 频率, 因此有低通, 带通, 高通滤波器

6.1.1 Miller Effect

Miller's Theorem

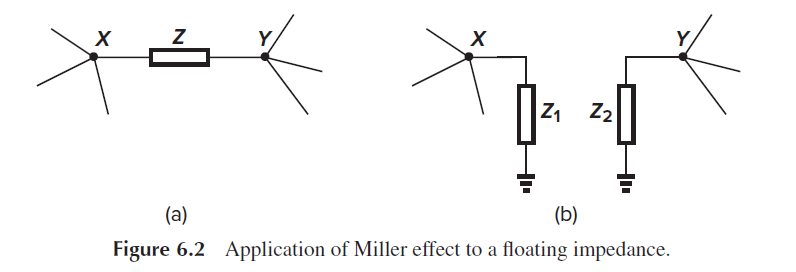

考虑impedance Z1和Z2, X和Y之间增益为Av.

Z1 = Z/(1-Av). Z2 = Z/(1-Av^-1). Av=Vy/Vx.

原理证明:

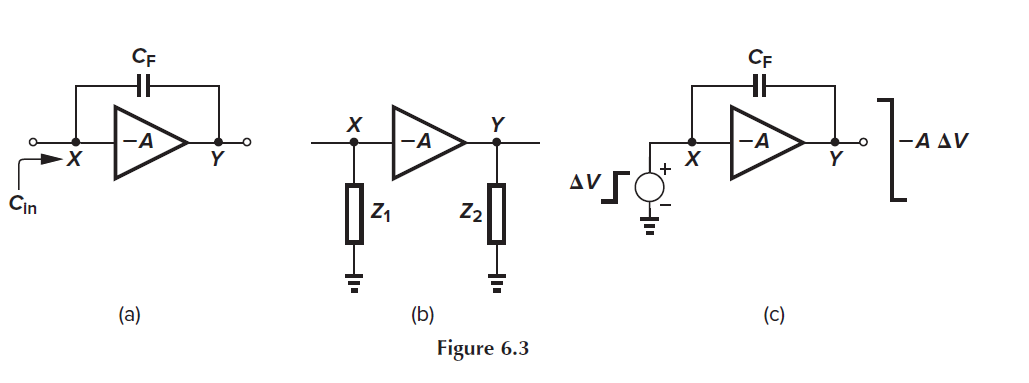

利用miller原理, 可以在X端产生Cf*Av的大电容(miller电容)

6.1.2 Association of Poles with Nodes

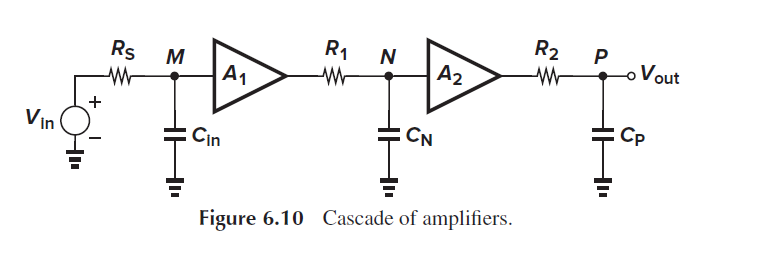

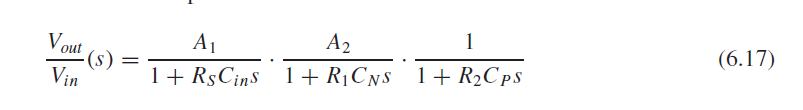

对于下图级联的运放, 我们可以写出传输函数

传输函数

6.2 Common-Source Stage

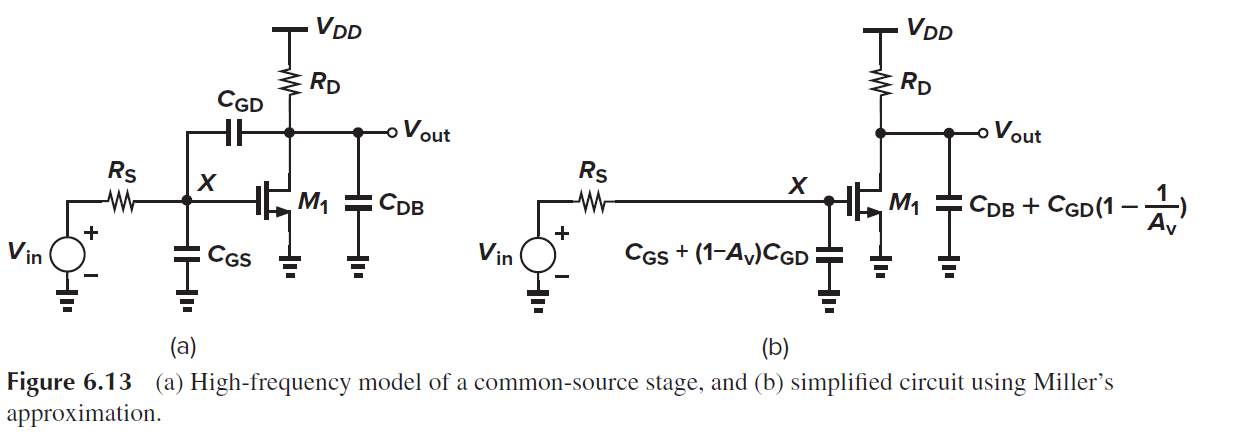

考虑下图的CS结构

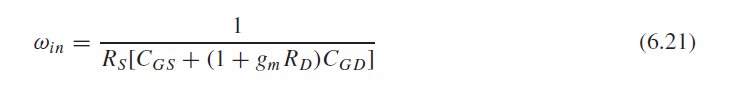

在X处有Cgd的miller cap=Ccd*(gm Rd), 估算输入端极点为

估算输出端极点为

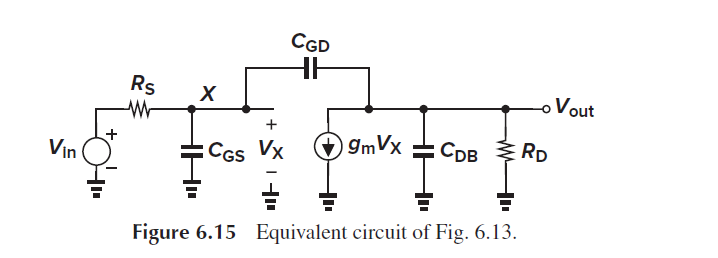

但这里的估算没有体出零点, 我们采用Direct Analysis

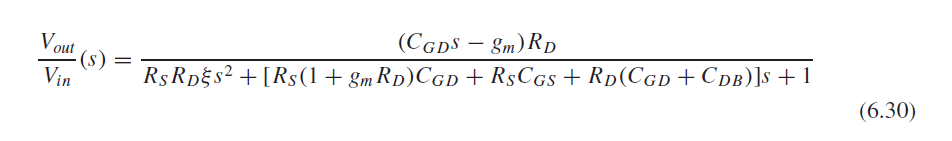

可得传输函数

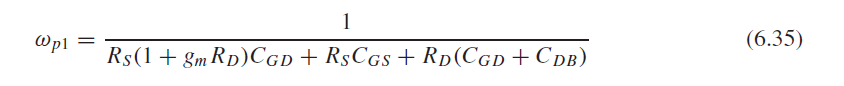

采用极点分离, 主极点为

对比直接求解(6.35)和我们用miller cap (6.21)得估算, 两者差距不大

当Cgs dominates时, 次极点和估算一样.

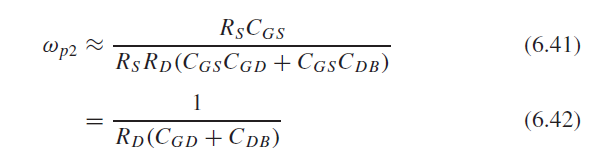

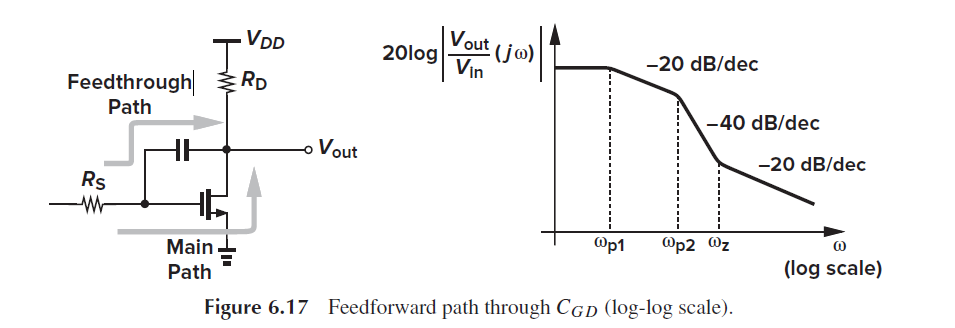

6-30公式直接分析展示了有一个右零点. wz=+gm/Cgd. 右零点代表两条通路的极性相反, 因此输出可能为零!

右零点意味着在w=wz时输出Vout=0, 输出shorted to grond. 说明所有电流都通过Cgd走到了沟道, 没有电流流过RD. 通过Cgd的电流为v * admittance. admittance=Cgs*wz.

右零点 位置可得

ω z = + g m C G D \omega_{z}=+\frac{g_{m}}{C_{GD}} ωz=+CGDgm

考虑输入阻抗, 采用miller效益简化为, 即Cgs+miller电容

6.3 Source Followers

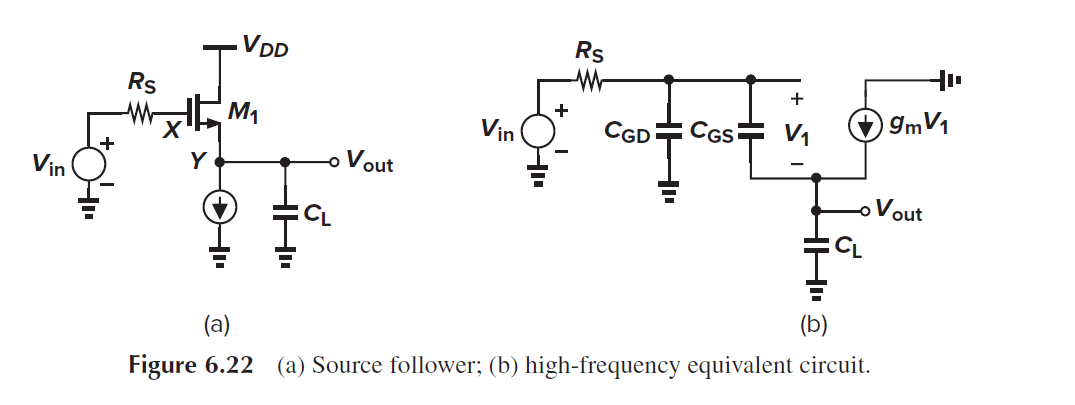

source follower 作为level shifters或者buffers, 也会影响整体的频率响应. 考虑下图

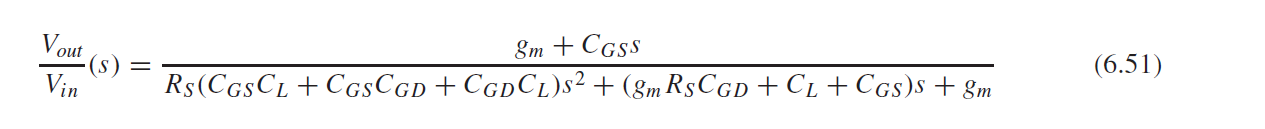

可推导出传输函数

如果输出电容CL=0, Vout/Vin可简化为

Cgd引入了极点. Cgs电容, 由于source follower的效果Gate short to Source, 因此不引入零点和极点.

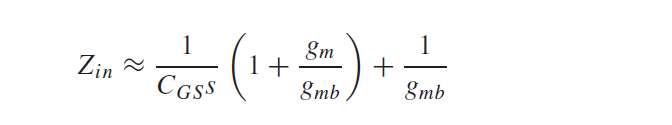

考虑输入阻抗

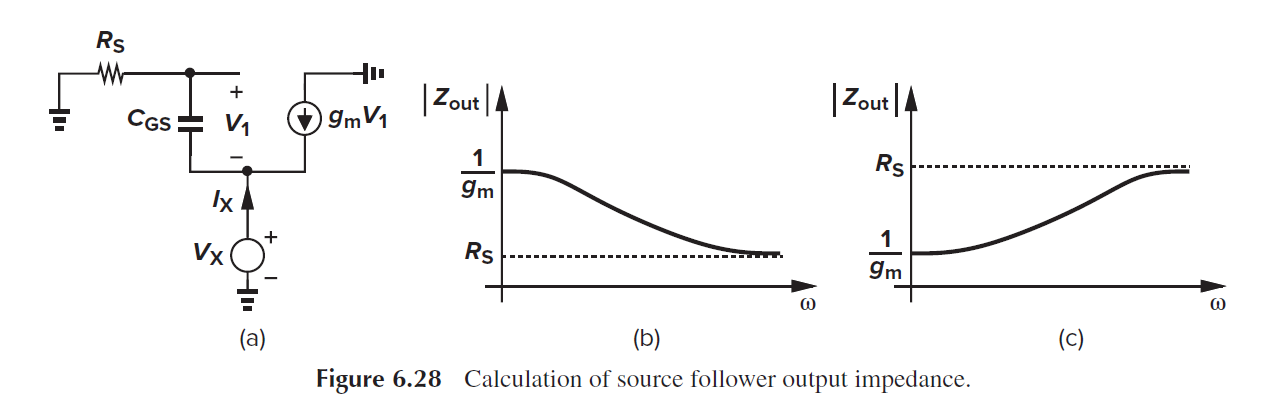

考虑输出阻抗

SF的Zout 的输出阻抗大部分表现为从©, 即有电感属性, 即impedance随着频率增加而增加

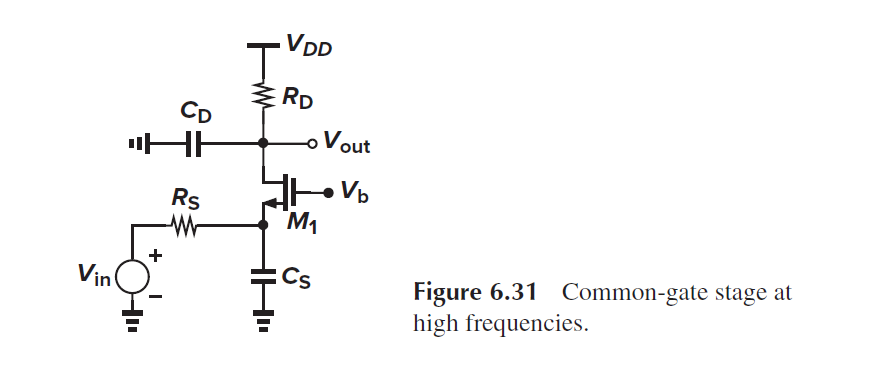

6.4 Common-Gate Stage

考虑下图common-gate结构

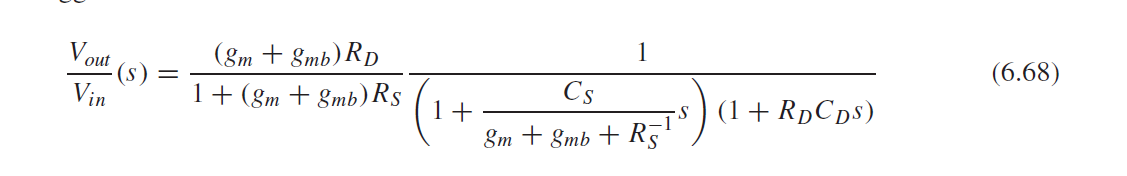

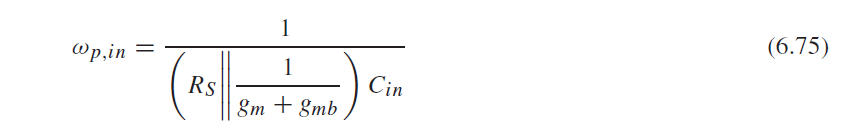

其输入输出传输函数为

没有miller电容效应, CG结构主要应用于:1) 需要小的输入阻抗. 2) 在cascode stage中.

输入阻抗:

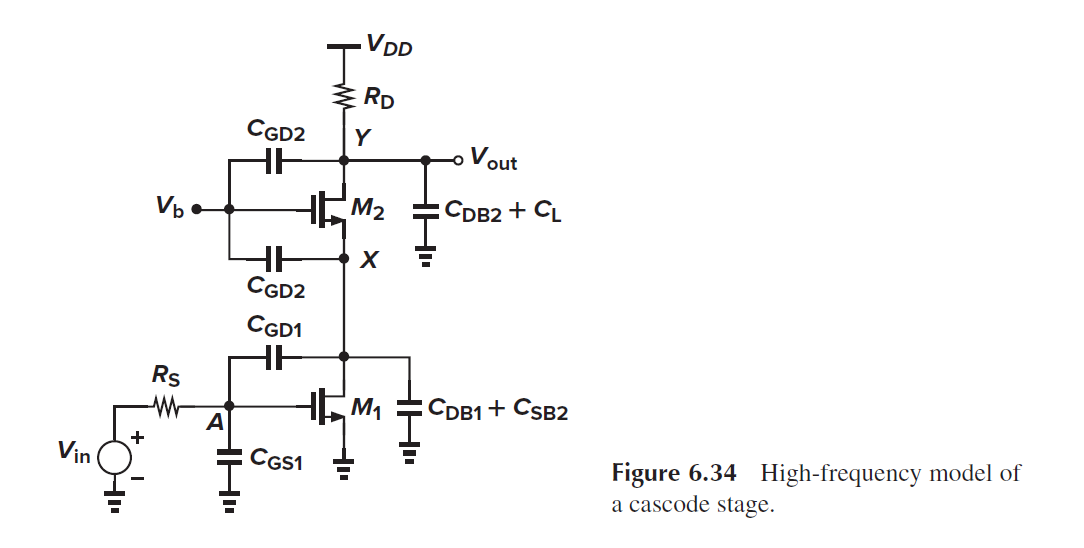

6.5 Cascode Stage

考虑cascode结构如下图所示

miller效应的Cgd1在A和X之间, 但是gain很小, X向M2看进去的阻抗为1/gm2.

A处极点:

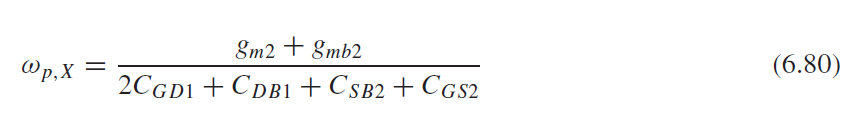

X处极点:

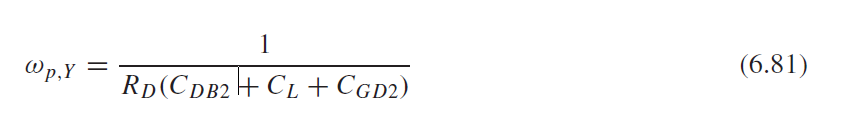

Y处极点:

一般来说X处的极点为高频极点, 因为阻抗低1/gm.

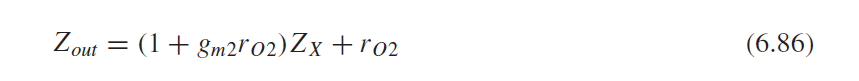

输出阻抗:

Zx=ro1||(CX s)^−1

6.6 Differential Pair

6.6.1 Differential Pair with Passive Loads

考虑差分结构带电阻, 如下图所示

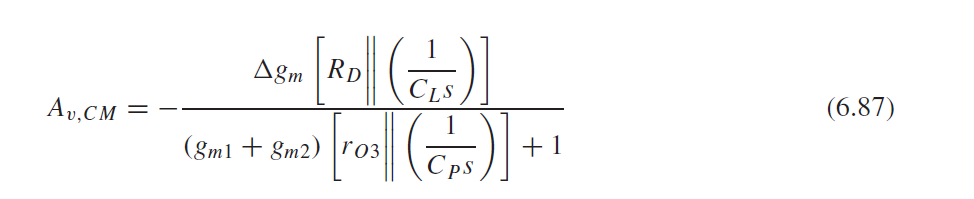

CM增益为

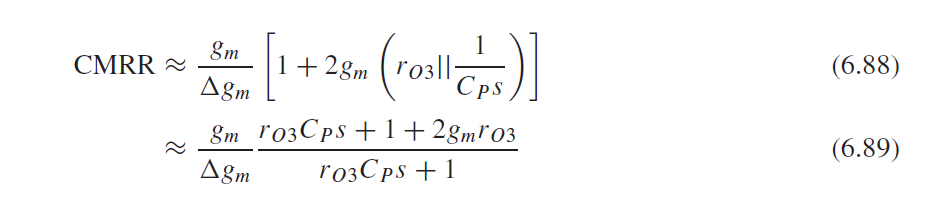

CMRR为

在高频下, M3 source的CP会降低P点阻抗, 降低CMRR. CMRR分布图如下

如果输出端是MOS,那么高频极点为Vout处的Cgd*Rout

6.6.2 Differential Pair with Active Load

带active current mirror的差分对如下所示, 考虑输出输入函数

主极点在输出Vout处, wp1=1/(Rout*CL)

次极点在E处, 即mirror pole, wp2=1/(gm3*Ce)

另外还有一个左零点 . 位置在次极点的两倍频处. 来源于M1-M3-M4为slow path, M1和M2为fast path, 两者极性相同, 因此为左零点. (极性相反为右零点, 例如带miller电容的CS结构)

ω z = 2 g m p C E \omega_{z}=\frac{2g_{mp}}{C_{E}} ωz=CE2gmp

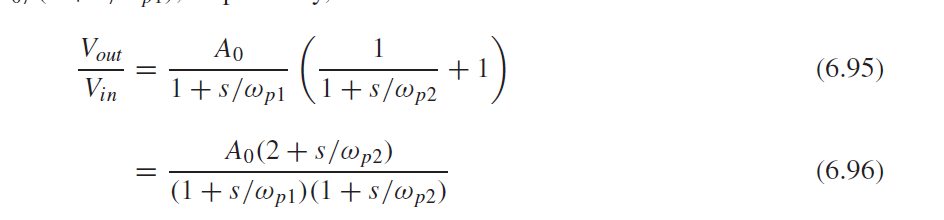

输入输出传函为:

6.7 Gain-Bandwidth Trade-Offs

我们考虑w-3db和unity-gain带宽 wu.

6.7.1 One-Pole Circuits

对于上图的单极点系统

"gain-bandwidth" product=GBW=Gain*dominant pole

对于单极点系统 GBW=wu, 即unity-gain bandwith

注意套筒式cascoding并不能提高GBW, cascode只能提高gain, 相应的f-3db会减少, 维持GBW不变.

6.7.2 Multi-Pole Circuits

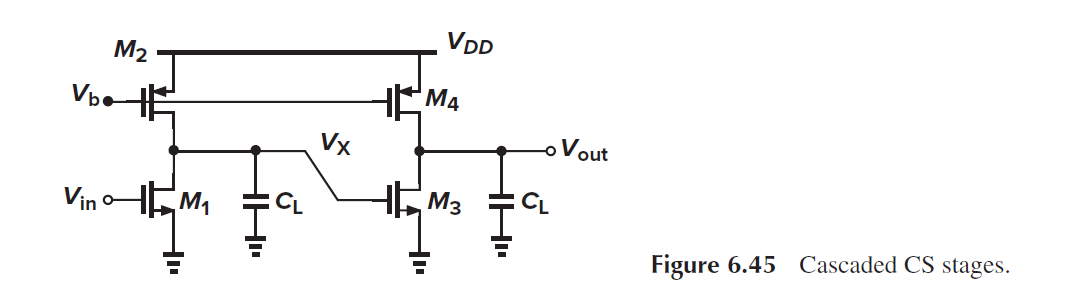

通过级联cascading 两级或者三级增益级, 是可以提高GBW的. 如下图所示

输入输出传函为

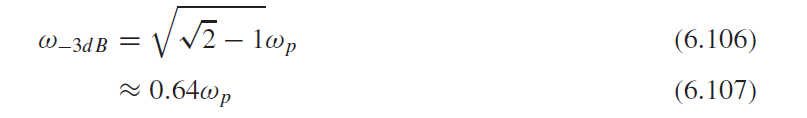

为了得到f-3db. Vout/VIn=A0^2/sqrt(2)

f-3db减小了

但是GBW增大了64%

所以级联cascading 能增加系统的GBW, 但缺点是功耗加倍, 另外容易造成系统的不稳定.