一.概述

本文主要介绍了调试软件 IP 的使用情况。调试软件 IP 是一个

嵌入式逻辑分析仪,以帮助设计者检查 FPGA 内部的信号转换。采

样信号的波形存储在嵌入的存储器中,在触发事件发生后,可以

通过 JTAG 端 口检索数据。然后,设计者可以根据所配置的条件

得到一个波形图像。

调试软件 IP 支持以下功能 :

·触发器条件可以进行动态配置

·支持实时捕获

·支持触发器的类型和条件:算术和边沿

默认客户已安装 FUXI,并 JTAG 驱动已经安装完成,PC 可以正常连接

到芯片;

2**.操作步骤**

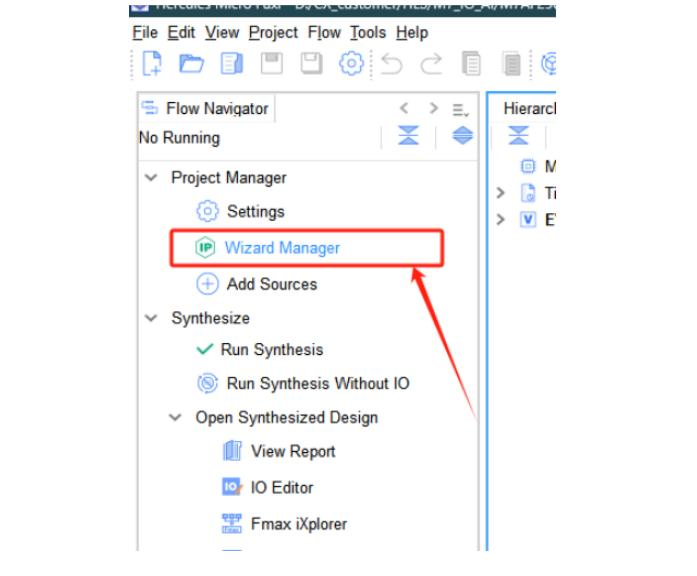

2.1 双击 Wizard Manager ,准备调用 Debugware IP;

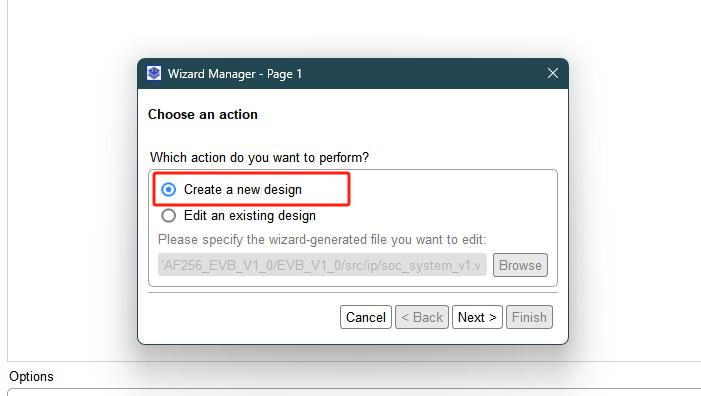

2.2 选择 Create a new design 然后点击 next 按钮

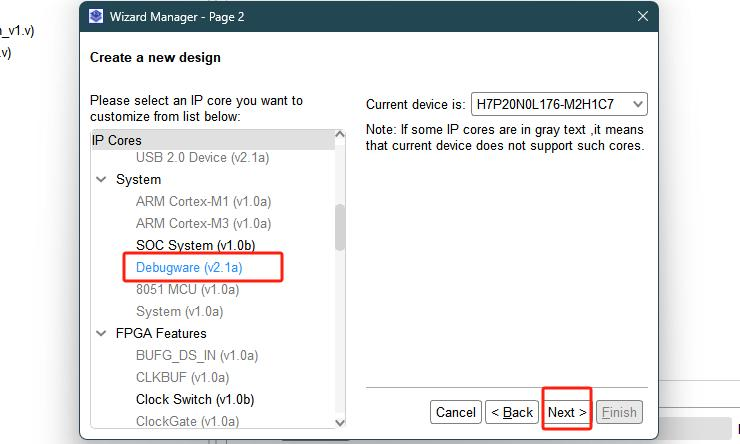

2.3 选择 Debugware IP 核 然后点击 NEXT 进入 IP 设置界面

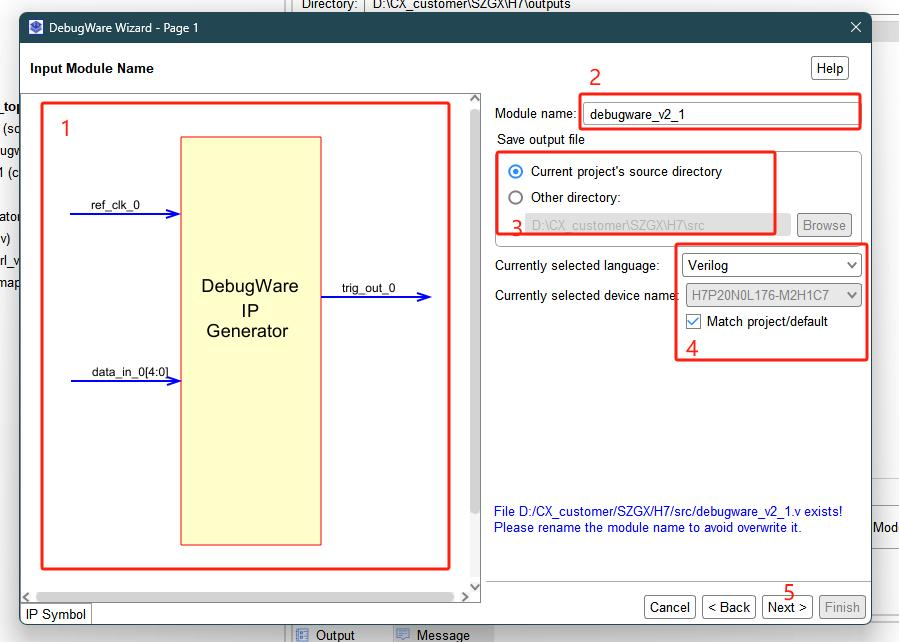

2.4 左边①框是 Debugware IP 核框架图,②是自定义命名 Debugware

名称,一般保持默认即可,也可自定义修改,③是 IP 当前源文件路

径,默认即可,④是语言和器件型号确认,确认无误,点击 NETX 进

入下一步;

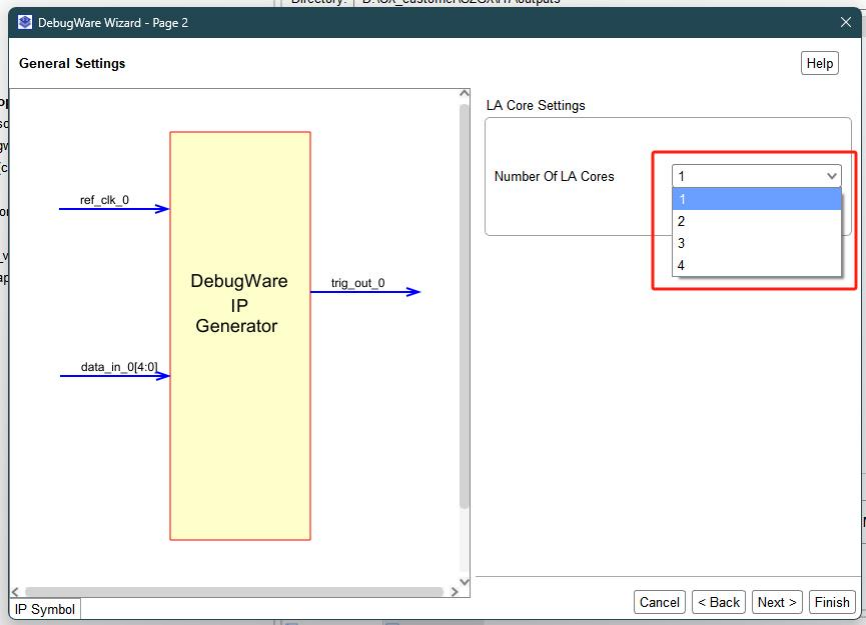

2.5 LA 核参数设置,默认选择 1 即可,最大支持选择 4;

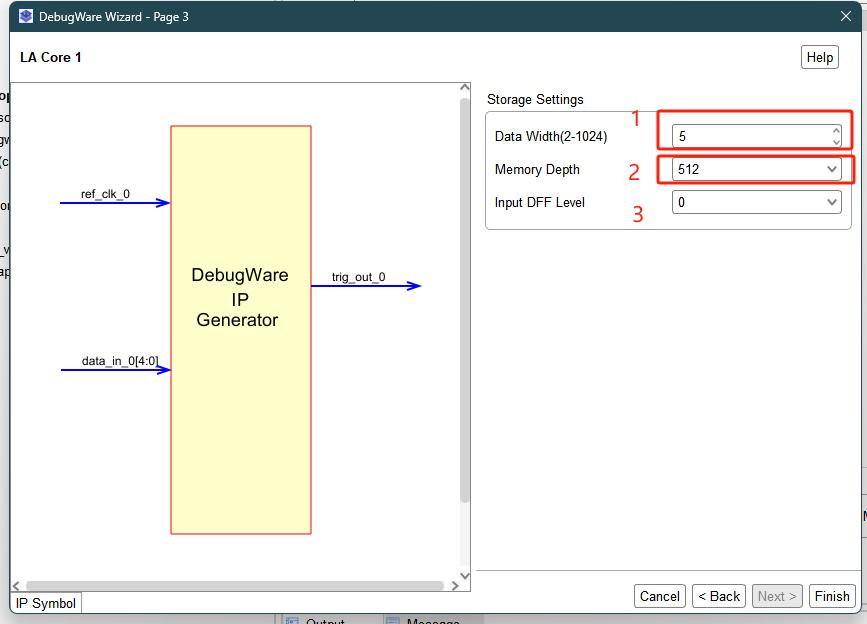

2.6 设置抓取信号的位宽和抓取信号的深度

①处设置信号位宽,支持 2-1024 范围,用户可自定义配置;

②处设置抓取信号深度,默认选择 512,也可自定义配置,推荐 1024,

过大的位宽和过大的深度会占用逻辑资源;

设置完成之后,选择 Finish,完成 Debugware IP 核的配置;

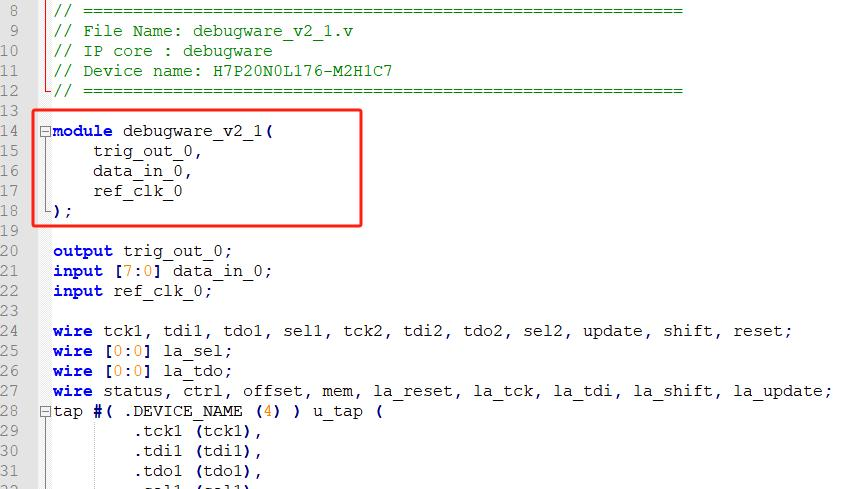

2.7.生成 Debugware IP 成功之后,双击 Debugware IP 核,找到如下

图代码,例化到自己需要抓取的代码中,trig_out_0:此信号方向输

出,可以忽略不管;data_in_0:抓取信号输入,位宽需要匹配,并且

被抓信号后面需要带位宽,否则会默认都为 1bit,例如 data[7:0];

只写 data 则为 1bit;

例化无误后,完成编译生成 ACF 文件,并且将程序下载到板子中;

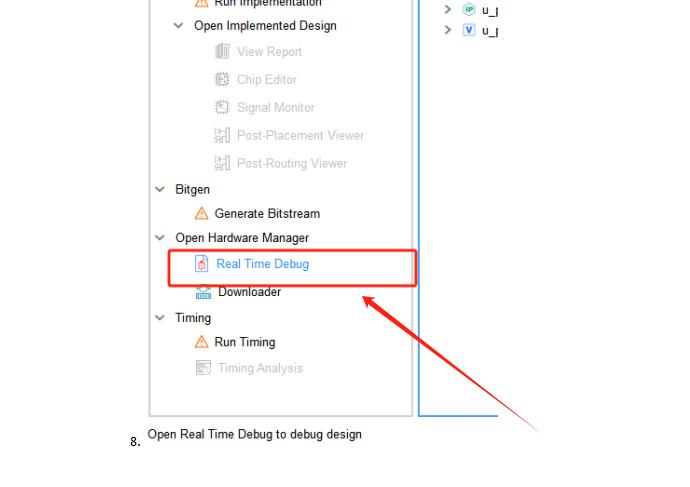

2.8 选择 Real Time Debug 选项,连接好下载器,进入到逻辑分析仪

界面;

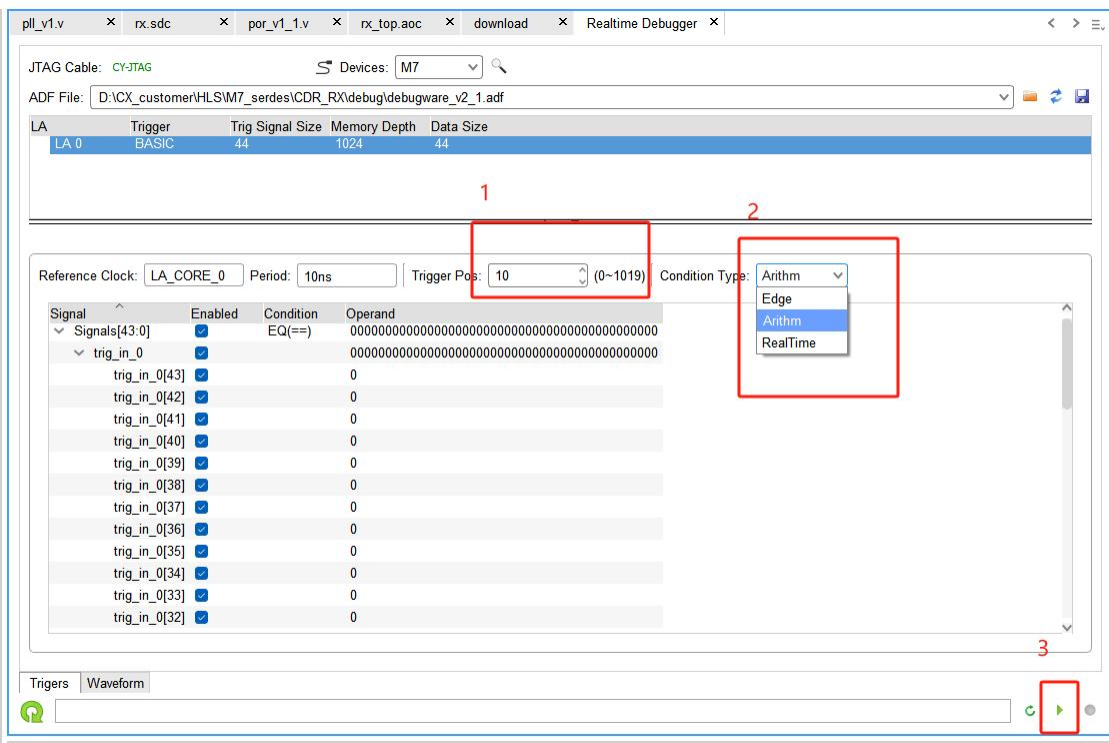

2.9.进入到 Triger 界面

①处设置波形触发位置,用户根据自己的深度设置需要触发的位置,

自定义,默认 10;

②处为触发条件的设置,可选择:Edge 边沿触发,支持上升沿下降

沿自定义,Arithm:支持数字信号触发,可设置 0 或 1,用户自定义

设置,RealTime 为实时抓取信号;

③处为开始信号,点击 3 处,信号波形触发后显示在 wave 界面,3

处后面为停止按钮;

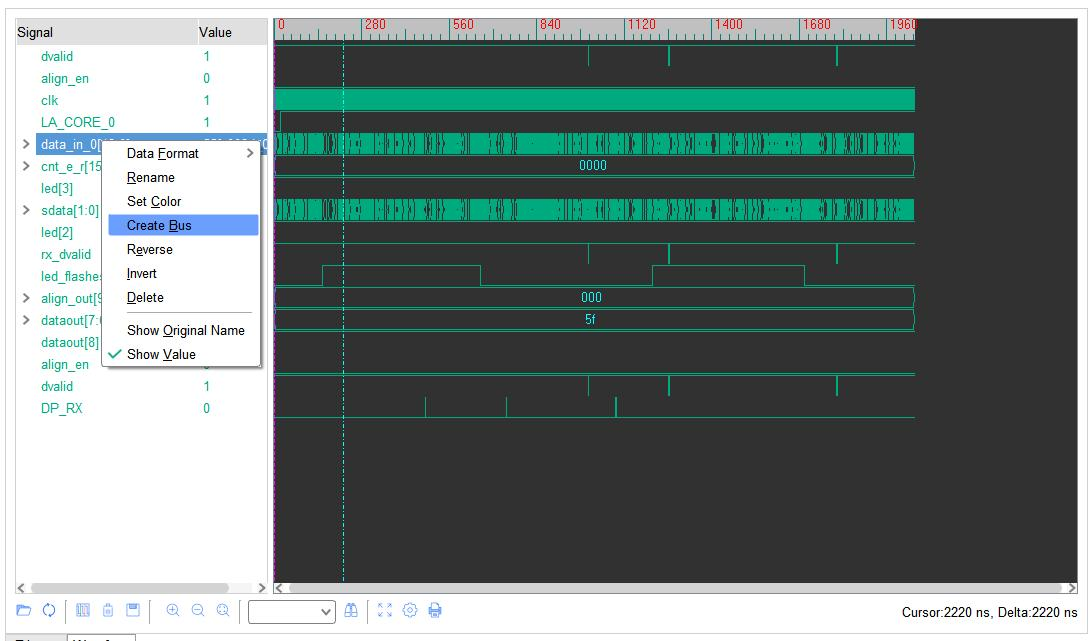

2.10 波形显示界面,用户可以放大或缩小波形,以便分析观察和调

试;修改名称,修改颜色,删除等基础操作,这里不多说明;信号重

命名操作:右键选择 Create Bus;

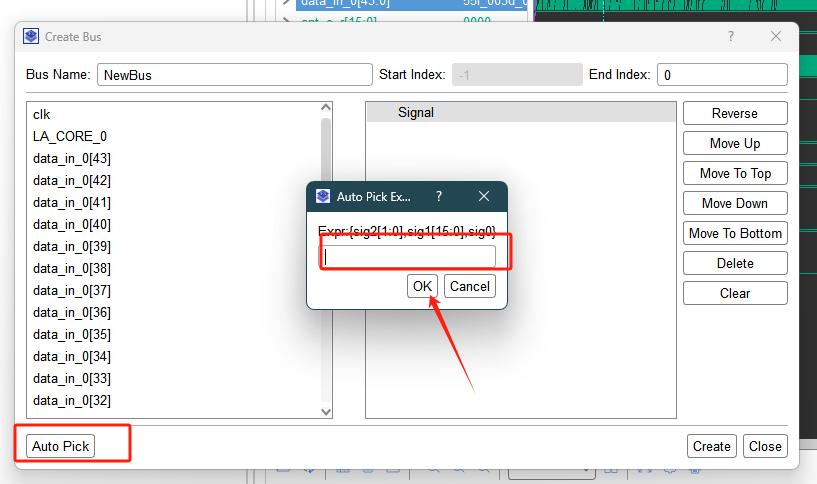

2.11 点击 Auto Pick 按钮,根据示例代码,复制自己源代码中的信

号(Expr:{sig2[1:0],sig1[15:0],sig0}),然后点击 OK,完成信

号的重命名,以便分析各个信号时序关系;

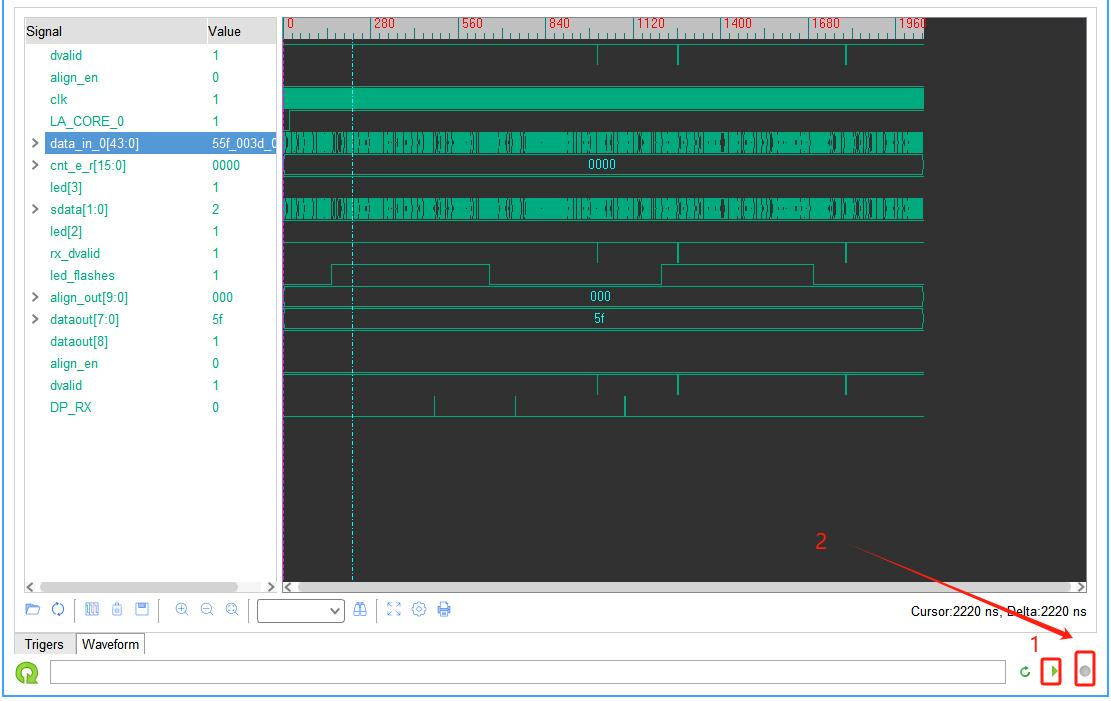

2.12.控制 ①开始 ②停止 按钮分析波形,配合触发和放大缩小,分

析各个信号时序,波形文件也可以另外保存,尾缀.vcd;

至此,完成 Debugware IP 的使用和波形分析操作。

介绍完毕,动手操作!!!