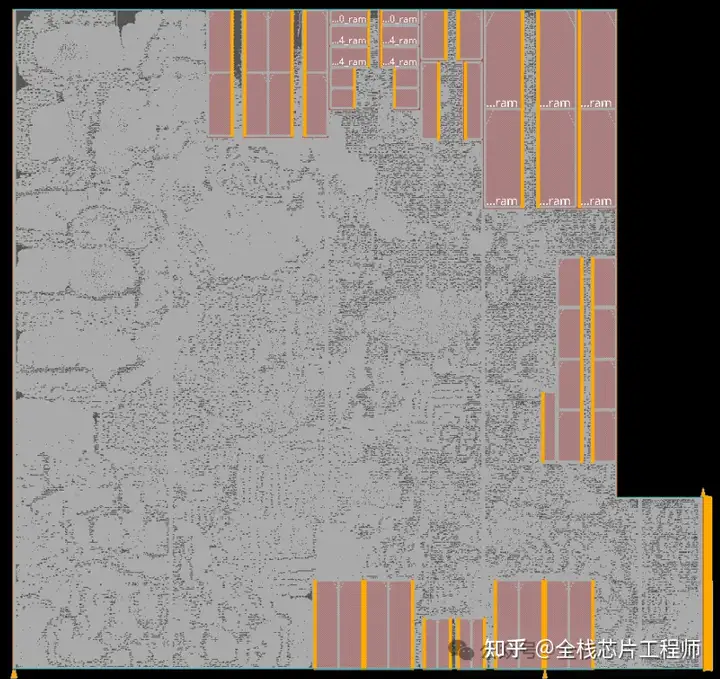

innovus的ctslog中的Clock DAG信息可以报出来CTS主要运行步骤的关键信息,比如clustering,balancing做完后的clock tree的长度,clock tree上所用的buffer、inverter,icg cell数量,clock skew等信息。我们以景芯SoC A72 TOP项目的maia_cpu core为例:

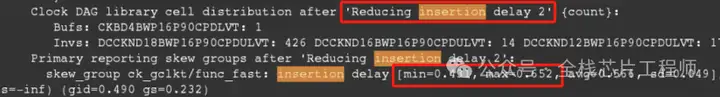

从clustering到balancing,clock ID(insertion delay)和buffer数量大幅增加,这是由于比如一些sinks存在于不同的skew groups,为了平衡skew group之间的skew,就会插入buffer并做大了clock ID,因此我们需要确认skew group的存在是否合理。

抓取cts.log中的Clock DAG

grep -E -A2 "Clock DAG" cts.log >> SoC_cts_Clock DAG.rpt

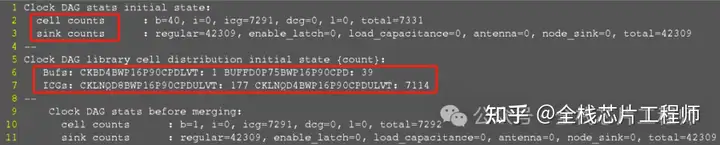

可以看到cell、sink的counts,也可以看到BUF、ICG的数量,接下来我们来看看景芯SoC A72 TOP的CLOCK ID和BUF个数的变化吧。

先看下景芯SoC A72项目的cts latency变化过程。将Clock DAG和Primary reporting一起抓出来:

grep -E -A2 "Clock DAG|Primary reporting" cts.log >> SoC_cts_latency_debug.rpt

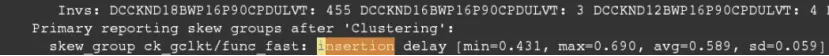

打开报告SoC_cts_latency_debug.rpt,Clustering之后,IDmin=0.431 IDmax=0.690

Reducing insertion delay后:IDmax从0.690降低到了0.652

Balancing后:IDmin从0.431升到了0.569,而IDmax从0.652略微降低到了0.648

请思考,为何Balancing后:IDmin从0.431升到了0.569?