描述

Xilinx 7系列FPGA和UltraScale体系结构提供了高性能(HP)和

高范围(HR)I/O组。I/O库是I/O块(IOB)的集合,具有可配置的

SelectIO驱动程序和接收器,支持多种标准接口

单端和差分。HP I/O组旨在满足性能要求

电压高达的高速存储器和其他芯片到芯片接口的要求

1.8伏。人力资源I/O库旨在支持更广泛的I/O标准

电压高达3.3V。

每个I/O组都包括片上输出强度和转换速率的可编程控制

使用数字控制阻抗(DCI)的终端,以及内部

产生参考电压(INTERNAL_VREF)。

在UltraScale设备中,大多数I/O组由52个IOB组成,尽管HR I/O是小型组

由26个IOB组成。而在7系列设备中,大多数I/O组包括50个IOB,这与

时钟区域的高度。设备上I/O组的数量取决于大小

以及封装引脚。

有关I/O组以及与I/O分配相关的规则的更多信息,请参阅7

系列FPGA SelectIO资源用户指南(UG471)[参考文献2]和UltraScale体系结构

选择IO资源用户指南(UG571)[参考文献8]。

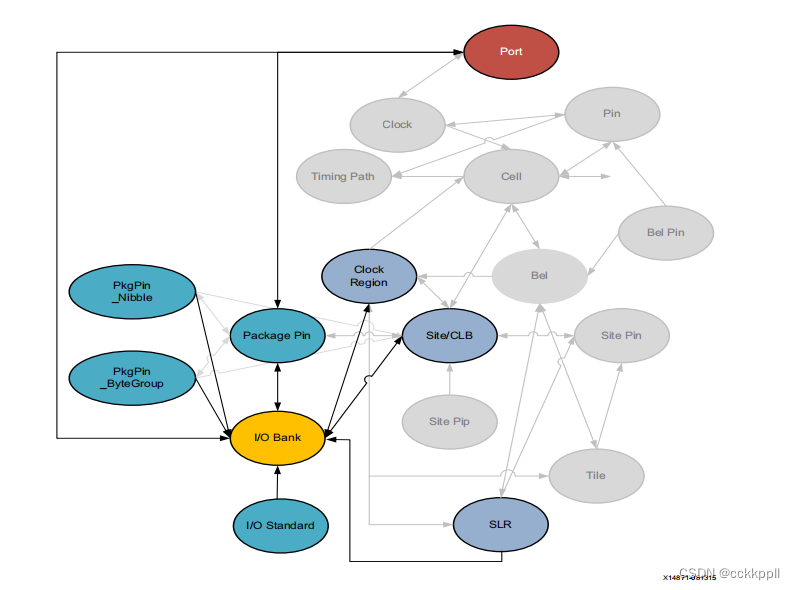

相关对象

从第104页的图2-27中,您可以看到I/O组与端口网表对象相关,

设备的package_pin和由I/O块实现的I/O标准。

您可以获得相关的package_pins、端口、时钟区域或站点的io_banks:

get_iobanks-of[get_clock_regions X0Y2]

您还可以查询端口、clock_region、站点、SLR、I/O标准、package_pin、,

pkgpin_bytegroup和与I/O组相关联的pkgpin_nibble对象:

get_sites-of[get_iobanks 227]

属性

在I/O Bank对象上找到的属性如下,其中包含示例值:

Property Type Read-only Value

BANK_TYPE string true BT_HIGH_PERFORMANCE

CLASS string true iobank

DCI_CASCADE string* false

INTERNAL_VREF double false

IS_MASTER bool true 0

IS_SLAVE bool true 0

MASTER_BANK string true

NAME string true 46

VCCOSENSEMODE string false

The properties of an io_bank can be listed with the following command:

report_property -all [lindex [get_iobanks] 0]

描述

IO_STANDARD对象定义目标Xilinx支持的可用IOSTANDARD

装置IO_STANDARD对象可以通过

IOSTANDARD属性,用于配置当前中的输入、输出或双向端口

设计有关支持标准的更多信息,请参阅7系列FPGA SelectIO

资源用户指南(UG471)[参考文献2]和UltraScale体系结构SelectIO资源用户

指南(UG571)[参考文献8]。

相关对象

您可以查询与特定BEL、SITE、PACKAGE_PIN关联的IO_STANDARD,

IO_BANK或感兴趣的PORT:

get_io_standards-[get_ports ddr4_sdram_dm_n[0]的

您还可以查询实现特定IO_STANDARD的PORT对象:

get_ports-of[get_io_standards POD12_DCI]

提示:在这种情况下,还可以通过查看IOSTANDARD属性来找到端口:

get_ports-筛选器{IOSTANDARD==POD12_DCI}

属性

在package_pin对象上找到的属性如下,其中包含示例值:

Property Type Read-only Value

CLASS string true io_standard

DIRECTION string true INPUT OUTPUT BIDIR

DRIVE_STRENGTH string true NA

HAS_VCCO_IN bool true 1

HAS_VCCO_OUT bool true 1

HAS_VREF bool true 1

INPUT_TERMINATION string true SINGLE

IS_DCI bool true 1

IS_DIFFERENTIAL bool true 0

NAME string true POD12_DCI

OUTPUT_TERMINATION string true DRIVER

SLEW string true SLOW MEDIUM FAST

SUPPORTS_SLEW bool true 0

VCCO_IN double true 1.200

VCCO_OUT double true 1.200

VREF double true 0.840

The properties of package_pin objects can be listed with the following command:

report_property -all [lindex [get_io_standards] 0]