个人名片:

🎓作者简介:嵌入式领域优质创作者

**🌐个人主页:**妄北y**📞个人QQ:**2061314755

💌个人邮箱: [mailto:2061314755@qq.com]

📱**个人微信:**Vir2025WBY

🖥️个人公众号: 科技妄北

🖋️本文为妄北y原创佳作,独家首发于CSDN🎊🎊🎊

**💡座右铭:**改造世界固然伟大,但改造自我更为可贵。

专栏导航:

妄北y系列专栏导航:

物联网嵌入式开发项目:大学期间的毕业设计,课程设计,大创项目,各种竞赛项目,全面覆盖了需求分析、方案设计、实施与调试、成果展示以及总结反思等关键环节。📚💼💡

QT基础入门学习:对QT的基础图形化页面设计进行了一个简单的学习与认识,利用QT的基础知识进行了翻金币小游戏的制作。🛠️🔧💭

Linux基础编程:初步认识什么是Linux,为什么学Linux,安装环境,进行基础命令的学习,入门级的shell编程。🍻🎉🖥️

深耕Linux应用开发:分享Linux的基本概念、命令行操作、文件系统、用户和权限管理等,网络编程相关知识,TCP/IP 协议、套接字(Socket)编程等,可以实现网络通信功能。常见开源库的二次开发,如libcurl、OpenSSL、json-c、freetype等💐📝💡

Linux驱动开发:Linux驱动开发是Linux系统不可或缺的组成部分,它专注于编写特殊的程序------驱动程序。这些程序承载着硬件设备的详细信息,并扮演着操作系统与硬件间沟通的桥梁角色。驱动开发的核心使命在于确保硬件设备在Linux系统上顺畅运作,同时实现与操作系统的无缝集成,为用户带来流畅稳定的体验。🚀🔧💻

Linux项目开发:Linux基础知识的实践,做项目是最锻炼能力的一个学习方法,这里我们会学习到一些简单基础的项目开发与应用,而且都是毕业设计级别的哦。🤸🌱🚀

非常期待与您一同在这个广阔的互联网天地里,携手探索知识的海洋,互相学习,共同进步。🌐💫🌱 熠熠星光,照亮我们的成长之路

✨✨欢迎订阅本专栏,对专栏内容任何问题都可以随时联系博主,共同书写属于我们的精彩篇章!✨✨

文章介绍:

📚本篇文章将深入剖析嵌入式学习的精髓与奥秘,与您一同分享相关知识!🎉🎉🎉

若您觉得文章尚可入目,期待您能慷慨地送上点赞、收藏与分享的三连支持!您的每一份鼓励,都是我创作路上源源不断的动力。让我们携手并进,共同奔跑,期待在顶峰相见的那一天,共庆辉煌!🚀🚀🚀

🙏衷心感谢大家的点赞👍、收藏⭐和评论✍️,您的支持是我前进的动力!

前些天发现了一个巨牛的人工智能学习网站,通俗易懂,风趣幽默,忍不住分享一下给大家。点击跳转到网站:人工智能教程

目录:

一、选择题:

1.计算机系统由硬件和软件两大部分构成,下列属于计算机系统硬件的是( )。

A.编译工具

B.操作系统

C.输入/输出接口

D.设备驱动程序

计算机系统由硬件和软件两大部分构成。硬件是指计算机的物理组件,如中央处理器(CPU)、内存、硬盘、显示器、键盘、鼠标等。软件则是指运行在硬件上的程序和数据,包括操作系统、应用程序、设备驱动程序等。

选项分析:

A. 编译工具 - 这是一种软件 ,用于将高级语言编写的程序转换成机器语言,属于软件范畴。

B. 操作系统 - 这也是一种软件 ,负责管理计算机硬件与软件资源,提供用户与计算机硬件之间的接口,属于软件范畴。

C. 输入/输出接口 - 这是硬件的一部分 ,负责连接计算机与外部设备,如键盘、鼠标、打印机等,属于硬件范畴。

D. 设备驱动程序 - 这是一种软件,用于控制和管理硬件设备的操作,属于软件范畴。

因此,正确答案是 C. 输入/输出接口。

答案:C

2.MIPS通常用来描述计算机的运算速度,其含义是() 。

A.每秒执行百万条指令

B.每分钟处理百万个字符

C.每分钟执行百万条指令

D.每秒处理百万个字符

MIPS 是 "Millions of Instructions Per Second" 的缩写,直译为"每秒百万条指令"。这个术语用来衡量计算机或处理器每秒钟能够执行的机器指令数量,通常用来描述处理器的运算速度。

选项分析:

A. 每秒执行百万条指令 - 这是 MIPS 的正确含义。

B. 每分钟处理百万个字符 - 这个选项描述的是处理字符的速度,而不是指令执行速度。

C. 每分钟执行百万条指令 - 这个选项的时间单位是分钟,而不是秒,因此不正确。

D. 每秒处理百万个字符 - 这个选项描述的是处理字符的速度,而不是指令执行速度。

因此,正确答案是 A. 每秒执行百万条指令。

答案:A

3.和冯·诺依曼结构相比,哈佛结构最本质的特点是〈)。

A.提高了处理器的频率

B.指令存储和数据存储分开,使用两套独立总线访问

C.程序无需存储在存储器中

D.增加了指令的数目

哈佛结构(Harvard architecture)和冯·诺依曼结构(Von Neumann architecture)是两种不同的计算机体系结构。

**冯·诺依曼结构的特点是使用单一的存储器来存储指令和数据,并且使用单一的总线来传输指令和数据。**这种结构简单且成本较低,但指令和数据的传输可能会相互干扰,影响处理速度。

**哈佛结构的特点是指令存储和数据存储是分开的,各自拥有独立的存储器和总线系统。**这意味着指令和数据可以同时被访问,从而提高了处理速度和效率。

选项分析:

A. 提高了处理器的频率 - 这个选项描述的是处理器性能的一个方面 ,但不是哈佛结构最本质的特点。

B. 指令存储和数据存储分开,使用两套独立总线访问 - 这是哈佛结构最本质的特点。

C. 程序无需存储在存储器中 - 这个选项不正确,无论是哈佛结构还是冯·诺依曼结构,程序都需要存储在存储器中。

D. 增加了指令的数目 - 这个选项描述的是指令集的复杂性,而不是哈佛结构的特点。

因此,正确答案是 B. 指令存储和数据存储分开,使用两套独立总线访问。

4.世界上第一台计算机研制成功的年代是〈 )。

A. 1944年

B. 1945年

C. 1946年

D. 1947年

世界上第一台通用电子数字计算机是ENIAC (Electronic Numerical Integrator And Computer),它于**1946年2月14日在美国宾夕法尼亚大学研制成功。**ENIAC最初是为了计算弹道表而设计的,但它后来被用于各种科学和工程计算。

答案:C

5.微软开发的嵌入式操作系统是( ) 。

A. RT-Linux

B. Monta Vista

C. Windows CE

D. vxWorks

答案:C

6.在嵌入式系统设计中,嵌入式处理器选型是在进行()时完成。

A.需求分析

B.系统集成

C.体系结构设计

D.软硬件设计

在嵌入式系统设计过程中,**嵌入式处理器选型是一个关键步骤,它通常在体系结构设计阶段完成。**体系结构设计阶段涉及确定系统的整体结构,包括硬件和软件的划分,以及选择合适的处理器和其他关键组件。

A. 需求分析 - 在这个阶段,设计者主要关注用户需求和系统功能, 但尚未进行具体的硬件选型。

B. 系统集成 - 这个阶段通常是在硬件和软件设计完成后的整合阶段 ,此时处理器选型已经完成。

C. 体系结构设计 - 在这个阶段,设计者会根据系统需求和性能要求选择合适的处理器 ,因此这是正确的阶段。

D. 软硬件设计 - 这个阶段是在处理器选型之后,具体进行硬件设计和软件编程的阶段。

答案:C

7.以下不是引导程序的是〈 )。

A. VIVI

B.U-Boot

C.BLOB

D.RT-Linux

引导程序(Bootloader)是计算机启动时运行的程序,它的主要任务是初始化硬件设备、建立内存空间的映射,以及将操作系统加载到内存中并启动它。

选项分析:

A. VIVI - VIVI是一个为ARM处理器设计的引导程序 ,通常用于嵌入式系统。

B. U-Boot -U-Boot(Universal Bootloader)是一个广泛使用的开源引导程序 ,支持多种处理器架构。

C. BLOB - BLOB(Boot Loader Object)是一个为PowerPC处理器设计的引导程序 ,主要用于嵌入式系统。

D. RT-Linux - RT-Linux(Real-Time Linux)是一个实时操作系统,它不是一个引导程序,而是一个完整的操作系统,旨在提供实时性能。

因此,正确答案是 D. RT-Linux,因为它是一个操作系统,而不是一个引导程序。

答案:D

8.程序计数器PC是CPU内部的一种专用寄存器,其中存放的是( ) 。

A.下一条待取指令的存放地址

B.当前执行指令的存放地址

C.指令

D.数据

程序计数器(Program Counter, PC)**是CPU内部的一个专用寄存器,它的主要功能是存储下一条待取指令的内存地址。**在大多数计算机体系结构中,CPU会根据PC中的地址从内存中取出指令,然后执行该指令,并在执行完毕后更新PC的值,使其指向下一条指令的地址。

选项分析:

A. 下一条待取指令的存放地址 - 这是程序计数器PC的正确功能。

B. 当前执行指令的存放地址 - 这个描述不准确**,因为当前执行的指令地址在取指令时会被加载到指令寄存器中,而不是存储在PC中** 。

C. 指令 -指令本身不是存储在PC中的,PC存储的是指令的地址 。

D. 数据 - PC不存储数据,它存储的是指令地址。

答案:A

9.Cortex-M3采用()。

A.3级流水线结构

B.4级流水线结构

C.6级流水线结构

D.8级流水线结构

Cortex-M3是ARM公司设计的一款32位微控制器内核,它采用了3级流水线结构。流水线是一种提高处理器性能的技术,它允许不同的指令在不同的阶段同时进行处理。在Cortex-M3中,这3级流水线包括:

取指(Fetch):从内存中取出下一条指令。

解码(Decode):解码取出的指令,确定需要执行的操作。

执行(Execute):执行解码后的指令,可能包括从寄存器读取数据、进行算术或逻辑运算、写回结果到寄存器或内存等操作。

这种3级流水线结构相对简单,有助于减少流水线停顿和提高指令执行效率,尤其是在嵌入式系统和实时应用中。

因此,正确答案是 A. 3级流水线结构。

答案:A

10.关于ARM子程序和Thumb子程序互相调用描述正确的是( )。

A.系统初始化之后,ARM处理器只能工作在一种状态,不存在互相调用。

B.只要遵循一定调用的规则,Thumb子程序和ARM子程序就可以互相调用。

C.只要遵循一定调用的规则,仅能Thumb子程序调用ARM子程序。

D.只要遵循一定调用的规则,仅能ARM子程序调用Thumb子程序。

**ARM和Thumb是ARM架构中的两种不同的指令集模式。ARM模式使用32位的指令集,而Thumb模式使用16位的指令集,后者旨在提供更高的代码密度和更低的功耗。**在ARM架构中,这两种模式是可以互相切换的,这意味着ARM子程序和Thumb子程序可以互相调用,但需要遵循特定的调用规则和约定。

选项分析:

A. 系统初始化之后,ARM处理器只能工作在一种状态,不存在互相调用。 - 这个描述不正确,因为ARM处理器可以在ARM和Thumb模式之间切换,允许互相调用 。

B. 只要遵循一定调用的规则,Thumb子程序和ARM子程序就可以互相调用。 - 这个描述是正确的,ARM和Thumb子程序可以通过使用适当的调用约定(如使用BX或BLX指令)来互相调用。

C. 只要遵循一定调用的规则,仅能Thumb子程序调用ARM子程序。 - 这个描述不正确,因为ARM子程序也可以调用Thumb子程序。

D. 只要遵循一定调用的规则,仅能ARM子程序调用Thumb子程序。 - 这个描述不正确,因为Thumb子程序也可以调用ARM子程序。

因此,正确答案是 B. 只要遵循一定调用的规则,Thumb子程序和ARM子程序就可以互相调用。

答案:B

11.微处理器内部标志寄存器(或称为程序状态寄存器〉的主要作用是()。

A.纠正当前指令执行的结果

B.用于判断当前指令是否正确执行

C.反映处理器的状态和ALU运算结果的某些特征

D.决定CPU是否继续工作

微处理器内部标志寄存器(或称为程序状态寄存器,通常简称为PSR或FLAGS)的主要作用是**反映处理器的状态和算术逻辑单元(ALU)运算结果的某些特征。**这些特征通常包括但不限于:

零标志(ZF):当运算结果为零时,该标志被设置。

负标志(SF):当运算结果的最高位为1时,表示结果为负数,该标志被设置。

溢出标志(OF):当算术运算结果超出了数据类型所能表示的范围时,该标志被设置。

进位标志(CF):当算术运算产生进位或借位时,该标志被设置。

奇偶标志(PF):当运算结果的最低有效字节中1的个数为偶数时,该标志被设置。

这些标志位用于条件分支指令,允许程序根据上一条指令的执行结果来决定程序的流程。例如,如果一个比较指令执行后零标志被设置,那么程序可能会跳转到某个特定的代码段。

选项分析:

A. 纠正当前指令执行的结果 -标志寄存器不用于纠正指令执行的结果,而是用于记录结果的特征。

B. 用于判断当前指令是否正确执行 - 标志寄存器反映的是运算结果的特征,而不是指令执行的正确性。

C. 反映处理器的状态和ALU运算结果的某些特征 - 这是标志寄存器的正确作用。

D. 决定CPU是否继续工作 - 标志寄存器不直接决定CPU是否继续工作,但它可以影响程序的执行流程。

因此,正确答案是 C. 反映处理器的状态和ALU运算结果的某些特征。

答案:C

- ARM的启动向量是()

A. 0xffffffff

B. 0x00000000

c. 0x11110000

D. 0x0000ffff

在ARM架构中,**启动向量(也称为复位向量)是指在处理器复位后,程序计数器(PC)被设置的地址。**这个地址指向的是处理器启动时执行的第一条指令的位置。

对于大多数基于ARM架构的处理器,启动向量通常是固定的,并且位于特定的内存地址。在早期的ARM处理器中,启动向量通常是0x00000000。然而,随着ARM架构的发展,这个地址可能会有所不同,特别是在具有安全扩展(如TrustZone)的处理器中,启动向量可能会指向一个安全状态的地址。

选项分析:

A. 0xffffffff - 这个地址通常不是ARM处理器的启动向量。

B. 0x00000000 - 这个地址是许多基于ARM架构的处理器传统的启动向量。

C. 0x11110000 - 这个地址不是ARM处理器的标准启动向量。

D. 0x0000ffff - 这个地址不是ARM处理器的标准启动向量。

因此,正确答案是 B. 0x00000000。

13.ARM访问特殊功能寄存器的方法与访问下列()设备一致。

A.寄存器

B. Cache

C.内存

D.以上都不对

在ARM架构中**,特殊功能寄存器(Special Function Registers, SFRs)通常用于控制和配置处理器的行为**,例如中断控制、时钟配置、电源管理等。这些寄存器通常不是通过普通的内存映射I/O(Memory-Mapped I/O)来访问的,而是通过特定的指令或地址空间来访问。

选项分析:

A. 寄存器 - 这个选项不准确,因为特殊功能寄存器不是通过访问通用寄存器的方式来访问的。

B. Cache - 特殊功能寄存器的访问与Cache的访问方式不同,Cache是用于存储内存数据的快速存储器,而特殊功能寄存器是用于控制处理器行为的。

C. 内存 - 在某些ARM处理器中,特殊功能寄存器是通过内存映射的方式来访问的,这意味着它们被映射到特定的内存地址空间,可以通过访问内存的方式来读写这些寄存器。

D. 以上都不对 - 如果C选项是正确的,那么这个选项就是错误的。

因此,正确答案是 C. 内存。

在ARM架构中,特殊功能寄存器通常是通过内存映射的方式来访问的,这与访问内存设备的方式一致。然而,需要注意的是,并非所有的ARM处理器都使用内存映射的方式来访问特殊功能寄存器,有些处理器可能使用其他机制,如专用指令或特定的地址空间。因此,具体情况应参考相应处理器的文档。

答案:C

14.ARM汇编指令SUB R0,R1,R2,LSR#2中,LSR的含义是()。

A.算术左移

B.算术右移

C.逻辑右移

D.逻辑左移

在ARM汇编指令中,`LSR` 表示逻辑右移(Logical Shift Right)。逻辑右移操作会将操作数的每一位向右移动指定的位数,左边空出的位用0填充。

选项分析:

A. 算术左移 - 这个选项描述的是`LSL`(Logical Shift Left)操作,不是`LSR`。

B. 算术右移 - 这个选项描述的是`ASR`(Arithmetic Shift Right)操作,不是`LSR`。算术右移在右移时会保持最高位(符号位)不变,以保持数的正负性。

C. 逻辑右移 - 这个选项正确描述了`LSR`的含义。

D. 逻辑左移 - 这个选项描述的是`LSL`(Logical Shift Left)操作,不是`LSR`。

因此,正确答案是 C. 逻辑右移。在指令 `SUB R0, R1, R2, LSR#2` 中,`R2` 的值首先会被逻辑右移2位,然后这个结果会从 `R1` 中减去,结果存入 `R0`。

答案:C

15.ADDR0,R1,#3属于( ) 。

A.立即寻址

B.多寄存器寻址

C.寄存器直接寻址

D.相对寻址

**在ARM汇编指令中,

ADD R0, R1, #3是一条加法指令,它将寄存器R1的值与立即数3相加,并将结果存储在寄存器R0中。**这条指令的寻址方式是立即寻址,因为操作数之一是一个立即数(即直接包含在指令中的常数)。选项分析:

A. 立即寻址 - 这个选项正确描述了指令的寻址方式。

B. 多寄存器寻址 - 这个选项不适用,因为指令只涉及两个寄存器和一个立即数,没有涉及多个寄存器。

C. 寄存器直接寻址 - 这个选项不准确,因为虽然指令中使用了寄存器,但其中一个操作数是立即数,所以不是纯粹的寄存器直接寻址。

D. 相对寻址 - 这个选项不适用,因为指令没有使用程序计数器(PC)的相对地址。

因此,正确答案是 A. 立即寻址。

答案:A

- 指令寻址方式通常是指获取()的方式。

A.操作数或者操作数地址

B.内存单元

C.指令地址

D.指令内容

**指令寻址方式通常是指获取操作数或者操作数地址的方式。**在计算机体系结构中,寻址方式定义了如何计算出操作数的有效地址,以便执行指令。这些操作数可以是立即数、寄存器中的值,或者是内存中的数据。

选项分析:

A. 操作数或者操作数地址 - 这个选项正确描述了指令寻址方式的目的。

B. 内存单元 - 这个选项过于狭窄,因为指令寻址方式不仅涉及内存单元,还包括寄存器和立即数。

C. 指令地址 - 这个选项不准确,因为指令寻址方式通常不涉及指令本身的地址,而是操作数的地址。

D. 指令内容 - 这个选项不准确,因为指令寻址方式关注的是如何获取操作数,而不是指令本身的内容。

因此,正确答案是 A. 操作数或者操作数地址。

答案:C

17.ARM中可以访问状态寄存器的指令是( )。

A. MRS

B. MCS

C. LDR

D. STM

答案:D

- PWM定时器的时钟信号为() 。

A. FCLK

B.HCLK

C. UCLK

D. PCLK

在ARM架构中,PWM(脉冲宽度调制)定时器的时钟信号通常是 `PCLK`。`PCLK` 是外设时钟(Peripheral Clock)的缩写,它为外设提供时钟信号,包括定时器和PWM模块。

选项分析:

A. FCLK - 这个选项不正确**,`FCLK` 是ARM内核的主时钟** ,通常用于CPU操作,而不是外设。

B. HCLK - 这个选项不正确,`HCLK` 是高速总线时钟, 通常用于AHB总线上的设备,但不一定直接用于PWM定时器。

C. UCLK - 这个选项不正确,`UCLK` 通常指的是USB时钟 ,与PWM定时器无关。

D. PCLK - 这个选项正确,`PCLK` 是外设时钟,为外设提供时钟信号,包括PWM定时器。

因此,正确答案是 D. PCLK。

答案:D

19.定时器0和1共用一个8位预分频器,预分频器是可编程的,定时器1的预分频值存储在寄存器〈〉中。

A. TCFG1

B. TCNTB1

C. TCFG0

D.TCMPB1

答案:C

20.片选信号nGCsn结束后,地址信号保持的时间为()。

A. Tacs

B. Tcos

C. Tcoh

D. Tcah

在存储器接口中,片选信号(nGCSn)结束后,地址信号保持的时间通常由特定的时序参数决定。这些参数可能包括:

A. Tacs (Address Set-up Time) - 地址建立时间,指的是在片选信号有效之前,地址信号需要稳定的时间。

B. Tcos (Chip Select Set-up Time) - 片选信号建立时间,指的是在片选信号有效之前,片选信号需要稳定的时间。

C. Tcoh (Chip Select Hold Time) -片选信号保持时间,指的是在片选信号无效之后,片选信号需要保持稳定的时间。

D. Tcah (Address Hold Time) - 地址保持时间,指的是在片选信号无效之后,地址信号需要保持稳定的时间。

根据问题描述,片选信号nGCsn结束后,地址信号保持的时间应该是地址保持时间。

因此,正确答案是 D. Tcah。这个参数确保在片选信号无效后,地址信号仍然保持稳定,以便存储器能够正确地响应。

答案: D

21.关于NOR Flash的描述,下列哪一个是错误的( )。

A.带有SRAM接口

B.支持Execute Chip技术

C.可以直接进行写操作

D.可以作为引导ROM

选项分析:

A. 带有SRAM接口 - 这个描述是正确的。NOR Flash通常具有与SRAM相似的接口,包括地址线和数据线,这使得它可以很容易地与微处理器或微控制器连接。

B. 支持Execute In Place (XIP) 技术 - 这个描述也是正确的。NOR Flash的一个关键特性是它支持XIP技术,这意味着代码可以直接在Flash存储器中执行,而不需要先将代码复制到RAM中。

C. 可以直接进行写操作 - 这个描述是错误的。虽然NOR Flash可以被写入,但它不能像RAM那样直接进行写操作。写入NOR Flash通常需要一个特定的编程过程,包括擦除操作,因为Flash存储器是基于浮栅晶体管的,需要通过电子隧穿来改变其状态。

D. 可以作为引导ROM - 这个描述是正确的。由于NOR Flash支持XIP技术,它可以被用作引导ROM,允许处理器直接从Flash中加载并执行启动代码。

因此,错误描述的选项是 C. 可以直接进行写操作。正确答案是 C。

答案: C

22.S3C2440A IO口常用的控制器是( )。

A.端口控制寄存器(GPACON-GPHCON)

B.端口数据寄存器(GPADAT-GPHDAT)

C.外部中断控制寄存器(EXTINTN)

D.以上都是

S3C2440A是一款由三星电子生产的基于ARM920T核心的微处理器**。它具有多个通用输入输出(GPIO)端口,每个端口都可以通过相应的控制寄存器进行配置和控制。**

A. 端口控制寄存器(GPACON-GPHCON) -这些寄存器用于配置GPIO端口的功能,例如设置某个引脚为输入、输出或其他特殊功能。

B. 端口数据寄存器(GPADAT-GPHDAT) - 这些寄存器用于读取或写入GPIO端口的数据,即引脚的状态。

C. 外部中断控制寄存器(EXTINTN) - 这些寄存器用于配置外部中断的触发方式,例如边沿触发或电平触发。

在S3C2440A中,上述所有寄存器都是常用的控制器,用于管理和控制IO口的行为。因此,正确答案是 D. 以上都是。

答案: D

23.嵌入式系统最常用的数据传送方式是〈 )。

A.查询

B.中断

C. DMA

D. I/O处理机

嵌入式系统中,数据传送方式的选择取决于系统的具体需求和设计。以下是每种传送方式的

简要说明:

A. 查询 - **在这种方式中,处理器不断地检查外设的状态,直到外设准备好进行数据传送。**这种方式简单,但效率较低,因为处理器可能会花费大量时间等待外设准备就绪。

B. 中断 - **当外设准备好进行数据传送时,它会向处理器发送一个中断信号。处理器在接收到中断信号后,会暂停当前任务,转而处理中断服务例程,完成数据传送。**这种方式比查询方式效率高,因为它允许处理器在等待外设准备就绪时执行其他任务。

C. DMA(直接内存访问) - **DMA允许外设直接与内存进行数据传送,而不需要处理器介入。**这种方式特别适合大量数据的高速传送,可以显著提高系统效率,减少处理器的负担。

D. I/O处理机 - 这是一种专用处理器,用于管理和执行I/O操作。它可以在不涉及主处理器的情况下处理数据传送,从而释放主处理器以执行其他任务。

在嵌入式系统中,最常用的数据传送方式通常是中断和DMA。中断适用于需要处理器响应的事件驱动型数据传送,而DMA适用于大量数据的高速传送。因此,最常用的数据传送方式可能是中断和DMA的组合。然而,如果必须选择一个最常用的方式,那么中断(B)可能是更常见的选择,因为它适用于更广泛的应用场景,并且实现起来相对简单。

答案: B

24.SPI通信接口中,主设备的MOSI引脚与从设备的()引脚连接。

A. MOSO

B. MISO

C. MOSI

D.MISI

在SPI(Serial Peripheral Interface)通信中,主设备(Master)和从设备(Slave)之间通过四条线进行通信:

MISO(Master In Slave Out):主设备输入,从设备输出。

MOSI(Master Out Slave In):主设备输出,从设备输入。

SCLK(Serial Clock):时钟信号,由主设备产生。

SS(Slave Select)或CS(Chip Select):从设备选择信号,由主设备控制。

在SPI通信中,主设备的MOSI引脚用于发送数据到从设备,因此从设备需要一个对应的引脚来接收这些数据。这个引脚通常被称为MISO(Master In Slave Out),即从设备输出到主设备的引脚。

答案: C

25.下面关于Linux内核的有关叙述中,错误的是( ) 。

A.进程调度模块负责控制进程对CPU资源的使用,所采取的调度策略是使得各个进程能够平均访问CPU,但并不保证内核能及时地执行硬件操作。

B.Linux内存管理模块的功能之一是屏蔽各种硬件内存结构的差异并向上返回统一的访问接口。

C.网络接口模块包含网络接口驱动程序。

D.支持进程之间各种通信机制,其通信机制主要包括信号、管道、消息队列、信号量、共享内存和套接字。

选项A中的叙述是错误的**。Linux内核的进程调度模块确实负责控制进程对CPU资源的使用,并且可以采取多种调度策略,如时间片轮转、优先级调度等。然而,这些调度策略的目的并不仅仅是使得各个进程能够平均访问CPU,而是要根据系统的运行情况和进程的优先级来合理分配CPU资源,以提高系统的整体性能和响应速度。**此外,内核确实需要及时地执行硬件操作,以确保系统的稳定性和性能。因此,选项A中的叙述"并不保证内核能及时地执行硬件操作"是不正确的。

选项B、C和D的叙述都是正确的:

B. Linux内存管理模块确实屏蔽了各种硬件内存结构的差异,并提供了统一的访问接口,使得上层应用不需要关心底层硬件的具体实现。

C. 网络接口模块确实包含网络接口驱动程序,这些驱动程序负责与硬件通信,实现网络数据的收发。

D. Linux内核支持进程之间的各种通信机制,包括信号、管道、消息队列、信号量、共享内存和套接字等,这些机制是实现进程间通信和同步的重要手段。

因此,错误的是选项A。

答案:A

26.GPIO不可以实现以下功能() 。

A.感知外部开关量信号

B.感知外部世界模拟量的大小

C.输出驱动LED灯

D.仿真实现特定的功能接口

GPIO(General Purpose Input/Output)是通用输入输出端口的简称,它是一种可以由用户编程控制的数字信号接口。GPIO通常用于连接和控制外部设备,如传感器、开关、LED灯等。

A. 感知外部开关量信号:GPIO可以作为输入端口,用来检测外部开关量信号,如按钮是否被按下。

B. 感知外部世界模拟量的大小:这个选项是错误的。GPIO通常只能处理数字信号,即高电平(通常是3.3V或5V)和低电平(通常是0V)。如果需要感知模拟量的大小,通常需要使用模数转换器(ADC)来将模拟信号转换为数字信号,然后才能由GPIO或其他数字接口处理。

C. 输出驱动LED灯:GPIO可以作为输出端口,用来控制LED灯的亮灭,通过输出高电平或低电平来驱动LED。

D. 仿真实现特定的功能接口:GPIO可以通过编程来模拟实现特定的功能接口,例如通过GPIO模拟I2C、SPI等通信协议。

因此,GPIO不可以实现的功能是感知外部世界模拟量的大小,正确答案是B。

答案:B

二、填空题

1.嵌入式系统的实时性分为软实时和_____。

答案:硬实时

2.从层次角度来看,嵌入式系统由四大部分组成,分别是:应用软件层、操作系统层、板级支持包〈或硬件抽象层〉和_____。

答案:硬件层

3.实时系统的关键问题是保证系统的____。

答案:实时性

4.系统的需求一般分功能性需求和_____两方面。

答案:非功能性需求

5.在大端模式存储的情况下,0x1234abcd中存储在最低地址的数据为_____。

答案:0x12

6.用户模式下的可见通用寄存器个数为___个。(填写一个阿拉伯数字)

答案:16

7.S3C2440A中,其地址空间有______个BANK,每个BANK最大的容量128M。

答案:8

8.标明本段程序是代码段伪指令是____。

答案:CODE

9.ARM系列处理器通过执行BX或者_______指令来实现工作状态的切换。

答案: BLX

10._____是用于功率器件中的PWAM控制。此功能允许在开关器件关闭与另一个开关器件的开启之间插入一个小的时间间隙。这个间除禁止同时开启两个开关器件,即使是在非常短的时间也不允许。

答案:死区

11.当对Fash中的某个存储位擦写一定次数后(理论上约10~-100万次》,这个位就会变得不可靠或失效。为了避免在存储过程中对某些位的集中擦写,通常都会使用_____技术,以实现对所有位的擦写次数是均匀的,从而延长存储器的使用寿命。(填四个字)

答案:磨损均衡

12.外部中断源的触发信号方式是多种的,可以为低电平触发、高电平触发、方式下降沿触发、上升沿触发或______。

答案:双边沿触发

13.UART的帧格式由四部分组成,包括:起始位、_____、奇偶校验位和停止位。

答案:数据位

14.LCDCDMA中存在____个字的FIFO存储器。

答案:28

15.嵌入式系统开发时,由于受到目标机资源的限制,需要建立一个_____与目标机组成的调试架构来完成开发工作。

答案:宿主机

三、判断题:

1.嵌入式系统是与应用紧密结合的,它具有很强的专用性,必须结合实际系统需求,进行合理的裁减利用。

答案:√

2.嵌入式系统分为微控制器与应用处理器两大类。

答案:X

3.当程序直接改写CPSR来切换模式时,CPSR会被复制到SPSR。

答案:X

4.Cortex-M4发生异常时,进入处理工作模式。

答案:√

5.程序运行过程中的资源可以是显示器、键盘,但不可以是一个数组或变量。

答案:X

6.CMN指令用于2个操作数分别取反后进行比较,同时更新CPSR中条件标志位的值。

答案:√

7.芯片内部时钟比外部时钟更稳定、可靠。

答案:X

8.PWM定时器可以作通用定时器使用。

答案:√

9.SRAM读写时,片选信号要先于数据信号给出。

答案:X

10.DMA与CPU交替访问内存的DMA数据传输方法的效率要优于周期挪用的DMA数据传输方法。

答案:X

11.上/下拉输入是指将GPIO设置成为输入管脚,管脚外侧配置上/下拉电路。

答案:X

12.I2C采用全双工的方式进行通信。

答案:X

13.宿主机和目标板的处理器一般不相同,宿主机为Intel处理器,而目标板可以是嵌入式开发板。

答案:√

四、专业术语解释

1.DSP

答案:数字信号处理器

- HAL

答案:硬件抽象层

3.CPSR

答案:程序状态寄存器

- AHB

答案:先进高性能总线

- RTC

答案:实时时钟

6.DRAM

答案:动态随机存取存储器(不得分)

7.CAN

答案:控制器局域网

8.UART

答案:通用异步接收器和发送器

9.GPIO

答案:通用输入输出口

五、综合应用

答案:(1) CMP R0,R1 (2)SUBLT R1,R1, R0

(3)SUBGT R0, R0, R1(4) BNE START

2.

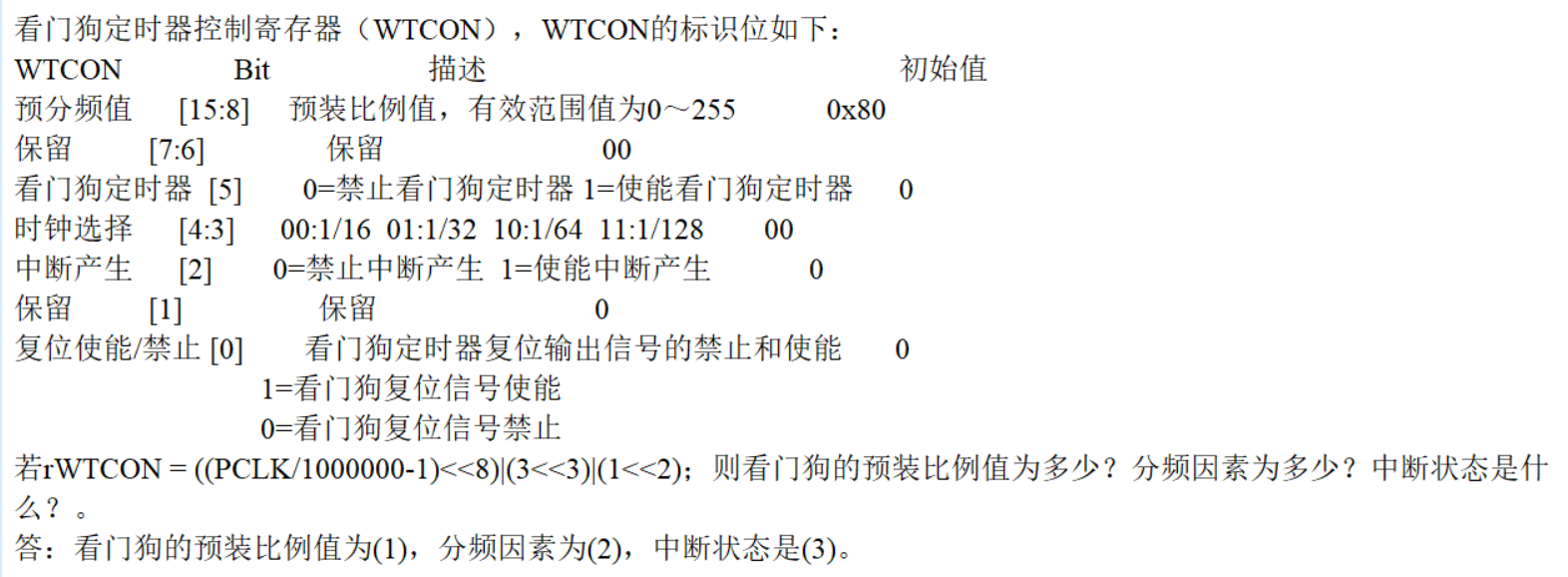

答案:(1)1000000 (2)1/128 (3)使能

3.

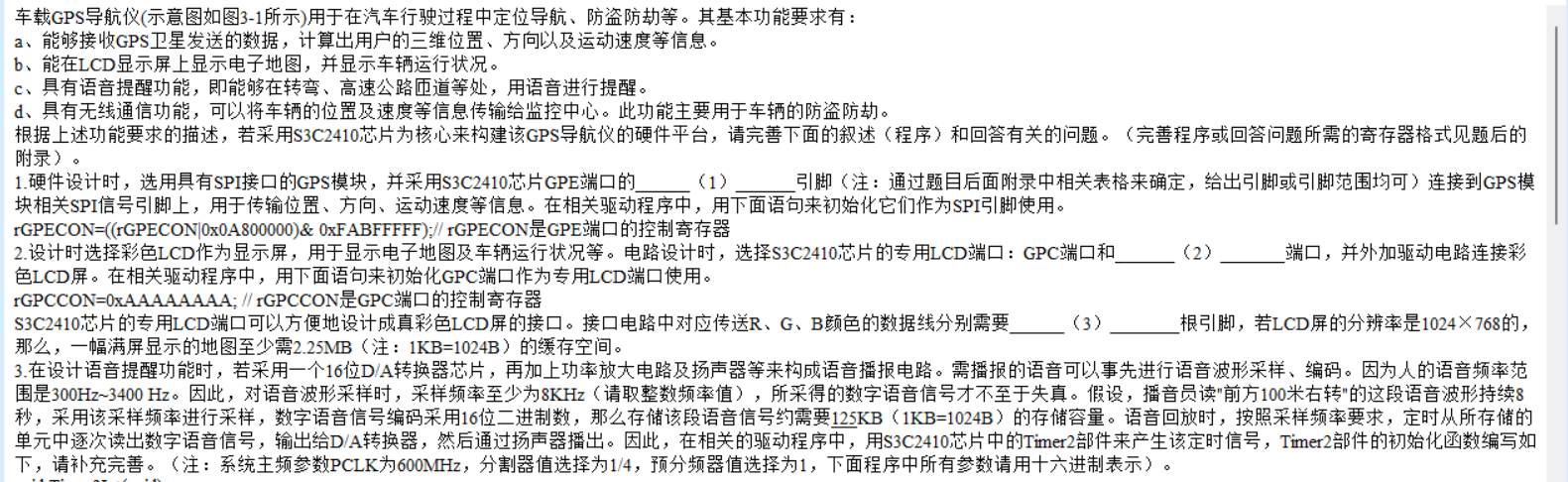

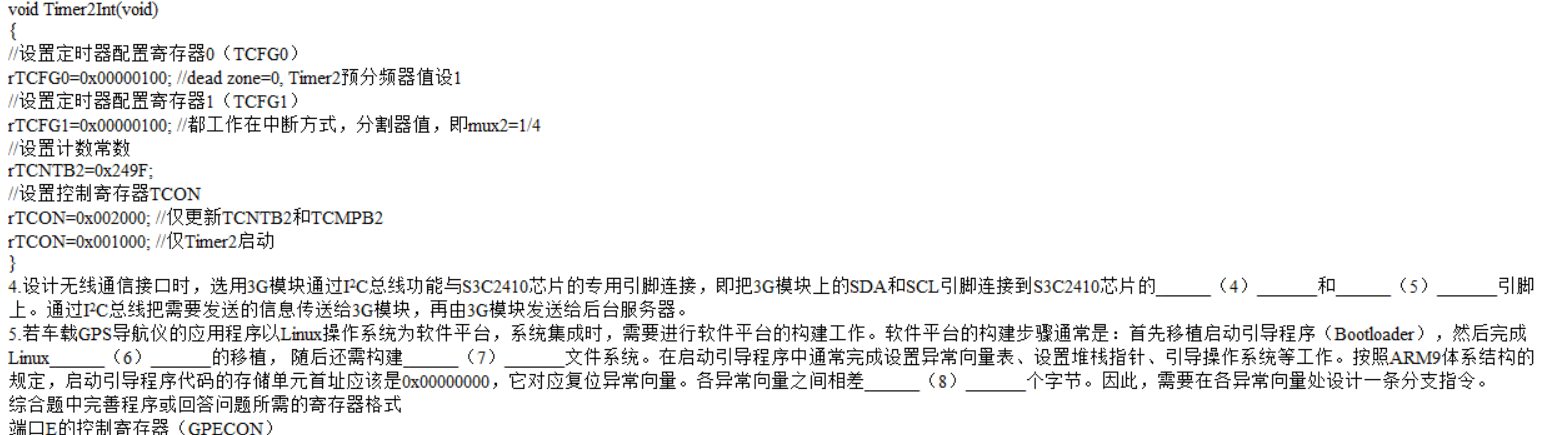

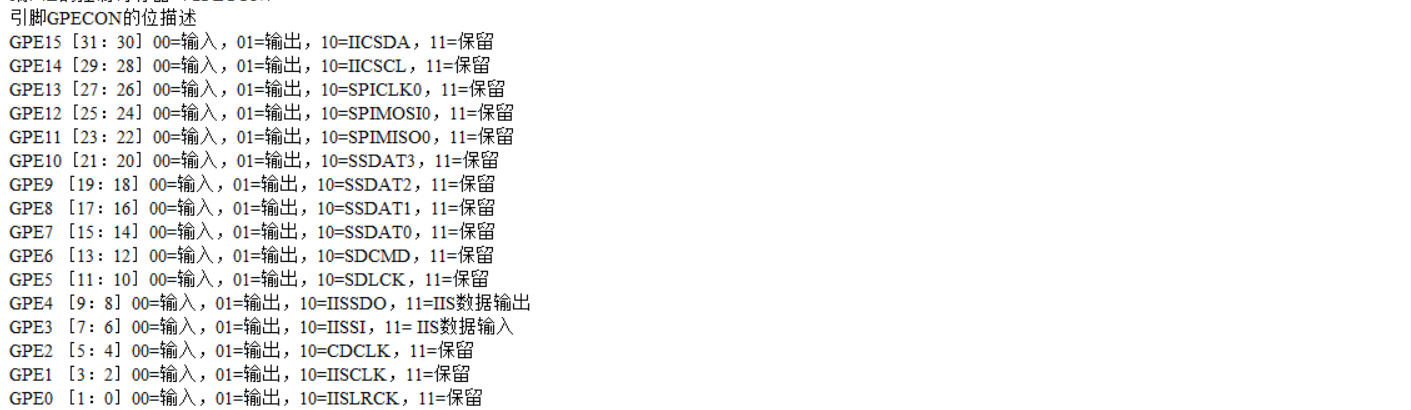

答案 :(1)GPE11 、GPE12、GPE13 ,(2)GPD ,(3) 8 ,(4)GPE15 ,(5) GPE14,(6)内核,(7)根,(8)4

📝大佬觉得本文有所裨益,不妨轻点一下👍给予鼓励吧!

❤️❤️❤️本人虽努力,但能力尚浅,若有不足之处,恳请各位大佬不吝赐教,您的批评指正将是我进步的动力!😊😊😊

💖💖💖若您认为此篇文章对您有所帮助,烦请点赞👍并收藏🌟,您的支持是我前行的最大动力!

🚀🚀🚀任务在默默中完成,价值在悄然间提升。让我们携手共进,一起加油,迎接更美好的未来!🌈🌈🌈