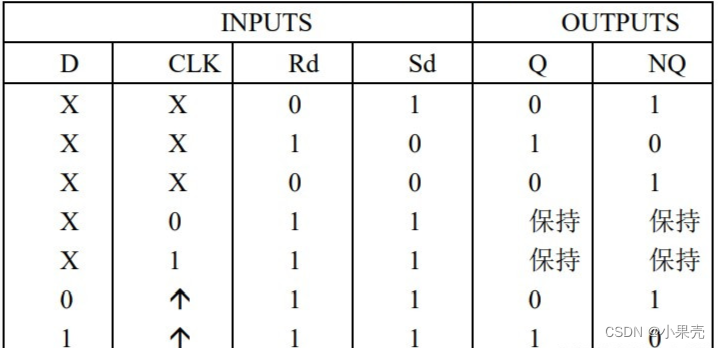

1 带有异步置位和异步清零的D触发器的真值表:

2 Verilog代码描述

module DFF_SR(CLK, D, Rd, Sd, Q, QN);

input CLK, D, Rd, Sd;

output Q, QN;

reg Q_DFF;

always @(posedge CLK

or negedge Rd or negedge Sd)begin

if(!Rd)

Q_DFF <= 1'b0;

else if(!Sd)

Q_DFF <= 1'b1;

else

Q_DFF <= D;

end

assign Q = Q_DFF;

assign QN = ~Q_DFF;

endmodule已经经本人验证,放心使用