文章目录

- [0. 时钟树结构](#0. 时钟树结构)

-

- [0.1 参考手册 Chapter 18: Clock Controller Module (CCM)](#0.1 参考手册 Chapter 18: Clock Controller Module (CCM))

- [0.2 时钟信号路径](#0.2 时钟信号路径)

- [1. 时钟源------晶振](#1. 时钟源——晶振)

-

- [1.1 外部低频时钟 - CKIL](#1.1 外部低频时钟 - CKIL)

-

- [1.1.1 CKIL 同步到 IPG_CLK 解释](#1.1.1 CKIL 同步到 IPG_CLK 解释)

- [1.2 外部高频时钟 - CKIH 和 内部振荡器](#1.2 外部高频时钟 - CKIH 和 内部振荡器)

- [1.3 总结](#1.3 总结)

- [1.4 缩写补充](#1.4 缩写补充)

- [2. PLL时钟](#2. PLL时钟)

-

- [2.1 i.MX6U 芯片 PLL 时钟表格](#2.1 i.MX6U 芯片 PLL 时钟表格)

- [2.2 i.MX6U 芯片 PLL 时钟详解](#2.2 i.MX6U 芯片 PLL 时钟详解)

- [3. PFD是什么](#3. PFD是什么)

-

- [3.1 PFD概述](#3.1 PFD概述)

- [3.2 PFD寄存器配置](#3.2 PFD寄存器配置)

- [4. AHB是什么](#4. AHB是什么)

- [5. IPG是什么](#5. IPG是什么)

本文章结合了正点原子的 i.mx6u嵌入式Linux开发指南 和笔者的理解。

本文章应配合《 【嵌入式Linux】i.MX6ULL 时钟树------代码梳理(基础时钟初始化)》使用。

0. 时钟树结构

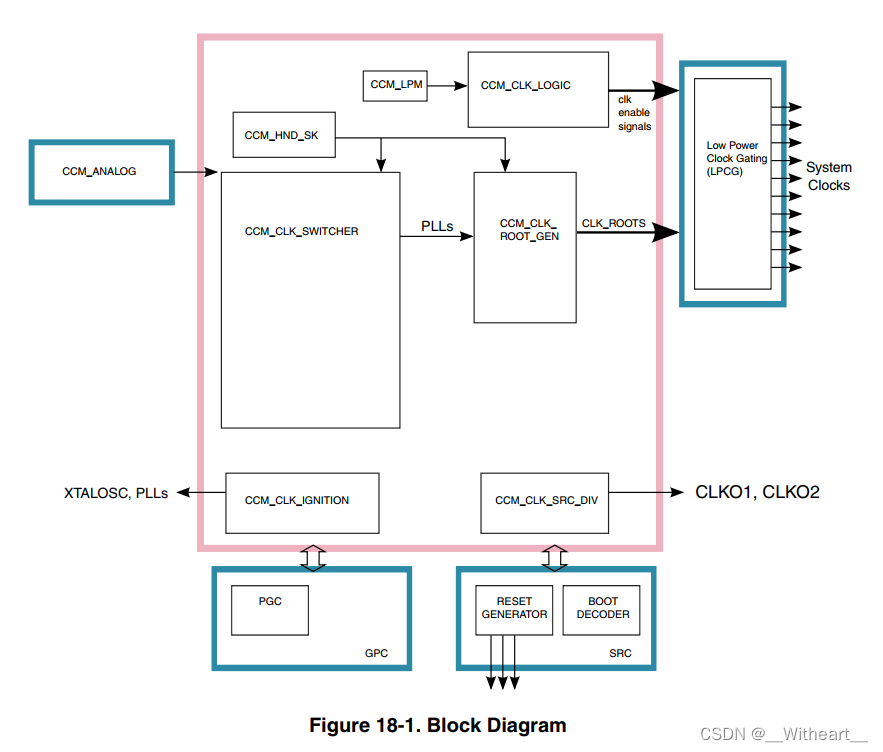

0.1 参考手册 Chapter 18: Clock Controller Module (CCM)

CCM(Clock Controller Module),意为时钟控制器模块。

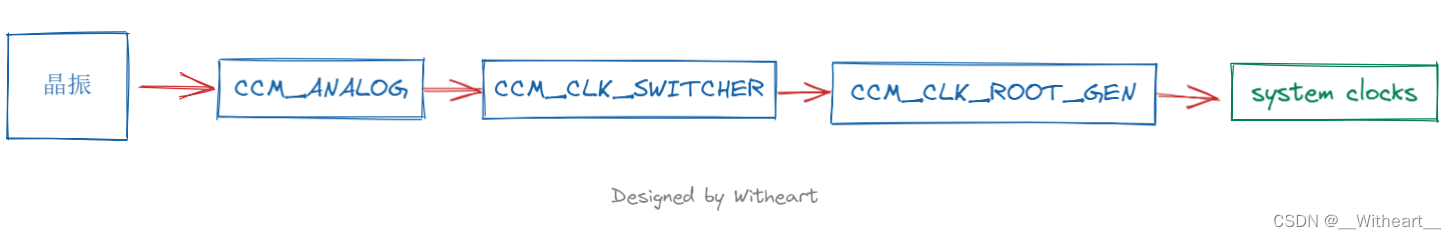

0.2 时钟信号路径

手册中的CMM框图:

晶振:32.768KHz外部的低速晶振、24MHz的外部高速晶振CCM_ANALOG:晶振信号为 analog(模拟) 信号,输入到芯片内部的 PLL(锁相环) 进行倍频,i.MX6ULL 内部有 7 个 PLL,在手册的 CCM_ANALOG 说明了配置方式和寄存器CCM_CLK_SWITCHER:接受 PLL 输出的时钟输出,以及PLLs的旁路时钟,并为CCM_CLK_ROOT_GEN子模块生成交换器时钟输出(pll1_sw_clk, pll3_sw_clk)CCM_CLK_ROOT_GEN:接收主时钟(PLLs / PFDs)并生成输出根时钟

______下面开始对各个部分进行详细的解释______

1. 时钟源------晶振

1.1 外部低频时钟 - CKIL

- 芯片可以使用 32kHz 或 32.768kHz 晶振作为外部低频源 (XTALOSC)。

- 本章将低频晶振统一称为 32kHz 晶振。

- 该时钟源在芯片上电后应始终处于活动状态。

- 进入 CCM 的 32kHz 信号被称为 CKIL。

- CKIL 同步到 IPG_CLK,并提供给需要它的模块。

1.1.1 CKIL 同步到 IPG_CLK 解释

- 当系统处于功能模式时,CKIL 同步到 IPG_CLK。

- 当系统处于停止模式(没有 IPG_CLK)时,CKIL 同步器被绕过,原始的 CKIL 被提供给系统。

- 也就是说系统正常工作,没有进入停止模式的时候,外部低频时钟 CKIL 会同步到 IPG_CLK;但是当进入停止模式的时候,同步器就不会生效,系统将外部低频晶振的信号。

1.2 外部高频时钟 - CKIH 和 内部振荡器

- 芯片使用内部振荡器产生参考时钟 (OSC)。

- 内部振荡器连接到外部晶体 (XTALOSC),产生 24MHz 参考时钟。

1.3 总结

- i.MX6ULL 芯片使用外部低频晶体 (32kHz) 作为 CKIL,并同步到 IPG_CLK。

- 芯片使用内部振荡器连接到外部高频晶体 (24MHz) 产生参考时钟。

1.4 缩写补充

- CCM 是 Clock Control Module (时钟控制模块),负责管理芯片内部的时钟信号。

- CKIL 代表 Clock Input Low,即低频时钟输入。

- IPG_CLK 是 Integrated Peripheral Clock (集成外设时钟),是芯片内部外设使用的时钟信号。

2. PLL时钟

P644

2.1 i.MX6U 芯片 PLL 时钟表格

| PLL 名称 | 序号 | 倍频 | 输出频率 | 用途 | 特点 |

|---|---|---|---|---|---|

| ARM_PLL | PLL1 | 可编程 (最高 1.3GHz) | 可编程 | ARM 内核 | ARM 内核运行速度取决于此 PLL 输出频率 |

| 528_PLL | PLL2 | 固定 22 倍频 | 528MHz | 系统总线、内部逻辑单元、DDR 接口、NAND/NOR 接口 | 核心时钟源 |

| USB1_PLL | PLL3 | 固定 20 倍频 | 480MHz | USB1PHY | 可用于多种外设 |

| USB2_PLL | PLL7 | 固定 20 倍频 | 480MHz | USB2PHY | 序号标为 4,实际是 PLL7 |

| ENET_PLL | PLL6 | 固定 20+5/6 倍频 | 500MHz | 网络 | 可生成 25/50/100/125MHz 网络时钟 |

| VIDEO_PLL | PLL5 | 可调整 (650MHz~1300MHz) | 可调整 | 显示相关外设 (LCD) | 可调整输出频率和分频比 |

| AUDIO_PLL | PLL4 | 可调整 (650MHz~1300MHz) | 可调整 | 音频相关外设 | 可调整输出频率和分频比 |

2.2 i.MX6U 芯片 PLL 时钟详解

i.MX6U 芯片拥有多个 PLL(Phase-Locked Loop,锁相环)模块,用于生成各种频率的时钟信号,为芯片内部的不同模块和外设提供时钟源。下面整理了 i.MX6U 芯片的 7 个主要 PLL:

1. ARM_PLL (PLL1)

- 用途: 为 ARM 内核提供时钟信号。

- 倍频: 可编程,最高可倍频至 1.3GHz。

- 特点: ARM 内核的运行速度直接取决于此 PLL 的输出频率。

2. 528_PLL (PLL2)

- 用途: 为系统总线、内部逻辑单元、DDR 接口、NAND/NOR 接口等提供时钟源。

- 倍频: 固定 22 倍频,不可编程。

- 输出频率: 24MHz * 22 = 528MHz。

- 特点: 该 PLL 以及其生成的 4 路 PFD (PLL2_PFD0~PLL2_PFD3) 是 i.MX6U 内部系统总线的核心时钟源。

3. USB1_PLL (PLL3)

- 用途: 主要用于 USB1PHY,但也可作为其他外设的时钟源。

- 倍频: 固定 20 倍频。

- 输出频率: 24MHz * 20 = 480MHz。

- 特点: 该 PLL 以及其生成的 4 路 PFD (PLL3_PFD0~PLL3_PFD3) 可用于多种外设。

4. USB2_PLL (PLL7)

- 用途: 为 USB2PHY 提供时钟信号。

- 倍频: 固定 20 倍频。

- 输出频率: 24MHz * 20 = 480MHz。

- 特点: 虽然序号标为 4,但实际是 PLL7。

5. ENET_PLL (PLL6)

- 用途: 用于生成网络所需的时钟信号。

- 倍频: 固定 20+5/6 倍频。

- 输出频率: 24MHz * (20+5/6) = 500MHz。

- 特点: 可在此 PLL 的基础上生成 25/50/100/125MHz 的网络时钟。

6. VIDEO_PLL (PLL5)

- 用途: 用于显示相关外设,例如 LCD。

- 倍频: 可调整,输出范围在 650MHz~1300MHz。

- 分频: 可选 1/2/4/8/16 分频。

- 特点: 可根据显示设备的需求调整输出频率和分频比。

7. AUDIO_PLL (PLL4)

- 用途: 用于音频相关外设。

- 倍频: 可调整,输出范围在 650MHz~1300MHz。

- 分频: 可选 1/2/4 分频。

- 特点: 可根据音频设备的需求调整输出频率和分频比。

总结:

i.MX6U 芯片通过多个 PLL 模块,生成各种频率的时钟信号,为芯片内部的不同模块和外设提供时钟源。每个 PLL 的倍频和分频都可以根据需要进行配置,以满足不同外设的需求。

3. PFD是什么

3.1 PFD概述

P646

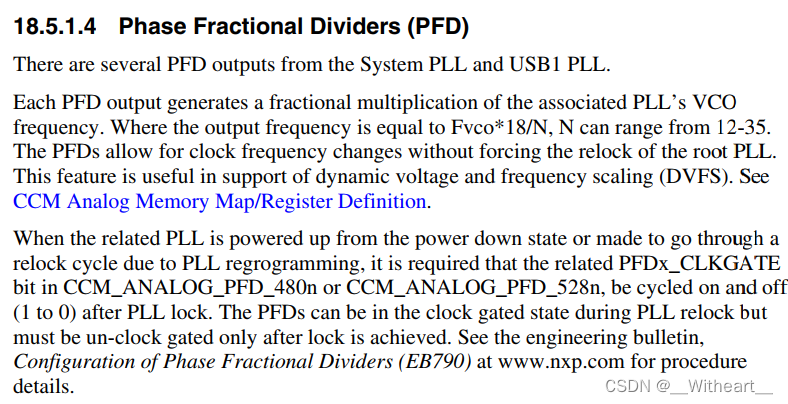

相位分数分频器 (Phase Fractional Divider, PFD) 在 NXP 处理器中的应用,与 锁相环 (PLL) 的关系:

PFD 是 PLL 中的一个重要组成部分,它可以将 PLL 的输出频率进行分数分频,从而产生更精确的时钟频率。

- PFD 的输出频率: PFD 的输出频率是 PLL 的 VCO 频率的倍数,但可以是分数倍数。例如,输出频率可以是 Fvco * 18/N,其中 N 的取值范围为 12-35。

- PFD 的作用: PFD 可以动态调整时钟频率,而无需重新锁定 PLL。这对于支持动态电压和频率缩放 (DVFS) 非常有用,因为 DVFS 可以根据负载情况动态调整 CPU 的频率和电压,从而降低功耗。

- PFD 的控制: PFD 的时钟门控可以通过 CCM_ANALOG_PFD_480n 或 CCM_ANALOG_PFD_528n 寄存器中的 PFDx_CLKGATE 位进行控制。在 PLL 上电或重新锁定后,需要将 PFDx_CLKGATE 位循环开、关 (1 到 0) 以确保 PFD 正确工作。

- PFD 的配置: 更多关于 PFD 配置的细节可以在 NXP 网站的工程公告 EB790 中找到。

总之,PFD 是 PLL 中的重要组成部分,它可以实现分数分频,从而产生更精确的时钟频率,并支持 DVFS 功能。PFD 的控制和配置需要按照 NXP 的规范进行操作。

3.2 PFD寄存器配置

P738

- 以PLL2(systemPLL)的4个PFD为例

- 4个PFD由一个32位寄存器配置:528MHz Clock (PLL2) Phase Fractional Divider Control Register (CCM_ANALOG_PFD_528n)

寄存器结构:

- 每个字段对应寄存器中的特定位。

- 字段名称以

PFD开头,代表 Phase Frequency Divider ,即 相位频率分频器。 - 数字

0到3代表不同的分频器。 - 后缀

_FRAC代表 Fractional Divide Value ,即 分数分频值。 - 后缀

_CLKGATE代表 Clock Gate ,即 时钟门控。 - 后缀

_STABLE代表 Stable ,即 稳定。

字段描述:

| 字段 | 位 | 描述 | 备注 |

|---|---|---|---|

| PFD3_CLKGATE | 31 | IO 时钟门控。如果设置为 1,则第三个分数分频器时钟 (参考 ref_pfd3) 关闭 (省电)。0: ref_pfd3 分数分频器时钟开启。 | 需要在 PLL 关闭之前断言此位。 |

| PFD3_STABLE | 30 | 只读位,用于诊断目的。分数分频器应该足够快地稳定,因此此字段永远不需要由设备驱动程序或应用程序代码使用。 | 当新的分数分频值生效时,该值会反转。读取此位,编程新值,当此位反转时,相位分频器时钟输出稳定。注意,当分数分频器处于或进入时钟门控状态时,该值不会反转。 |

| PFD3_FRAC | 29-24 | 控制分数分频值。结果频率应为 528*18/PFD3_FRAC,其中 PFD3_FRAC 的范围为 12-35。 | |

| PFD2_CLKGATE | 23 | IO 时钟门控。如果设置为 1,则 IO 分数分频器时钟 (参考 ref_pfd2) 关闭 (省电)。0: ref_pfd2 分数分频器时钟开启。 | 需要在 PLL 关闭之前断言此位。 |

| PFD2_STABLE | 22 | 只读位,用于诊断目的。分数分频器应该足够快地稳定,因此此字段永远不需要由设备驱动程序或应用程序代码使用。 | 当新的分数分频值生效时,该值会反转。读取此位,编程新值,当此位反转时,相位分频器时钟输出稳定。注意,当分数分频器处于或进入时钟门控状态时,该值不会反转。 |

| PFD2_FRAC | 21-16 | 控制分数分频值。结果频率应为 528*18/PFD2_FRAC,其中 PFD2_FRAC 的范围为 12-35。 | 最大允许频率为 400MHz。 |

| PFD1_CLKGATE | 15 | IO 时钟门控。如果设置为 1,则 IO 分数分频器时钟 (参考 ref_pfd1) 关闭 (省电)。0: ref_pfd1 分数分频器时钟开启。 | 需要在 PLL 关闭之前断言此位。 |

| PFD1_STABLE | 14 | 只读位,用于诊断目的。分数分频器应该足够快地稳定,因此此字段永远不需要由设备驱动程序或应用程序代码使用。 | 当新的分数分频值生效时,该值会反转。读取此位,编程新值,当此位反转时,相位分频器时钟输出稳定。注意,当分数分频器处于或进入时钟门控状态时,该值不会反转。 |

| PFD1_FRAC | 13-8 | 控制分数分频值。结果频率应为 528*18/PFD1_FRAC,其中 PFD1_FRAC 的范围为 12-35。 | |

| PFD0_CLKGATE | 7 | 如果设置为 1,则 IO 分数分频器时钟 (参考 ref_pfd0) 关闭 (省电)。0: ref_pfd0 分数分频器时钟开启。 | 需要在 PLL 关闭之前断言此位。 |

| PFD0_STABLE | 6 | 只读位,用于诊断目的。分数分频器应该足够快地稳定,因此此字段永远不需要由设备驱动程序或应用程序代码使用。 | 当新的分数分频值生效时,该值会反转。读取此位,编程新值,当此位反转时,相位分频器时钟输出稳定。注意,当分数分频器处于或进入时钟门控状态时,该值不会反转。 |

| PFD0_FRAC | 5-0 | 控制分数分频值。结果频率应为 528*18/PFD0_FRAC,其中 PFD0_FRAC 的范围为 12-35。 | 对于 76 MHz 的 QSPI 引导,此 PFD 会重新锁定到 307 MHz,因此此字段的默认值 (由 ROM 修改) 将为 0x1f。同样,对于低频引导,ROM 会将此 PFD 重新锁定到 307 MHz,因此默认值为 0x1f。 |

总结:

CCM_ANALOG_PFD_528n 寄存器控制着 i.MX 6ULL 处理器中四个分数分频器的配置,包括时钟门控、稳定性状态和分数分频值。这些分频器用于生成不同频率的时钟信号,以满足各种外设的需求。

1. CLKGATE 位 (Clock Gate): 时钟门控

- 作用:

CLKGATE位控制着对应PFD的时钟信号是否被开启或关闭。 - 值:

0: 时钟信号开启,PFD正常工作,可以输出分频后的时钟信号。1: 时钟信号关闭,PFD处于关闭状态,不输出时钟信号。

- 目的:

- 省电: 当某个外设不需要时钟信号时,可以通过设置

CLKGATE位为1来关闭该PFD的时钟,从而减少功耗。 - 控制时钟信号: 在某些情况下,可能需要动态地控制某个外设的时钟信号,例如在系统启动或进入低功耗模式时。

- 省电: 当某个外设不需要时钟信号时,可以通过设置

2. STABLE 位 (Stable): 稳定性状态

- 作用:

STABLE位指示对应PFD的输出时钟信号是否已经稳定。 - 值:

当新的分数分频值生效时,位域的值会反转(从 0 变为 1 或从 1 变为 0)。这个反转就像一个信号,表明分频器已经完成调整。 - 目的:

- 诊断:

STABLE位是一个只读位,用于诊断PFD的稳定性。 - 确保时钟信号质量: 在修改

PFD的分数分频值后,需要等待STABLE位反转,才能确保输出的时钟信号稳定可靠。

- 诊断:

4. AHB是什么

AHB 是 Advanced High-performance Bus 的缩写,中文意思是 高级高性能总线。它是一种同步总线协议,广泛应用于嵌入式系统和微处理器中,用于连接 CPU、内存控制器、外设等重要模块。

AHB 总线的主要特点:

- 高性能: AHB 总线采用同步传输方式,并支持突发传输,可以实现高速的数据传输。

- 灵活的地址空间: AHB 总线支持 32 位地址空间,可以连接大量的模块。

- 多主控支持: AHB 总线可以支持多个主控设备,例如 CPU、DMA 控制器等。

- 错误检测机制: AHB 总线包含错误检测机制,可以检测数据传输过程中的错误。

- 支持多种传输模式: AHB 总线支持多种传输模式,例如单字节传输、字传输、突发传输等。

- 支持多种数据宽度: AHB 总线支持 8 位、16 位、32 位等多种数据宽度。

AHB 总线的工作原理:

AHB 总线采用同步传输方式,即所有模块都使用同一个时钟信号。主控设备通过总线发送地址和控制信号,从设备根据地址和控制信号进行数据传输。

AHB 总线的应用:

AHB 总线广泛应用于各种嵌入式系统和微处理器中,例如:

- ARM 处理器: ARM 处理器通常使用 AHB 总线连接 CPU、内存控制器、外设等模块。

- FPGA: FPGA 中也经常使用 AHB 总线连接不同的模块。

- SoC: SoC 中也经常使用 AHB 总线连接不同的模块。

5. IPG是什么

IPG是 Intergrated Peripheral Clock 的缩写。

IPG 是一个 集成外设时钟,它提供给 i.MX6ULL 芯片上的各种外设,例如:

- UART

- SPI

- I2C

- CAN

- GPIO

- ADC

- DAC

- 等等

G 在 IPG 中代表 Generator ,即 时钟发生器。IPG 时钟发生器是一个独立的模块,它可以产生各种频率的时钟信号,以满足不同外设的需求。

Peripheral Clock 是指 外设时钟,它是由 IPG 时钟发生器产生的,并分配给特定外设使用的时钟信号。每个外设都有自己的时钟频率,可以通过配置 IPG 时钟发生器来设置。

总结:

- IPG 是 Integrated Peripheral Clock 的缩写,代表集成外设时钟。

- G 代表 Generator,即时钟发生器。

- Peripheral Clock 是由 IPG 时钟发生器产生的,并分配给特定外设使用的时钟信号。