今天来讲一篇如何在fpga上实现sata ip,然后利用sata ip实现读写sata 盘的目的,如果需要再速度和容量上增加,那么仅仅需要增加sata ip个数就能够实现增加sata盘,如果仅仅实现data的读写整体来说sata ip设计比较简单,下面从sata 协议角度来聊聊sata ip应该如何实现。下图就是在FPGA上实现3张SATA SSD硬盘组成RAID0的结构图。

sata速度分为三个等级,sata在硬件接口上是一对收发差分信号,硬件是全双工模式,但实际SATA协议是半双工工作模式,为什么会如此奇怪,再link层会讲解到。sata gen1 速度1.5Gbps,sata gen2速度3.0 Gbps,sata gen3 速度6.0Gbps,然后编码都是8b/10b编码,所以对于sata gen3的有效带宽速度=6*1000 * 0.8 / 8= 600MB/s(注意这里的速度都是按照1000进制计算),这里的有效带宽包含了FIS数据和一些握手 Primitives,实际的纯data的有效带宽一般是在570MB/s,如果带了sata盘,那么就和每家的ssd盘有一定关联,目前速度做的最快和最稳定的当是三星大哥了。

链路层

物理层不需要我们设计,用xilinx的ip就行,我们从链路层开始讲解。

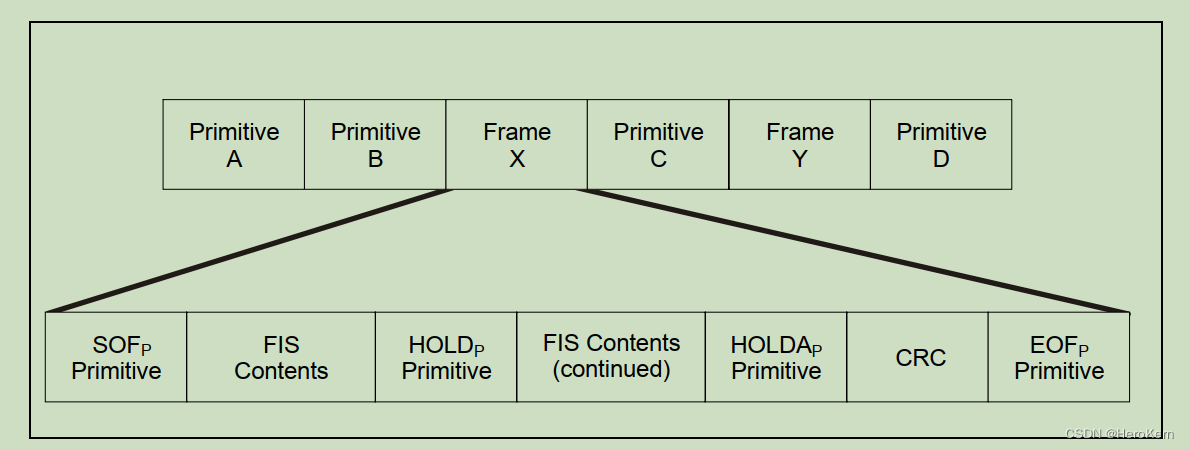

链路层的帧结构如下所示,Primitives + FIS +CRC组成,FIS在链路层看层是data,我们在传输层时候在讲解,CRC是FIS的CRC,Primitives用于HOST和device之间如何通讯,如何握手。每个FIS的传输都离不开Primitives和CRC.

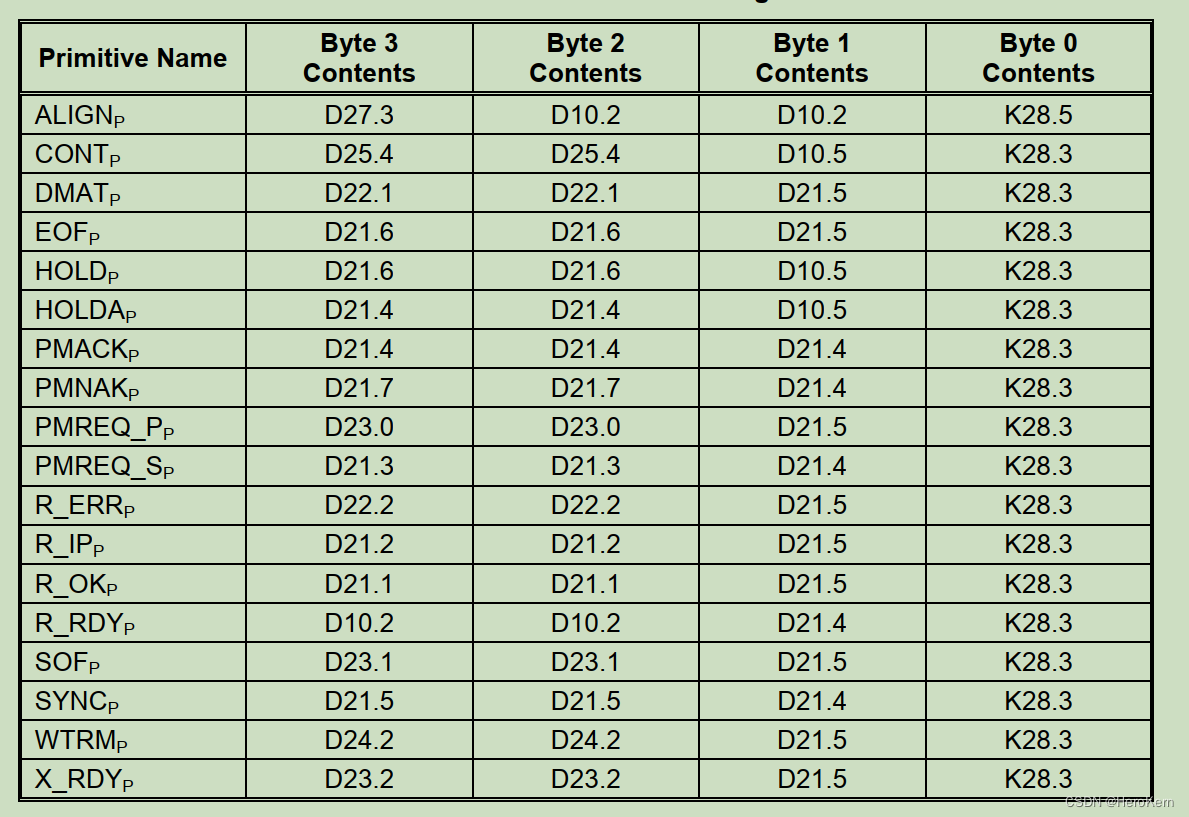

常见的Primitives如下图所示,这里只列举一些Primitives。

SOF :表示数据传输的start

EOF:表示数据传输的end

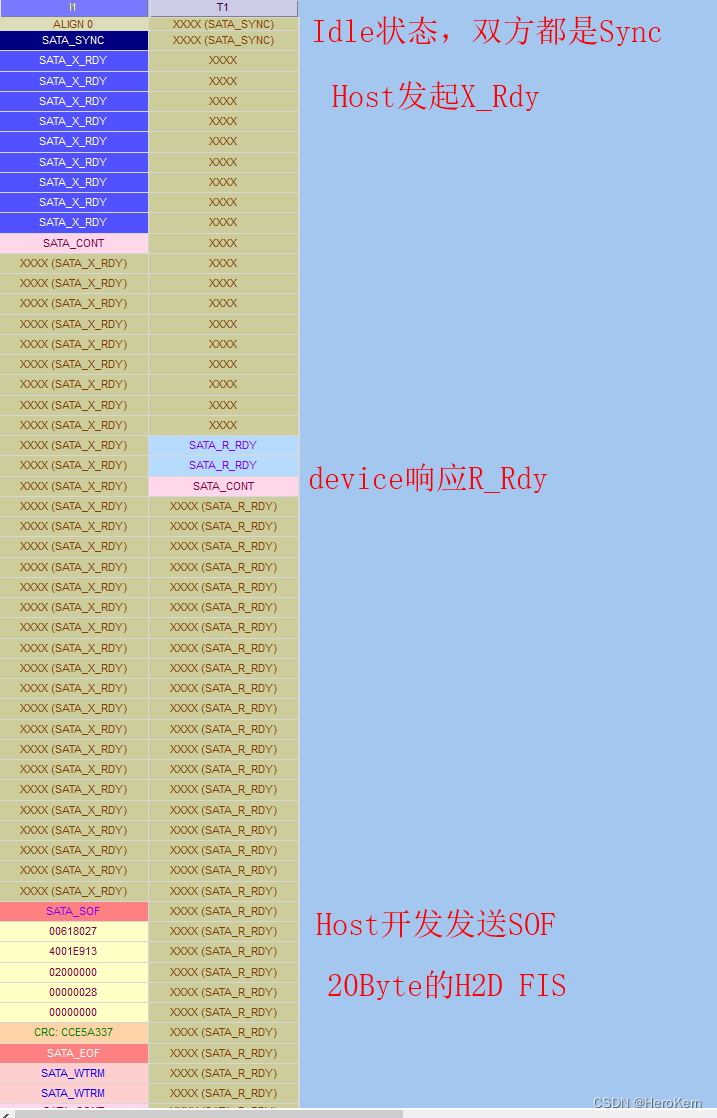

X_RDY:向对端发起请求,我要抢占总线传输数据

R_RDY:接受者向发起者发送该Primitives表示我已经准备好了

R_IP:表示一直在收数据或者在发数据,这就是为什么sata是半双工的原因,需要一直握手。

SYNC:表示事情做完了,可以让出总线处于Idle状态

传输层

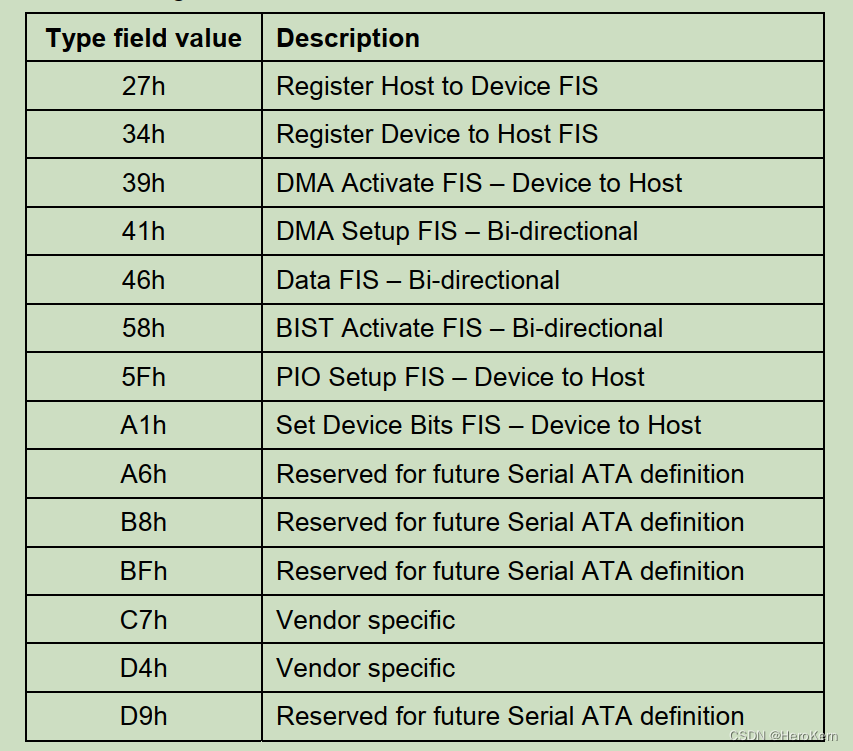

传输层设计相对简单很多,传输主要是解析FIS帧或者组FIS帧,常用的FIS帧如下所示。

从上图可以看到FIS层一共有8中类型的FIS,我们在设计FPGA SATA IP时可以不用设计BIST Activate FIS,因为该FIS用于验证链路的,下面列举几个常见FIS帧,

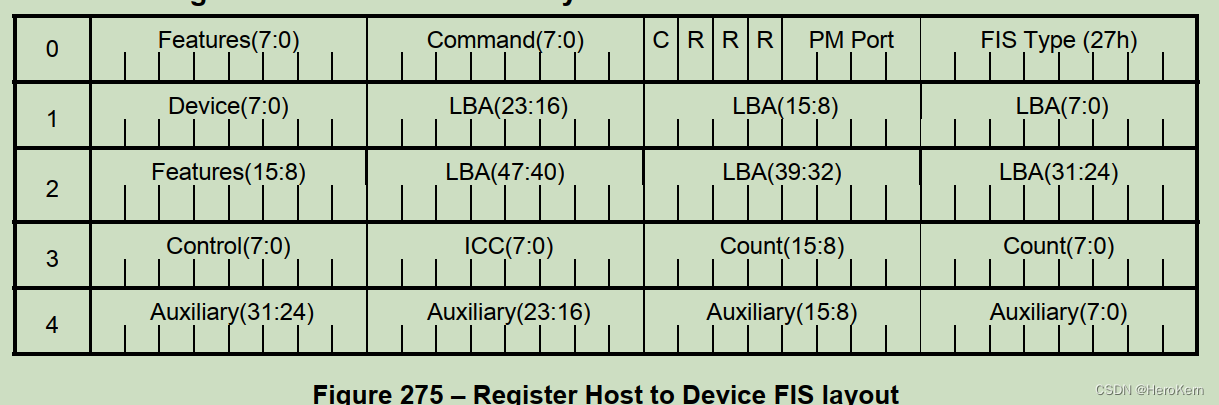

从下面FIS帧我们可以清晰的看到lba,count和Command等栏位,lba就是访问sata硬盘的逻辑扇区,count是lba的数量,count最大是16bit表示,那么可以看出单次命令最大的size=32MB,count=0表示32MB,command表示应用层的cmd code,这个在应用层会讲解。

D2H FIS帧格式如下:

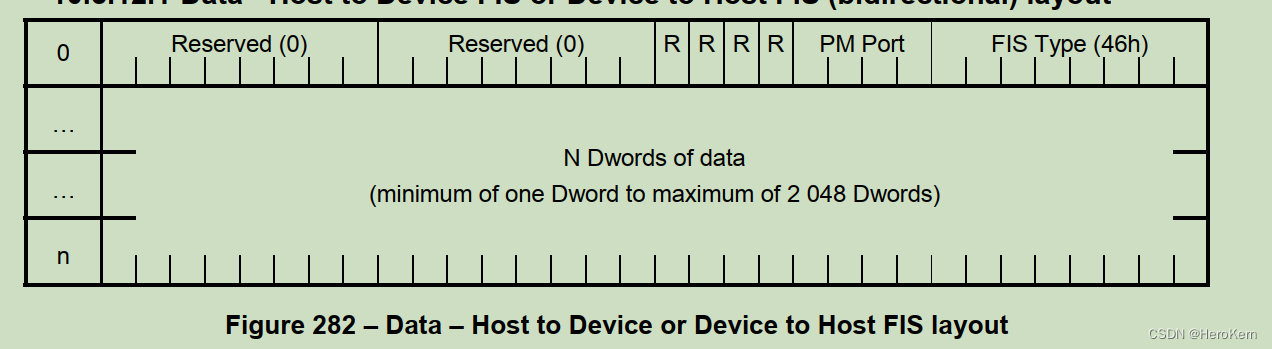

DATA FIS帧格式如下

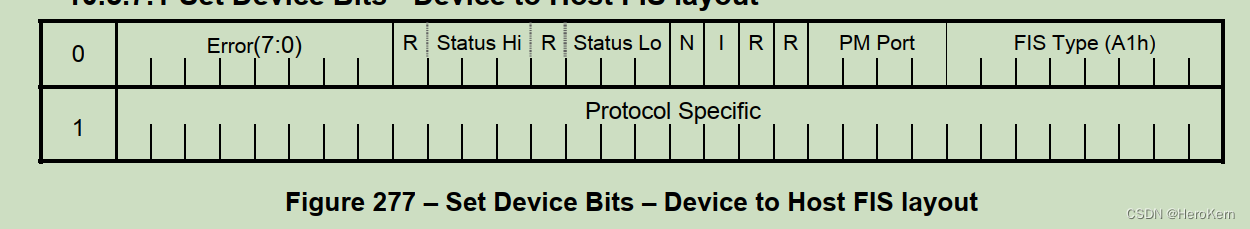

SDB FIS帧格式如下,NCQ发送DATA FIS之后需要发送SDB FIS反馈状态。

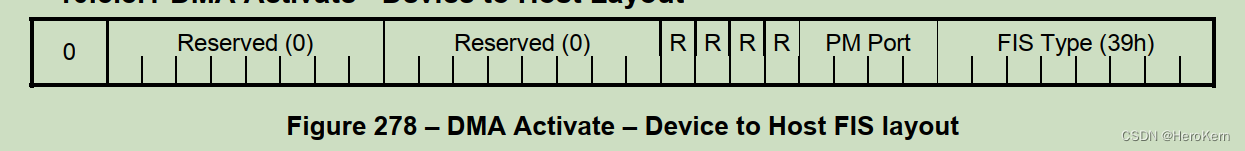

DMA Activate FIS帧格式如下,DMA Write和NCQ Write命令特有的。

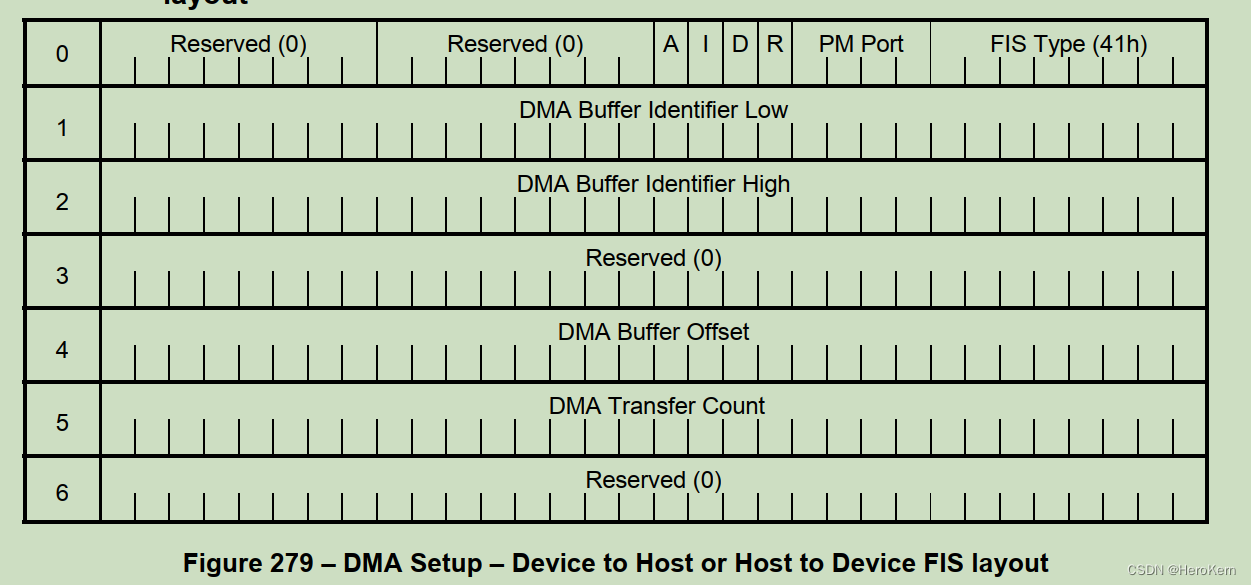

DMA Setup FIS帧格式如下,这个是NCQ命令特有的

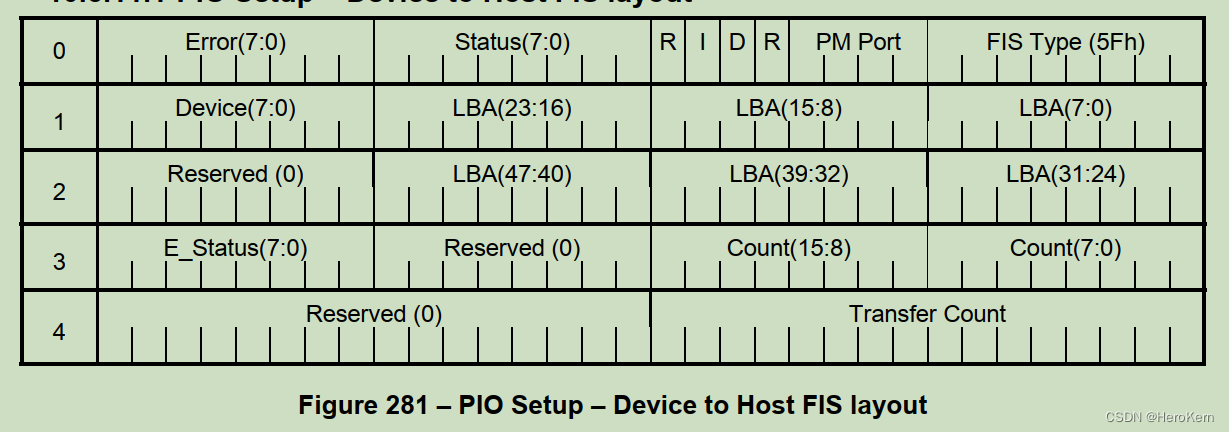

PIO Setup FIS帧格式如下,这个是PIO命令特有的。

应用层

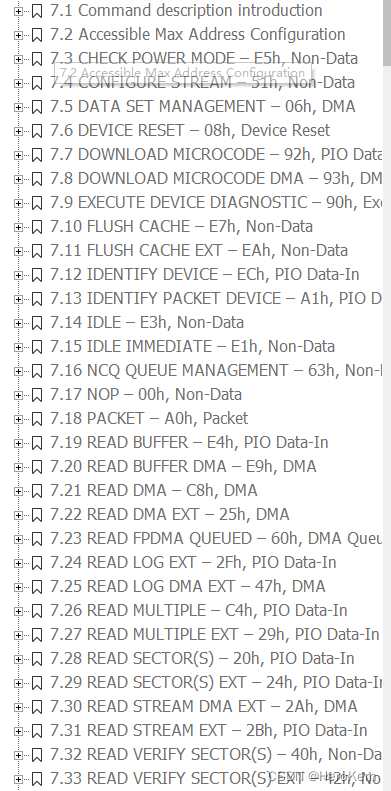

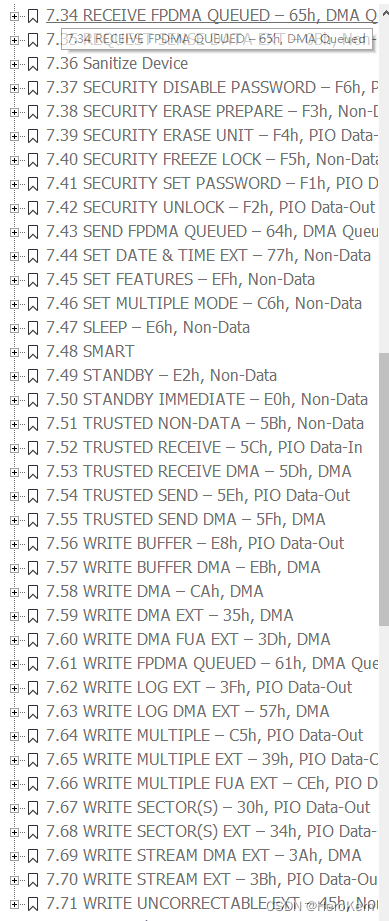

应用层常用的是ATA指令集,ATA指令集如下所示。

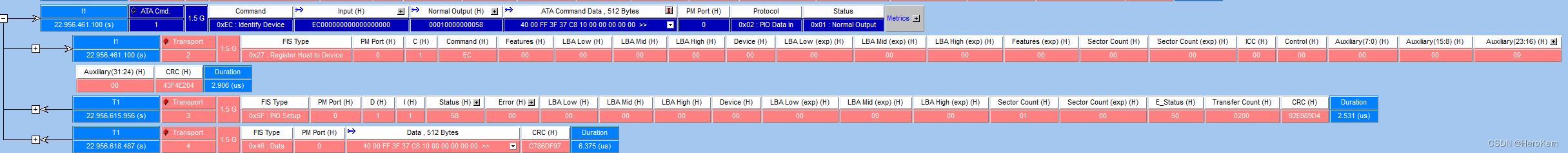

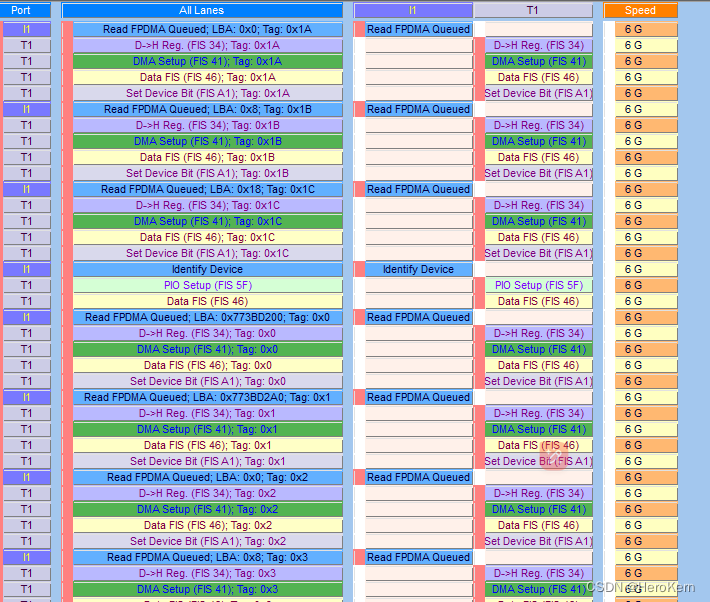

ATA指令集command偏多,这里讲解identify,trim,flush cache和ncq read write命令,下面贴图都是4KB size,和NCQ qd1,这样是为了方便理解单个命令FIS交互过程。flush cache命令比较简单,就是一个non-data命令,只需要H2D FIS和D2H FIS两个FIS就能完成命令的实现。

identify命令是一个pio read命令,只要不是Error情况,device是不需要响应D2H FIS

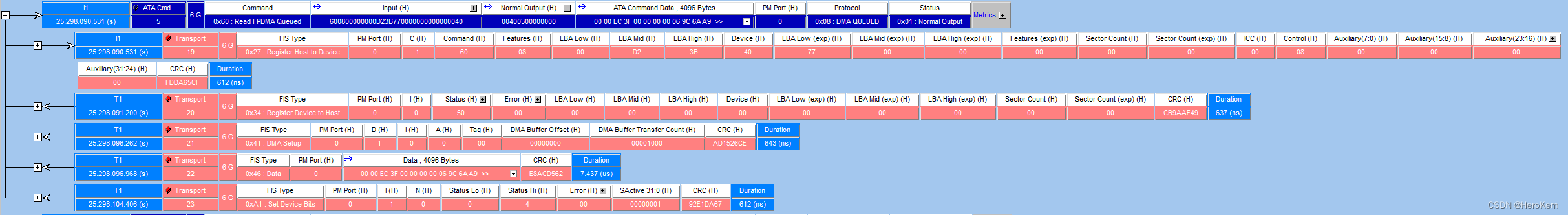

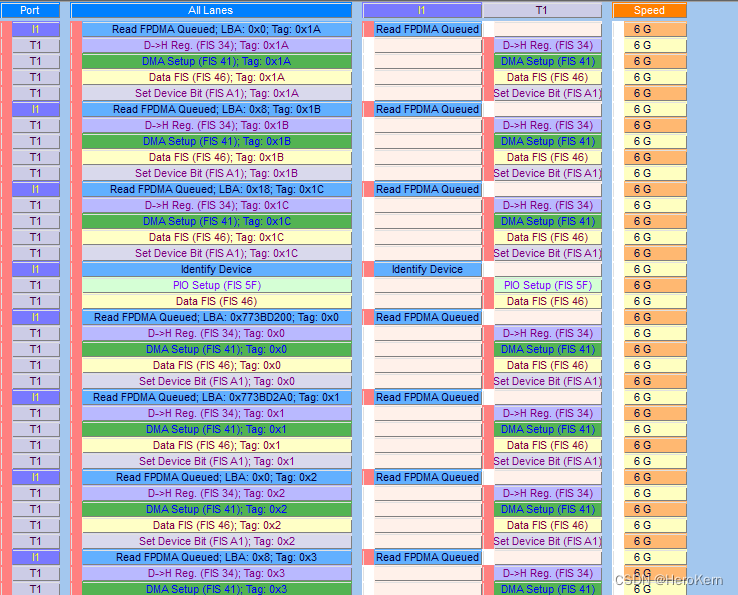

NCQ Read命令

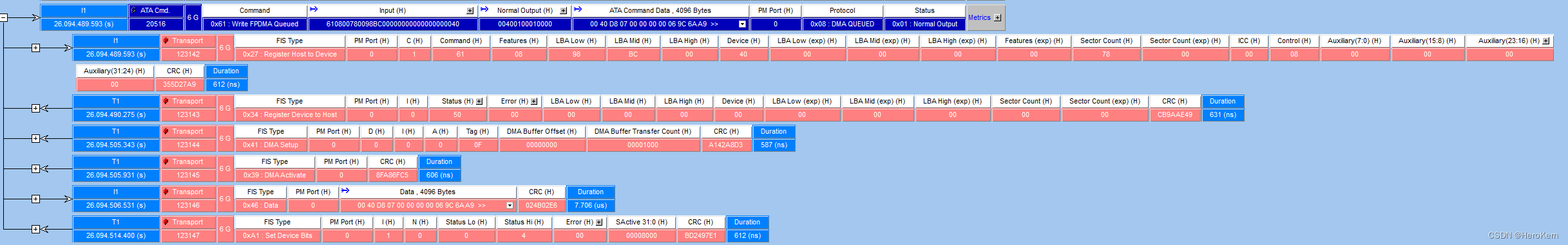

NCQ Wrtie命令,细心的同学发现了Write命令比Read命令多了一个DMA Activate,并且这个FIS在第一笔DATA FIS传输是可以省略的(可以在Set feature命令中设置)

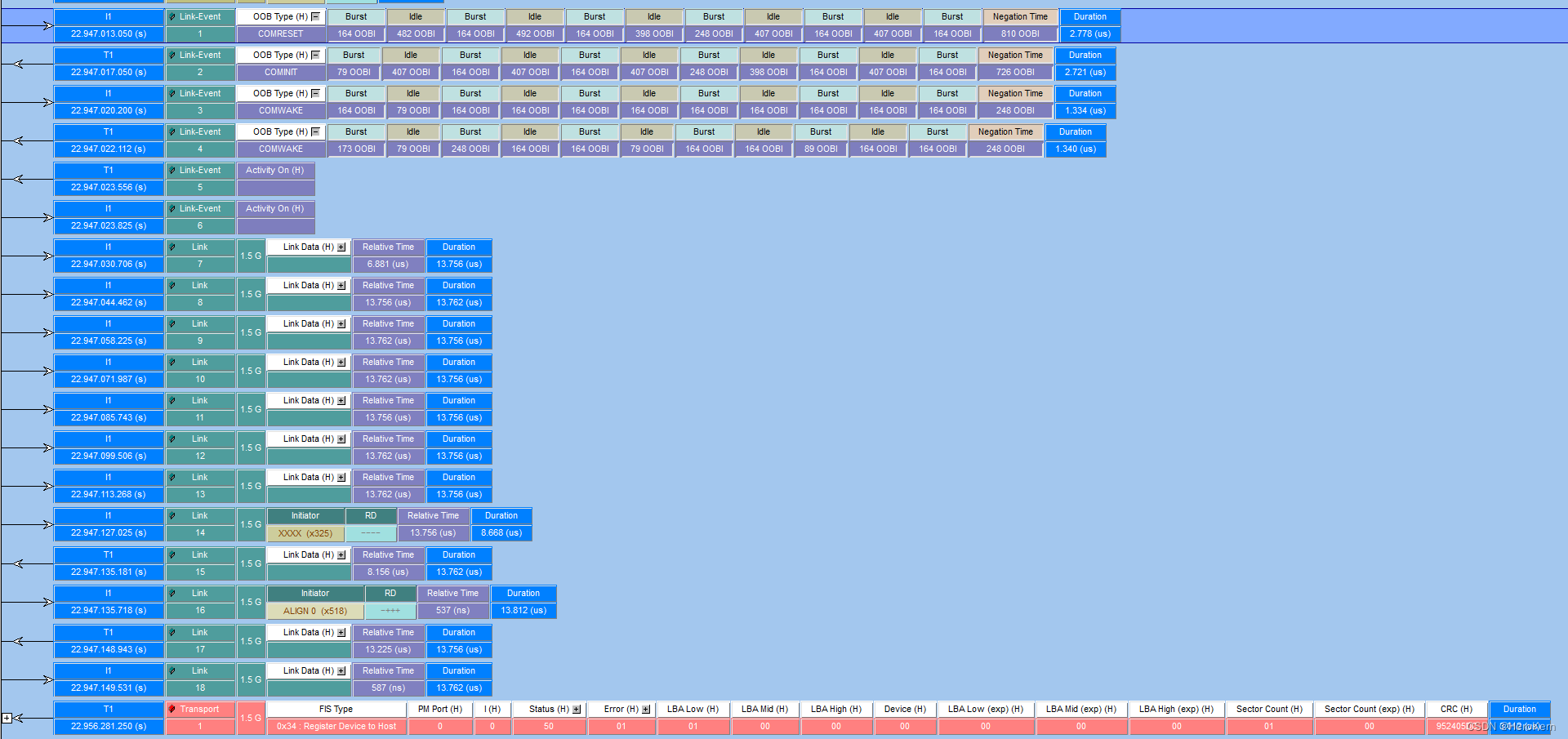

最后一个很重要的就是硬复位命令了,这个COMRESET在Primitives实现的。

总体来说SATA设计比较简单,因为不需要考虑什么low power等,仅仅需要实现NCQ命令就行,NCQ命令可以最大支持qd32,但是速度还是很慢,有条件就上pcie,无论在单lane速率,还是lane得数量上都是吊打sata,反正结合项目实际需求,找到适合自己的设计方案。