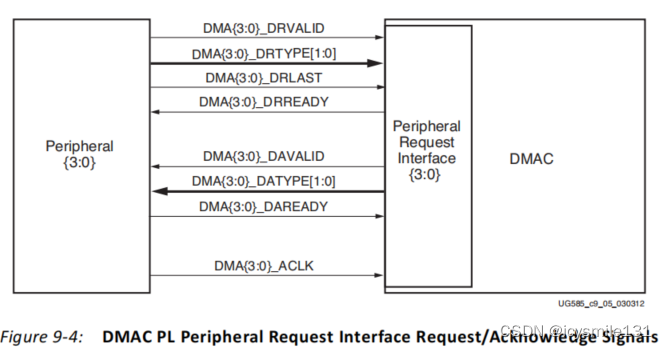

图9-4中展示了PL外设请求接口主要由两部分组成:PL外设请求总线和DMAC确认总线。这两部分分别使用特定的前缀进行标识,具体如下:

- PL外设请求总线(PL Peripheral Request Bus) :

- 前缀:DR

- 功能:用于PL外设向DMAC(直接内存访问控制器)发送请求信号。这些请求信号可能包括数据传输请求、中断请求或其他类型的请求。

- 特点:该总线允许多个PL外设同时向DMAC发送请求,并且每个请求都可以被DMAC单独处理。

- DMAC确认总线(DMAC Acknowledge Bus) :

- 前缀:DA

- 功能:用于DMAC向PL外设发送确认信号。这些确认信号表示DMAC已经接收到来自PL外设的请求,并正在处理或已经处理完成。

- 特点:该总线确保PL外设能够了解它们发出的请求是否已被DMAC接收和处理。通过DMAC的确认信号,PL外设可以采取适当的后续操作,如继续发送数据、进入等待状态或执行其他任务。

两种总线都使用AXI协议所描述的有效就绪握手。

- PL外围设备使用DMA{3:0}_DRTYPE[1:0]寄存器 :用于指定DMA传输的类型,

DMA{3:0}_DRTYPE[1:0]可以设置为不同的值来请求单一AXI事务(single AXI transaction)或AXI突发事务(AXI burst transaction),还可以用于确认一个刷新请求(flush request)。

- DMA{3:0}_DATYPE[1:0] 寄存器(在DMAC中) :用于向PL外设发送信号,指示DMAC何时完成了请求的单一AXI事务或AXI突发事务。

DMA{3:0}_DATYPE[1:0]的值将被DMAC设置,以通知PL外设DMA传输的状态。它还可以用于由DMAC发起刷新请求,这通常用于清空或重置DMA通道的状态。 - DMA{3:0}_DRLAST 信号(在PL外设中) :用于通知DMAC,当前AXI事务的最后一个数据周期已经开始。当PL外设发送完一个AXI事务的所有数据,并且这是该事务的最后一个数据周期时,它会设置

DMA{3:0}_DRLAST信号。这允许DMAC知道何时可以结束当前事务并释放相关资源。

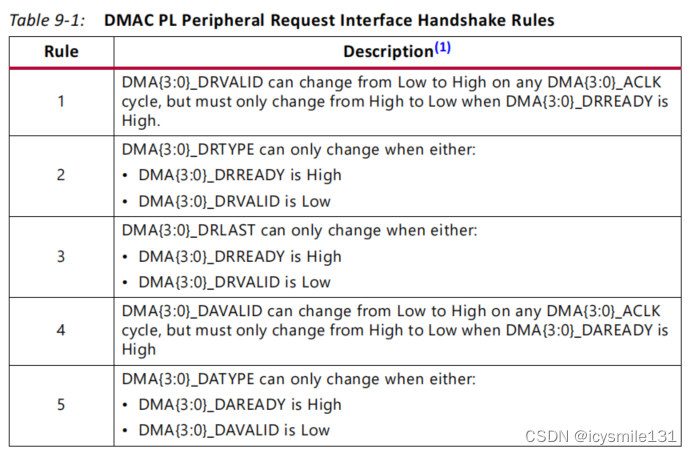

握手规则

当DMA通道线程处于活动状态,即不处于停止状态时,DMAC使用表9-1所示的DMA握手规则。

注:上表中所有信号都与DMA{3:0}_ACLK时钟同步

将PL外围接口映射到DMA通道

DMAC使软件能够将PL外围设备请求接口分配给任何DMA通道。当DMA通道线程执行DMAWFP时,PL外设[4:0]字段中编程的值指定与该DMA通道相关联的PL外设。

PL外设-长度由DMAC管理

DMAC长度管理是DMAC控制要传输的数据总量的过程。使用PL外围设备请求接口,当需要在任一方向上传输数据时,PL外围设备通知DMAC。DMA通道线程控制DMAC如何响应PL外围设备请求。

以下约束条件适用于DMAC长度管理:

- 单个请求与突发请求的数据量约束:

来自一个PL(Programmable Logic,可编程逻辑)外设的所有单个请求的数据总量必须小于该PL外设的突发请求的数据量。这意味着,如果你计划进行一系列的单次数据传输(single requests),它们的总数据量不能超过你为该外设配置的突发传输(burst request)的数据量。

- CCRn寄存器控制数据传输量:

CCRn(Channel Control Register n,通道控制寄存器n)用于控制突发请求和单个请求的数据传输量。这通常涉及到设置传输的数据块大小、是否启用中断等。

Arm(ARM架构的开发商)建议,在DMA通道的数据传输正在进行时,不要更新相应的CCRn寄存器。这是为了避免在数据传输过程中由于寄存器更新导致的潜在问题,如数据传输的意外中断或数据损坏。

- 突发请求后的单个请求限制:

当PL外设发送一个突发请求后,它必须等待DMAC确认该突发请求已经完成,才能发送下一个单个请求。这是为了确保DMAC能够按顺序处理请求,避免数据冲突或丢失。如果PL外设在DMAC完成突发请求之前就发送了单个请求,可能会导致数据传输的混乱或错误。

DMAWFP指令是用于当程序线程需要暂停执行,直到可编程逻辑(PL)外设请求接口接收到任何类型的请求时。

如果请求FIFO中的头条目请求类型为:

-

Single(单个请求):如果请求FIFO中的头条请求是单个请求,DMAC将从FIFO中弹出该条目,并继续程序执行。这意味着DMA控制器已经识别并处理了该单个请求,因此程序可以继续进行其他操作或等待下一个请求。

-

Burst(突发请求):如果请求FIFO中的头条请求是突发请求,DMAC将不会从FIFO中弹出该条目,而是继续程序执行。这是因为突发请求通常涉及多个连续的数据传输,可能需要一些时间来完成。DMAC可能会开始处理这个突发请求,但程序线程不需要等待整个突发请求完成,可以继续执行其他任务。一旦突发请求完成,DMAC会更新状态或发送中断,以通知程序线程该请求已完成。

使用DMAWFP指令的目的是允许程序线程在等待PL外设请求时进入休眠或低功耗状态,从而提高系统的整体效率。当请求到达时,DMAC会唤醒程序线程并继续执行后续操作。这种机制允许实现更高效的数据传输和资源管理。

注意:突发请求条目保留在请求FIFO中,直到DMAC执行DMAWFP突发指令或DMAFLUSHP指令。

当程序线程需要暂停执行,直到可编程逻辑(PL)外设请求接口接收到一个突发请求时,应该使用DMAWFP burst指令。

如果请求FIFO中的头条目请求类型为:

基于你给出的描述,这里是对DMA控制器(DMAC)处理FIFO中不同请求类型的行为解释:

- Single(单个请求):当请求FIFO中的头条请求是单个请求时,DMAC会移除这个请求条目从FIFO中。但是,尽管请求已经被处理(从FIFO中移除),程序执行仍然保持挂起(halted)状态。

- Burst(突发请求):当请求FIFO中的头条请求是突发请求时,DMAC会弹出(pop)这个请求条目从FIFO中,并开始处理这个突发请求。一旦突发请求开始被处理,程序执行会继续进行。这是因为DMAC已经接收到了它期望的突发请求类型,所以可以安全地继续执行其他任务或开始处理与这个突发请求相关的后续操作。

DMALDP 指令是用于当DMAC完成AXI读事务后,向可编程逻辑外设发送确认信号的指令。相似的是,DMASTP 指令是在DMAC完成AXI写事务后,用于向可编程逻辑外设发送确认信号的指令。DMA{3:0}_DATYPE[1:0]总线是用于DMAC向可编程逻辑外设发送事务完成确认信号的机制之一。

当rvalid和rlast为高时,DMAC发送读取事务的确认,当bvalid为高时,发送写入事务的确认。当系统具有缓冲AXI写事务的能力时,DMAC可能会在写数据到达最终目的地之前向可编程逻辑外设发送一个确认信号。告知写事务已经被接收并开始处理。然而,此时写数据可能仍然停留在AXI Slave的内部缓冲区中,尚未被写入最终目的地。

DMAFLUSHP指令是用于重置PL外设请求接口的请求FIFO的。当DMAC执行DMAFLUSHP指令后,它会忽略来自PL外设的请求,直到PL外设确认了这个刷新请求。这个过程允许DMAC和PL外设之间进行同步。

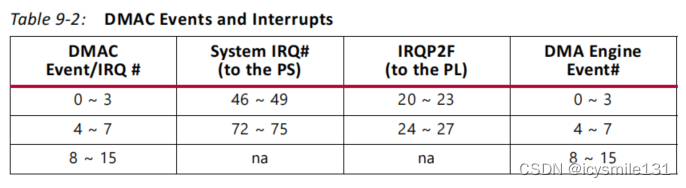

事件和中断

DMAC支持16个事件,其中前8个事件可以作为中断信号(IRQs [7:0])输出。这些中断信号可以同时发送到处理器系统(PS)的中断控制器和可编程逻辑(PL)部分。DMAC内部使用这些事件来实现通道到通道(channel-to-channel)或管理器到通道(manager-to-channel)的交叉触发。例如,一个DMA通道完成数据传输后,它可以触发一个事件,该事件可以被另一个DMA通道或DMAC的管理器捕获,以开始新的数据传输或执行其他任务。

表9-2展示了事件和中断之间的映射。

DMASEV(DMA Set Event)指令用于触发DMAC中指定的事件/中断资源。这个资源既可以被配置为事件(event),也可以被配置为中断(interrupt),这取决于INTEN(Interrupt Enable)寄存器的设置。

- 事件(Event)模式 :如果

INTEN寄存器将特定的事件/中断资源配置为事件模式,当DMAC执行DMASEV指令时,它会为指定的资源生成一个事件。当DMAC执行DMAWFE(DMA Wait For Event)指令并等待该事件资源时,如果事件已经被触发(即之前通过DMASEV设置了该事件),那么DMAWFE指令会返回并继续执行后续代码,同时清除该事件。 - 中断(Interrupt)模式 :如果

INTEN寄存器将特定的事件/中断资源配置为中断模式,当DMAC执行DMASEV指令时,它会将对应的中断信号irq<event_num>置高,其中event_num是指定的事件资源的编号。要清除这个中断,用户必须向INTCLR(Interrupt Clear)寄存器写入相应的值。通常,写入与中断源相对应的位掩码可以清除对应的中断。

安全性

在DMAC从复位状态退出时,其安全性的配置由复位初始化接口信号的状态决定。具体地,这些信号配置的安全性涉及到以下几个方面:

- DMA管理器(DMA manager) :

- 通过SLCR(Security Level Change Register,安全级别更改寄存器)的

TZ_DMA_NS位来配置DMA管理器的安全性。 - 如果

TZ_DMA_NS位被设置为0,DMA管理器将工作在安全状态下,仅执行安全的取指。 - 如果

TZ_DMA_NS位被设置为1,DMA管理器将工作在非安全状态下,仅执行非安全的取指。

- 通过SLCR(Security Level Change Register,安全级别更改寄存器)的

- 事件/中断资源(Event/Interrupt resources) :

- 通过SLCR的

TZ_DMA_IRQ_NS位来配置事件/中断资源的安全性。 - 该位的具体配置决定了事件/中断资源是在安全状态下工作还是非安全状态下工作。

- 通过SLCR的

- PL外设请求接口(PL peripheral request interfaces) :

- 通过SLCR的

TZ_DMA_PERIPH_NS位来配置PL外设请求接口的安全性。 - 同样地,该位的具体配置决定了PL外设请求接口是在安全状态下工作还是非安全状态下工作。

- 通过SLCR的

当DMA管理器执行DMAGO(DMA Go)指令来启动一个DMA传输时,它会根据通道的配置来设置该通道的安全状态。如果通道被配置为非安全(ns位被设置),则它可以在非安全环境中访问;如果通道被配置为安全,则它只能在安全环境中访问。

DMA通道的动态非安全状态可以通过Channel Status寄存器中的CNS位来提供。这个位反映了DMA通道当前的安全状态:

- 如果CNS位被设置为0,表示DMA通道当前在安全状态下运行。

- 如果CNS位被设置为1,表示DMA通道当前在非安全状态下运行。

软件可以通过读取这个CNS位来确定DMA通道的安全状态,从而采取相应的措施来保护数据或控制DMA传输的行为。