在写代码的工程中由于还没写完顶层模块或管脚约束无法综合完整工程查看资源消耗。可通过以下方式查看单独某个部分模块的资源消耗。

在TCL命令行中输入需要查看资源的模块命令:(可以不使用-part xc7z020clg484-1部分)

tcl

synth_design -mode out_of_context -top array_cmd_top -part xc7z020clg484-1-mode out_of_context:忽略 IO 约束和物理限制-top:指定目标模块

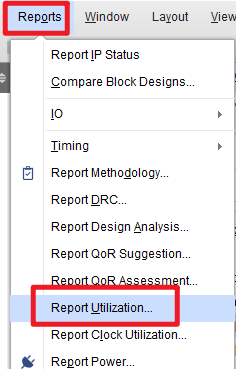

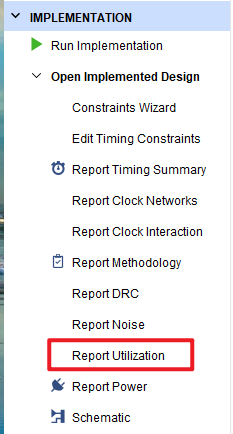

完成综合后点击左上角Reports-Report Utilization即可查看资源消耗情况或者在左侧的Flow Navigator中Open Implemented Design中的Report Utilization。

Reports-Report Utilization:

Open Implemented Design中的Report Utilization:

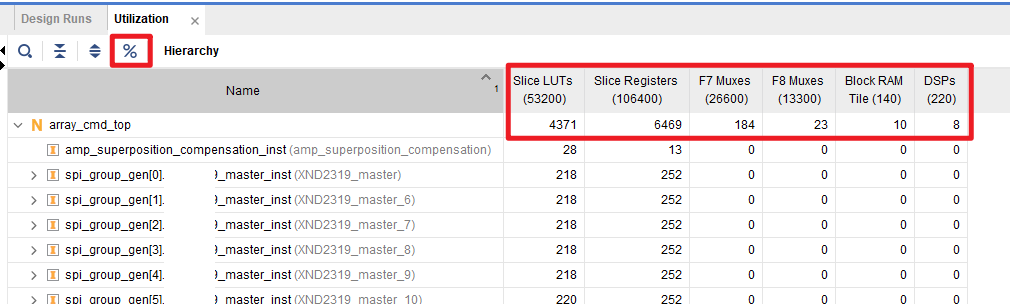

资源消耗情况。点击百分比符号可查看百分比消耗。