目录

-

- [1 概述](#1 概述)

- [2 参考文档](#2 参考文档)

- [3 查看方式](#3 查看方式)

- 4查询总结:

1 概述

本文用于介绍如何查看xilinx fpga GTX得位置信息(如X0Y0在哪个BANK/Quad)。

2 参考文档

《ug476_7Series_Transceivers》

《pg156-ultrascale-pcie-gen3-en-us-4.4》

3 查看方式

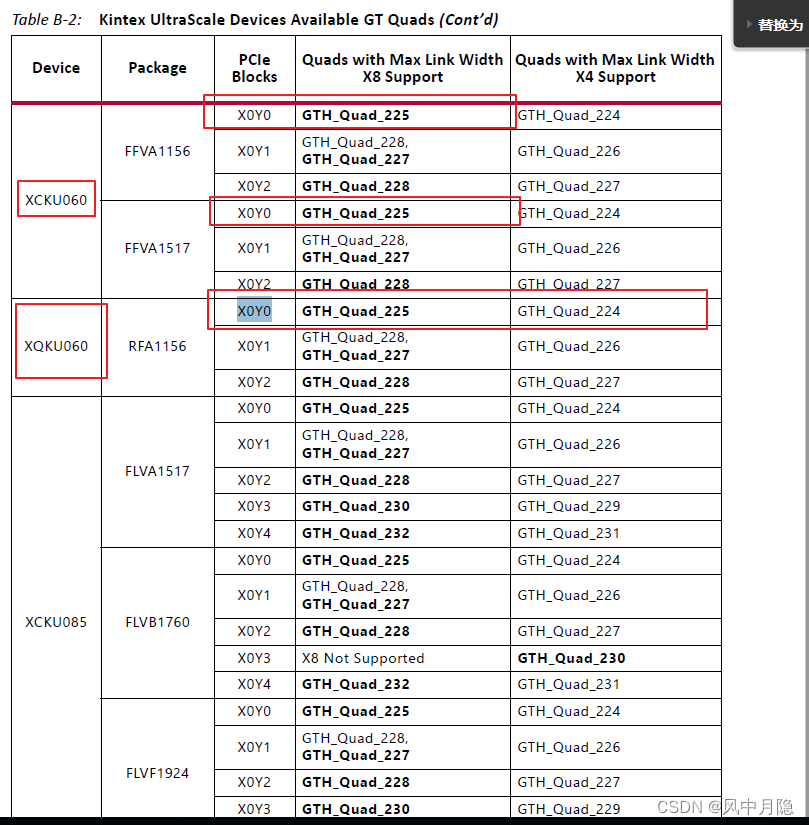

通过这两个文档可以自行查寻。比如如下查询结果中PCIE blocks 的x0y0在GTX的哪个quad。

4查询总结:

1) 不同的FPGA的X0Y0在GTX的bank/Quad不一定一样需要根据具体情况筛选;

2) 可以确定一点X0Y0一定在第一个GTX上;