首先科普一下

什么是bitstream文件

FPGA比特流(bitstream)是一种用于配置可编程逻辑器件的数据格式,特别是现场可编程门阵列(FPGA)。比特流包含了硬件逻辑电路、路由信息以及芯片上寄存器和存储器(如查找表LUT)的初始值。通常认为比特流具有厂商特定的格式,因此很难反向工程或理解其内部细节。然而,这种观点并不完全正确。

比特流文件不仅仅是一串配置FPGA的位数据,它还包含了一些人类可读的信息字段,用来描述这些位数据。实际上,比特流有一种类似汇编语言的指令集,用以描述FPGA的配置过程。从高层次上看,比特流文件类似于一个可执行程序。与ELF格式的可执行文件类似,比特流也有自己的文件格式来描述内容,而这种格式是公开的,因此可以分析比特流文件的内容,理解配置FPGA的具体步骤。

然而,比特流中未公开的部分在于位映射------即配置位的具体格式,尤其是比特流中的位如何映射到芯片上的具体LUT、连线等资源。可以将此比作,虽然汇编指令能够让你理解某段代码是在进行寄存器上的加法操作,但指令本身并没有明确指出是哪些寄存器参与了运算。

对于大多数FPGA用户而言,了解比特流的内部结构并非必要。只有当你要进行比特流回读、抢占调度或是类似的高级应用时,才需要深入理解比特流的工作原理和格式。例如,在进行比特流回读时,你可能需要验证配置是否正确;在抢占调度中,你可能需要在运行时动态地改变FPGA的部分配置而不影响其余部分的正常工作。

配置文件的格式

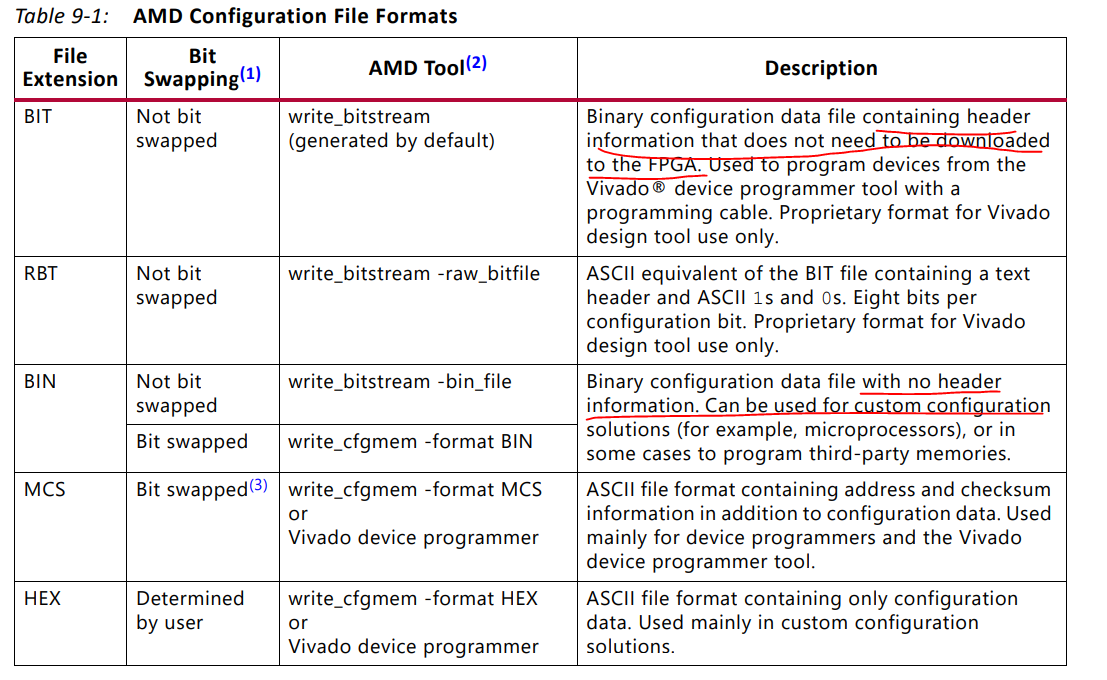

UG580 ,可以看到BIN文件相对BIT文件就是少了文件头信息。

参考

https://support.xilinx.com/s/article/14468?language=en_US

http://lastweek.io/fpga/bitstream/

有些开源工程在详细的研究如何去解密bit文件,分析FPGA电路结构,对我们理解bit文件的结构很有价值

bitstream文件结构

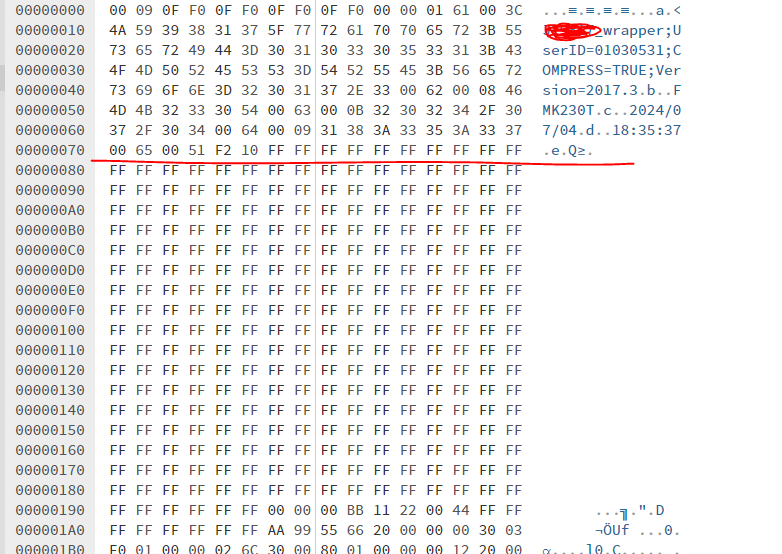

如下图所示,0x00-0x80地址区间为文件描述信息,描述该文件对应的器件型号、生成时间等等。

bitstream 可以直接烧录到FLASH吗?

答案是可以,将bit文件重命名为bin文件即可。但是前面不是说bit相对于bin 没有文件头信息吗?也就是说常规烧录到FLASH的bin文件相对于bit要小一些,按道理应该不可以才对,但实际上可以的,为什么呢?

FPGA配置过程SYNC

看一下FPGA的配置过程,尤其是sync 这个步骤。

必须向配置逻辑发送一个特殊的32位同步字(0xAA995566)。这个同步字通知设备即将接收配置数据,并将配置数据与内部配置逻辑对齐。除了总线宽度自动检测序列之外,在同步之前出现在配置输入引脚上的任何数据都将被忽略。 (所以这里即使烧录的文件多了文件头信息也会被忽略掉,这样即使你烧录的是bit文件也是可以的)

在FPGA配置过程中,这个32位的同步字起到关键作用,它标志着配置数据流的开始。配置逻辑在接收到这个特定的同步字后,会准备接收并处理随后到来的比特流数据。这是因为在配置过程中,FPGA的配置逻辑需要知道何时数据流真正开始,以正确地捕获和解释配置信息。如果没有正确的同步,FPGA可能会错误地解析配置数据,导致配置失败或者不正确的功能实现。

总线宽度自动检测序列是一个例外,因为它发生在同步字之前,用于确定配置接口的总线宽度,从而确保后续的数据传输能够正确进行。一旦同步字被识别,FPGA就会根据已知的总线宽度开始接收和解码配置比特流。

https://docs.amd.com/v/u/en-US/ug570-ultrascale-configuration

推荐个小工具 https://hexed.it/ ,如果需要查看bit或者bin的二进制文件,可以在线查看,比较方便