有比(ratioed)反相器:在输出低电平时,驱动管和负载管同时导通,其输岀低电平由驱动管的导通电阻和负载管的等效电阻的分压决定。为了保持足够低的低电平,两个等效电阻应保持一定的比值。

无比(ratioless)反相器在输出低电平时, 只有驱动管导通,负载管是截止的,在 理想情况下, 其输出低电平等于零。

上方只考荧光

静态CMOS反相器---透视(Perspective):

输出高电平和低电平分别为 V D D V_{DD} VDD和GND。换言之,电压摆幅(logicor signal swing, V s w V_{sw} Vsw)等于电源电压,因此噪声容限很大。

逻辑电平与器件的相对尺寸无关,所以晶体管可以采用最小尺寸。具有这一特点的门称为无比(ratioless)逻辑。它不同于有比(ratioed)逻辑, 在有比逻辑中逻辑电平是由组成逻辑的晶体管的相对尺寸来决定的。

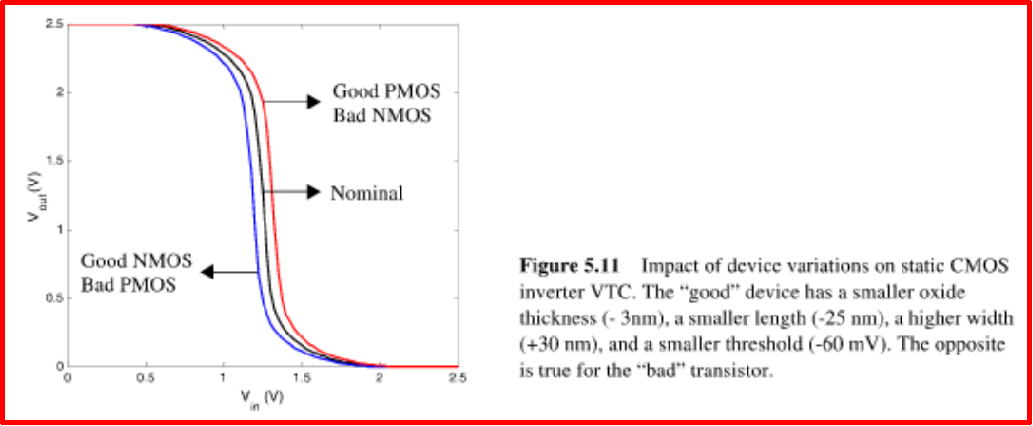

稳定性评估---静态特性---不对称VM:

稳定性评估---静态特性---VTC与VDD的关系:

为了能达到足够的增益以用于数字电路,必须使电源至少等于热电势(室温时为25 mV)的两倍。

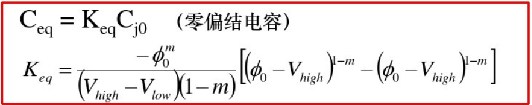

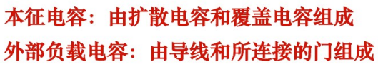

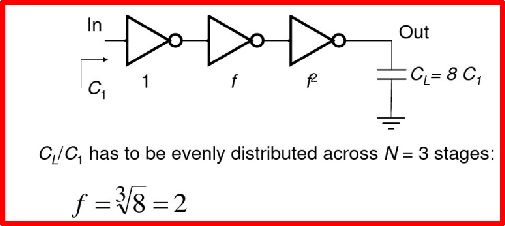

动态特性(The Dynamic Behavior)---计算电容值(Computing the Capacitances):

动态特性(The Dynamic Behavior)---延时(Propagation Delay):

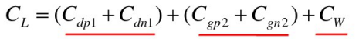

用以下方式可以减小一个门的传播延时:(简答)

1.减小负载电容CL:门本身的内部扩散电容、互连线电容和扇出电容。(细致的版图设计有助于减少扩散电容和互连线电容。优秀的设计要求漏扩散区的面积越小越好。)

2.增加晶体管的W/L比:这是设计者手中最有力和最有效的性能优化工具。但是在采用这一 方法时要当心:增加晶体管尺寸也增加扩散电容,因而增加了 CL;事实上,一旦本征电容 (即扩散电容)开始超过由连线和扇出形成的外部负载,增加门的尺寸就不再对减少延时有帮助。它只是加大了门的面积,这称为自载效应。此外,较宽的晶体管具有较大的栅电容,这就增加了驱动门的扇出系数,从而又反过来影响它的速度。

3.提高Vdd。如图所示,一个门的延时可以通过改变电源电压来调整。这一灵活性使设计者可以用能量损耗来换取性能。然而,增加电源电压超过一定程度后改善就会非常有限,因而应当避免,同时对可靠性方面的考虑(氧化层的击穿,热电子效应)也迫使在深亚微米工艺中对电源电压要规定严格的上限

只考填空

考虑两个完全相同的CMOS反相器相串联,第一个门的负载电容可近似为:

我们建立一个起上式中的各种参数和尺寸系数S之间的关系。尺寸系数S把反相器的晶体管尺寸与一个最小尺寸的反相器的晶体管尺寸联系起来。本征电容 C i n t C_{int} Cint如包括扩散电容及密勒电容, 它们都正比于晶体管的宽度。因此, C i n t = C_\mathrm{int}= Cint=S • C i r e f • C_{iref} •Ciref。门的电阻与参考门的关系为 R e q = R τ e f / R_\mathrm{eq}= \mathbf{R} _\mathrm{\tau ef}/ Req=Rτef/S。

功耗(Power),能量(Energy)---动态功耗 p d y n p_{dyn} pdyn:

通过观察得出:在由低至高翻转期间CL被充以电荷 C L • V D D \mathbf{C}\mathrm{L}•\mathbf{V}\mathrm{DD} CL•VDD。提供这些电荷需要从电源得到等于 C L ⋅ V D D 2 ( = Q × V D D ) \mathbf{C} _{\mathrm{L} }\cdot \mathbf{V} {\mathrm{DD}}^{2}( = \mathbf{Q} \times \mathbf{V} {\mathrm{DD}}) CL⋅VDD2(=Q×VDD) 的能量。存放在电容中的能量等于 C L ⋅ V D D 2 / 2 C_L·V^2{DD} /2 CL⋅VDD2/2。这意味着由电源提供的能量只有一半是存放在CL上的,另一半则由PMOS管消耗了。注意,这一能耗与PMOS 器件的尺寸(因而也与电阻)无关!在放电阶段,电荷从电容上移去,因此它的能量消耗在NMOS 器件中。同样,这一能耗与NMOS器件的尺寸无关。总之, 每一个开关周期(由L-H和H-L翻转组成)都需要一个固定数量的能量,即 C L ⋅ V D D 2 CL·V^2{DD} CL⋅VDD2°

减小电源电压VDD

减小实际电容或翻转活动性f0→1:由于在一个组合逻辑电路中大部分的电容是晶体管电容(栅电容和扩散电容),因此在进行低功耗设计时保持这部分电容最小是有意义的。这意味着应当保持晶体管有尽可能或合理的最小尺寸。但这无疑会影响电路性能,但这 一影响可以通过逻辑或结构上的加速技术来弥补。晶体管尺寸应当放大的惟一情形是当负载电容由外部电容(如扇出或导线电容)占主导地位的时候

改变器件尺寸并降低电源电压是减小一个逻辑电路能耗的非常有效的方法。对于具有较大等效扇出的电路尤为如此,因为在这些电路中可以达到几乎十倍的能量减少。

结论:使输出的上升/下降时间大于输入的上升/下降时间可以使短路功耗减到最小,但输出的上升/下降时间太大会降低电路的速度并在扇出门中引起短路电流。这个例子很好地说明了只顾局部优化而不管全局是如何会引起不良后果的。

当负载电容太小时,功耗主要来自短路电流。对于非常大的负载电容值,所有的功耗都用来充电和放电负载电容。

charging and discharging the load Capacitance.

功耗-延时积(PDP):单位是焦耳,所以PDP是能量的衡量,是一个逻辑门的质量评定指标。

静态CMOS反相器把一个上拉的PMOS器件和一个下拉的NMOS器件组合在一起。

因为 PMOS具有较低的电流驱动能力,通常应使它比NMOS宽。

该门具有几乎理想的电压传输特性。逻辑摆幅等于电源电压并且与晶体管的尺寸无关。一 个对称反相器(它的PMOS和NMOS管具有相同的电流驱动强度)的噪声容限接近Vdd/2。稳态响应不受扇出的影响

它的传播延时主要由充放电负载电容 C L C_L CL所需要的时间决定。作为一阶近似,它可以近似为:t = 0.69 C L =0.69C_{\mathrm{L}} =0.69CL (Re q n + R e q p ) / 2 qn+ R_\mathrm{eqp}) / 2 qn+Reqp)/2。使负载电容保持较小是实现高性能电路的最有效手段。只要延时主要受扇出和导线等外部(或负载)电容的影响,改变晶体管的尺寸就可能有助于提高性能。

功耗主要是由在充电和放电负载电容时消耗的动态功耗决定的,它等于 C L V d d f C_LV_{dd}f CLVddf

使工艺尺寸变小是减少一个门的面积、传播延时以及功耗的有效手段。如果电源电压也同时降低,则其影响甚至更为惊人。