本次分享论文:RO-SVD: A Reconfigurable Hardware Copyright Protection Framework for AIGC Applications

基本信息

**原文作者:**Zhuoheng Ran, Muhammad A.A. Abdelgawad, Zekai Zhang, Ray C.C. Cheung, Hong Yan

**作者单位:**香港城市大学电气工程系及智能多维数据分析中心

**关键词:**AI生成内容,版权保护,奇异值分解(SVD),区块链,纳米制造,AI安全,低功耗AI

**原文链接:**https://arxiv.org/abs/2406.11536

**开源代码:**暂无

论文要点

论文简介:

随着生成式人工智能(GenAI)的广泛应用,迫切需要一种安全高效的机制来管理和传播AI生成的多维数据。

本文提出了一个基于区块链的版权追溯框架,称为环形振荡器-奇异值分解(RO-SVD),该框架利用硬件熵源生成的低秩矩阵,在设备层面实现AI生成内容(AIGC)的版权追溯。

通过现场可编程门阵列(FPGA)的并行性和可重构性,RO-SVD框架可以在现有AI加速设备上轻松构建,并提供低成本的解决方案。研究者开发了一个软硬件协同设计原型,展示了其在AI生成图像版权追溯中的有效性和高效性,这是首个针对AIGC版权追溯问题的实用硬件研究。

研究目的:

本文旨在解决随着生成式人工智能(GenAI)技术的广泛应用而带来的AI生成内容(AIGC)版权问题。AIGC的创建过程包括数据、算法和加速计算三个关键组成部分,现场可编程门阵列(FPGA)被认为是一种可重构且低功耗的AI计算解决方案。研究者提出了一种基于区块链的版权追溯框架RO-SVD,利用硬件熵源生成的低秩矩阵,并通过FPGA的并行性和可重构性来实现低成本、高效的AIGC版权追溯机制。

研究贡献:

-

硬件熵源矩阵的低秩特性:研究者证明了由于工艺变化,硬件熵源生成的矩阵响应具有近似低秩特性,为设备层面的AIGC版权追溯提供了可能。

-

提出RO-SVD框架:在此基础上,研究者提出了一个名为RO-SVD的框架,该框架基于区块链实现AIGC的自动高效标记和管理。

-

引入奇异值分解(SVD):研究者首次将SVD作为一种强大的计算组件,引入到FPGA生成的矩阵基础原语中,作为物理不可克隆函数(PUF)和真随机数生成器(TRNG)的协同设计,用于大规模内容管理和标记。

-

开发软硬件协同设计原型:研究者开发了一个可以轻松构建在现有设备上的软硬件协同设计原型,体现了研究者工作的原则。

引言

生成式人工智能(GenAI)的普及,如ChatGPT、Midjourney和Sora,推动了创意产业的发展,同时引发了对AI生成内容(AIGC)版权问题的关注。AIGC的生成涉及数据、算法和加速计算三大要素,现场可编程门阵列(FPGA)作为可重构、低功耗的AI计算解决方案,不仅支持高效计算,还能部署安全功能。区块链技术因其高效的管理和交易能力,被认为是保护AIGC版权的有效策略。然而,针对AIGC版权保护的实用实现面临工程挑战。

本文提出了基于区块链的环形振荡器-奇异值分解(RO-SVD)框架,以解决AIGC版权保护中的效率、成本和可重构性问题,提供一种创新且低成本的解决方案。

研究背景

在AI生成内容(AIGC)的合法使用中,强大的知识产权保护方案至关重要。现有方案如元数据跟踪容易被修改,通常与水印技术结合使用。区块链技术由于其透明和不可更改的特点,被认为是一种有效的AIGC版权管理工具。通过利用硬件熵源的不可预测性,结合区块链技术,每个数字资产可以分配一个唯一且不可克隆的身份,在区块链和物联网生态系统中进行追溯。然而,针对AIGC版权保护的实用实现仍然面临工程挑战。

计算架构

研究者引入奇异值分解(SVD)技术,将硬件熵源生成的矩阵分解,提取奇异值及其对应向量用于认证和随机数生成。数据流处理包括预处理比特流、认证和随机比特流及单色比特流的生成和处理。

**·**在预处理阶段,FPGA生成初始矩阵并通过截断奇异值分解(TSVD)提取认证矩阵并存储在区块链中。

**·**在认证和随机比特流阶段,处理生成的矩阵分别用于认证和随机用途。

**·**在单色比特流阶段,通过最不重要位(LSB)技术,将认证和随机矩阵嵌入图像中,确保图像完整性和版权追溯性。

整个过程强调高效性和可重构性,为AIGC版权追溯提供了技术基础。

硬件实现

研究者利用环形振荡器(RO)设计了真随机数生成器(TRNG)和物理不可克隆函数(PUF),用于生成高熵随机数和设备特定标识符。他们减少了设计约束,专注于从熵源生成的矩阵中提取认证和随机种子。通过使用Vivado HLS基于Jacobi方法构建奇异值分解(SVD)硬件模块,研究者集成了AXI协议,支持浮点格式的输入和输出矩阵。

此外,研究者创建了基于AXI4-Lite协议的新IP核,使可编程逻辑(PL)能够作为主设备进行并行操作,并通过高性能AXI HP接口进行数据传输,提高了性能并减少了CPU负载。在区块链应用方面,研究者通过最不重要位(LSB)技术将无损图像嵌入到系统中,实现所有权声明并确保图像与设备的关联。

研究结果

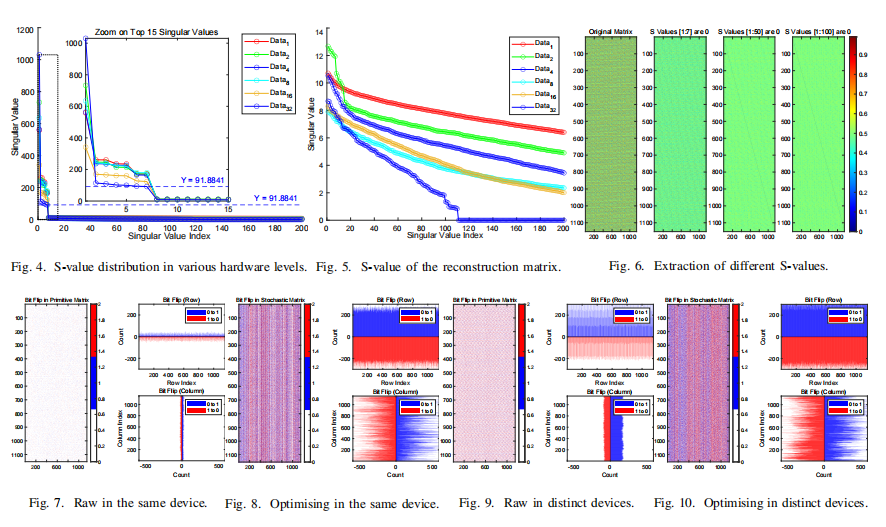

研究者在数百个PYNQ-Z2板上进行了硬件实验,使用VHDL和Vivado HLS实现了RO-SVD设计。通过模拟和分析环形振荡器(RO)的频率模式和特征变化,验证了硬件熵源生成响应中的固有模式和随机模式。研究者展示了不同硬件级别上生成的矩阵奇异值分布,证明了去除前七个奇异值进行重建的合理性。

认证测试表明,该方法在相同设备条件下能生成一致的不变哈希值。通过比较随机种子在列内的平均汉明距离,验证了该方法能有效地从生成端挖掘随机性。研究者简化了Xilinx约束设计,增强了设计的可重构性并减少了开发时间。生成的种子通过了NIST SP 800-22 Rev.1随机性测试,证明了其随机性优于原始方法。

论文结论

本文提出了一个基于区块链的环形振荡器-奇异值分解(RO-SVD)框架,首次在硬件层面实现了AI生成内容(AIGC)的版权追溯。通过软硬件协同设计,研究者展示了该框架在FPGA加速设备上的高效性和实用性。RO-SVD框架利用硬件熵源和奇异值分解技术,实现了AIGC的高效标记和管理。

实验结果表明,该框架能够生成一致的不变哈希值,有效挖掘随机性,并增强设计的可重构性。未来工作将致力于提高各组件的计算效率,进一步提升整体设计的性能,以应对不断增长的AIGC版权保护需求。

原作者:论文解读智能体

校对:小椰风