基于AM62x+FPGA的电力低压保护主控板解决方案

|---------------|---------------------------------------------------------------------|

| Specification | Description |

| 处理器 | AM6231 at up to 1.2GHz |

| 操作系统 | VXWORKS |

| 存储 | DDR4,8GB EMMC |

| 接口 | •1路10/100Mbps ETH •1个USB2.0 •6路KEYPAD 输入 •1路RS485 •1路IRIGB •1路RS232 |

| 调试接口 | JTAG / COP debug port |

0 引言

伴随着工业用户对供电可靠性的要求,数字式保护测控装置在工业用户中的应用也越来越广泛。目前市场上的低压综保装置是基于DSP和MCU双 CPU 架构,其中DSP负责逻辑功能计算,单片机负责界面显示及键盘输入。随着IT技术的不断进步,这种架构相对来说性能较低,液晶界面操作不够流畅,DSP 采样数据处理能力也相对较弱,对于集成保护测控工能来说性能已经没有优势。 CPU 和 DSP之间大多数采用串口通信方式,无数据总线,传输可靠性较低,且不利于插件和功能的扩展。 因此需要一种高性能的采集平台,解决高速数据传输、大容量数据采样、保护算法和数据采样同步等问题 。

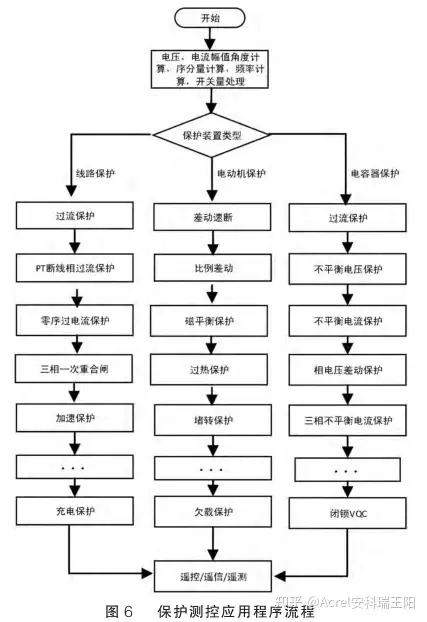

针对上述情况,本文提出一种FPGA+DSP+CPU 的架构,其中CPU和DSP之间通过 FPGA 为桥梁传递数据,保证了数据传输的稳定和可靠。其中FPGA用于低压综保装置的模拟量采集传输,将采集的数据送给 DSP 进行保护的启动及逻辑运算;CAN总线用于开关量采集、直流量采集和 CPU 管理数据通道。

1 装置的整体架构

装置的整体架构如图1所示,系统采用了两条高速数据总线和两条 CAN 总线。高速总线通信用于传输模拟量采集等大数据量的,采用数据总线的方式,便于插件和系统的扩展,其采用LVDS 差分电路,能够共模干扰信号,提高装置的抗干扰能力。CAN 总线用来传输开入开出、4~20mA直流信号、PT100 温度等数据,用于DSP 和CPU之间的数据传输, 同时CPU 对其他智能插件的管理命令和报文交互也是通过CAN总线实现的。CPU负责处理人机接口功能,实现装置的界面显示、定值整定、事件查看、事件记录、故障录波、对时及网络通信服务。 整个系统设计采用了高速数据总线和 CAN 总线的冗余结构,保证了系统的安全稳定和数据传输的可靠性。 FPGA 强大的数据处理能力,承担了基础数据交换和处理工作,为装置的报文、事件等提供了时标,同时降低了CPU 和 DSP的工作任务,DSP仅用于完成保护的采样值计算和逻辑功能处理,保证了功能划分的独立性和保护逻辑处理的实时性;CPU 用于人机接口、界面显示、通讯和时钟处理等任务,同时用来管理其他扩展智能插件,保证了系统的可扩展性。

2 装置的硬件设计

低压综保装置集成了线路保护功能、电动机保护功能、电容器保护功能;装置需要完成电流电压的模拟量信号的采集,用于参与逻辑运算的开关量、直流信号及温度传感器温度信号的采集,装置需要通过开出回路来完成断路器的跳闸功能。

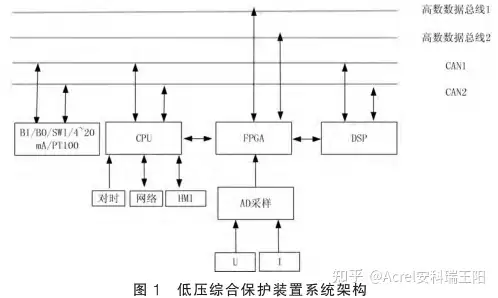

采样通道一般是将电流和电压信号,通过AC转换成为小电压信号,经背板送给ADC ,通过低通滤波回路,滤掉高次谐波干扰,再经过 AD 采样,将模拟量转换为数据量,送给 FPGA处理,FPGA 将从高速数据总线上获得的采样信号,进行同步处理,然后传输给DSP芯片进行采样运算和逻辑处理,完成装置保护逻辑的实现,同时通过 FPGA将计算的结果送给CPU,用于事件记录、录波存储、LCD显示等功能。采样回路需要考虑AC的二次断线后,AD 芯片采样有直流偏置的处理,装置采用了下拉电阻的方式来减少直流偏置电压,避免了装置因为 AC二次断线引起直流偏置过大,而产生采样异常告警。

模拟量采集处理过程如图 2 所示。

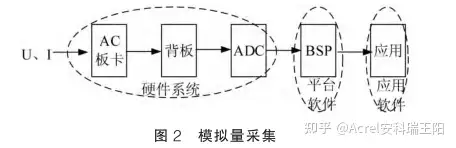

开关量采集回路,在电路设计的过程中,兼容 DC/AC220V、DC110V、DC24V的采集 ,DC220V、DC110V 和DC24V的采集,一般的处理是通过分压电阻的实现的,这种实现方式需要采用不同的 BOM 或者使用跳线帽选择采集回路电阻。不同的BOM 需要订货的时候,进行选择说明,跳线帽的方式需要拔插插件完成跳线选择,均有一定的弊端。本装置设计上采用了自适应原理,可以做到自适应,采用定值整定的方式,实现 DC/AC220V 和 DC110V 的采集,便于工程实施。

开关量采集处理过程如图 3 所示:

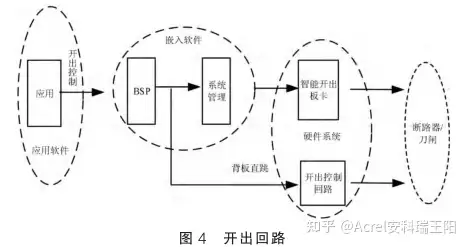

开出回路设计,开出回路输出分为两种,一种是逻辑计算输出的跳闸信号,一种是通过应用后台给出的分合闸命令,这两种输出的处理模式是不同的,应用后台的遥控命令,经过 BSP 驱动和系统管理模块,驱动智能开出板卡的输出回路,从而实现对刀闸断路器等操作机构的控制。 保护逻辑输出的跳闸信号,则经过 BSP 后经过背板直接控制开出板卡的输出回路,以减少出口控制延时,开出回路设计如图 4 所示。

一键分/合闸功能设计,保护测控装置对断路器的控制一般都是采用后台软件或者装置界面的主接线图,对开关进行遥控,实现分合闸操作,本装置除了支持上述功能外,考虑其低压综保的应用场景,在装置上设计了一键分合闸的按键功能,通过装置的面板按钮实现一键分闸和一键合闸操作, 该功能相对后台的遥控功能来说更加的简洁方便, 为无后台应用场景提供了快捷方式的遥控分合闸操作。

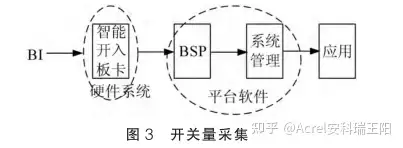

3 装置软件功能设计

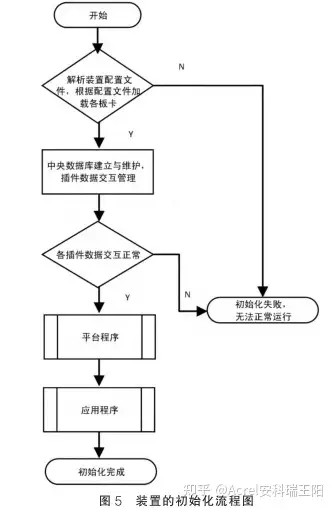

低压综保装置根据所以保护对象的不同,提供了不同了保护配置功能,不同对象其测控功能的作用是相同的,所以软件功能设计的时候,将测控功能的三个子模块,遥控功能,遥信功能和遥测功能作为了通用模块。对于电动机保护线路保护、电容器保护来说,保护对象不同保护功能模块也是不同的,装置通过保护类型定值可以选择当前装置是电动机保护装置、线路保护装置还是电容器保护装置,根据装置选择的类型,会相对应配置不同保护功能模块、定值清单、软压板、硬压板及控制字,在集成了多种保护功能的同时,考虑工程实施的便利性,通过定值整定的方式,选择保护装置的保护功能。装置的初始化过程如图 5 所示:

其中平台程序,包括实时模块、LCD模块、通讯模块、对时模块、打印模块、装置调试模块等。应用程序是装置保护测控功能的实现模块,针对低压综保装置,又根据装置类型的不同,有着不用的应用功能。保护测控功能流程如图 6 所示。