十六进制计数器

描述

请用Verilog设计十六进制递增计数器电路,每个时钟周期递增1。

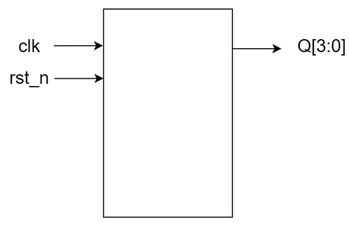

电路的接口如下图所示。Q[3:0]中,Q[3]是高位。

接口电路图如下:

输入描述:

input clk ,

input rst_n ,

输出描述:

output reg [3:0] Q

代码如下

cpp

`timescale 1ns/1ns

module counter_16(

input clk ,

input rst_n ,

output reg [3:0] Q

);

always @(posedge clk or negedge rst_n) begin

if (!rst_n) Q[3:0] = 4'b0000;

else Q[3:0] = Q[3:0] + 4'd1;

end

endmodulePS:该题还挺简单的。。。。。。