标准单元描述

标准单元主要由以下几个部分构成,分别是引脚电容、power、timing组成。其中引脚电容主要包含input/output pin的电容值。

power主要包含每个pin的leakage power和internal power。

timing主要包括cell的input pin到output pin的rise delay和fall delay。有需要了解cell delay是如何计算的小伙伴可以戳这里了解。

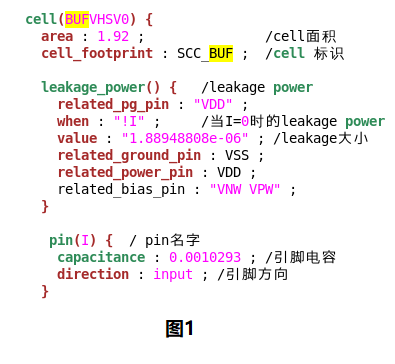

先看一下组合逻辑单元其lib是怎么构成的,以buffer为例。

图1定义了buffer的一些基本属性、 leakage power值和input pin的相关信息。

图2定义了buffer output pin的相关参数,即buffer Z端的功能和internal power相关信息。

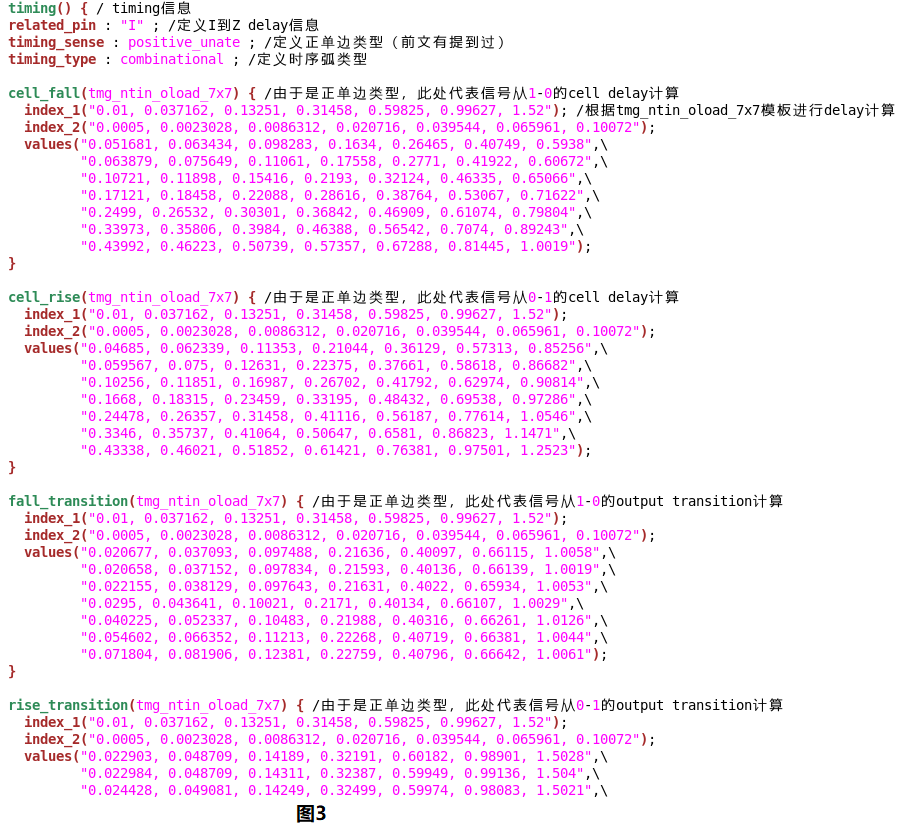

图3定义了buffer的timing信息。由于buffer属于组合逻辑,因此其timing arc属于combination timing arc。如图所示,定义了buffer output pin的rise/fall delay和rise/fall transition。

接下来,我们再看一下时序单元的timing arc是啥样的,以寄存器为例。

图4定义了寄存器的基本信息,以及其CK和D端的状态信息。

图5定义了D pin的相关信息和CK到Q的hold timing arc。

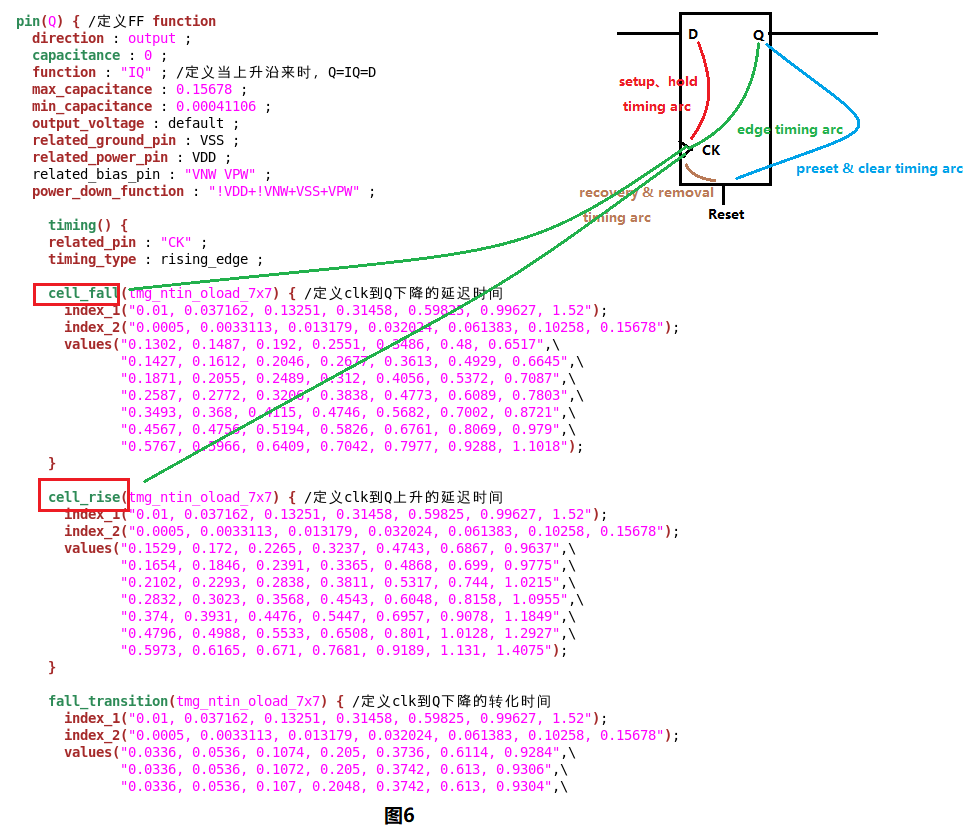

图6定义了Q端的功能及其CK到Q的timing arc。

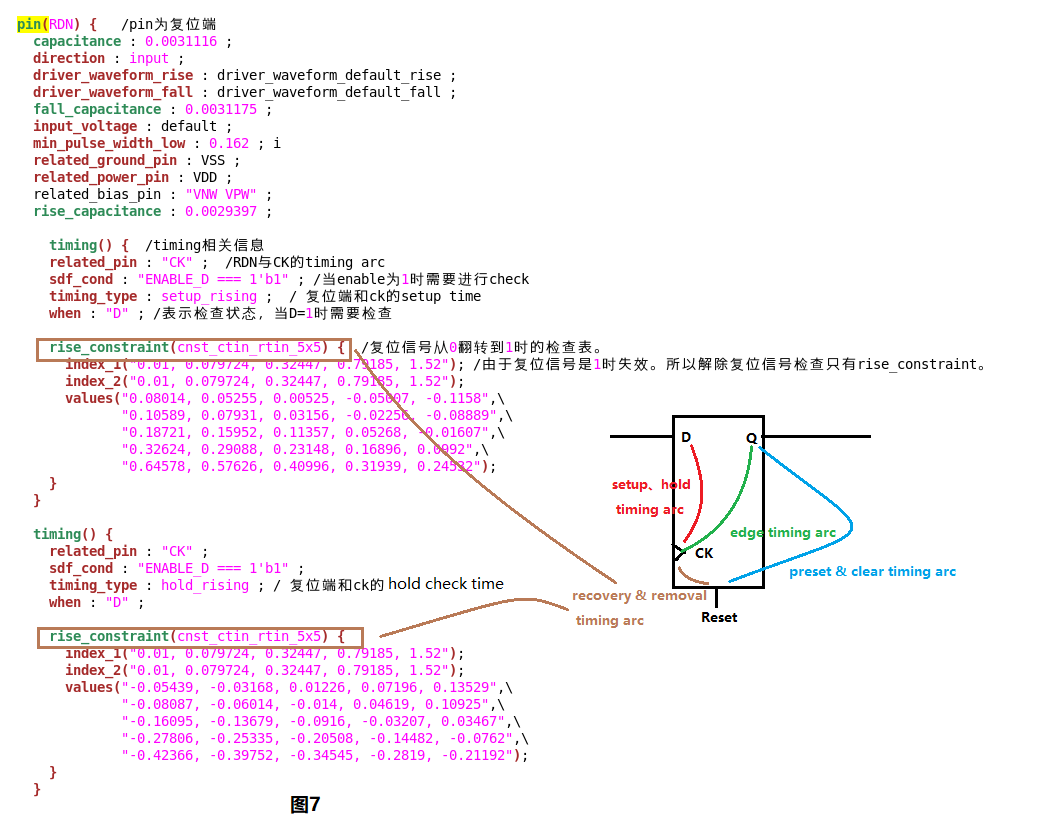

图7为寄存器的复位端和CK的timing arc。我们可以看到,其只有rise_constraint检查。这是因为解除复位信号是从0到1进行跳变。所以,其只有上升沿的timing检查。

#小编是一个入行多年的数字后端工程师,本身对编程方面比较感兴趣,在数字后端的脚本、flow上比较擅长,可以为大家提供答疑咨询服务。如有需求,可打开星球芯冰乐,获取更多知识干货分享与答疑服务。